哈工大数电打印 2.docx

哈工大数电打印 2.docx

- 文档编号:9901741

- 上传时间:2023-02-07

- 格式:DOCX

- 页数:23

- 大小:375.72KB

哈工大数电打印 2.docx

《哈工大数电打印 2.docx》由会员分享,可在线阅读,更多相关《哈工大数电打印 2.docx(23页珍藏版)》请在冰豆网上搜索。

哈工大数电打印2

二OOO年数字逻辑电路试题

一、回答下列各题(每小题5分,共25分)

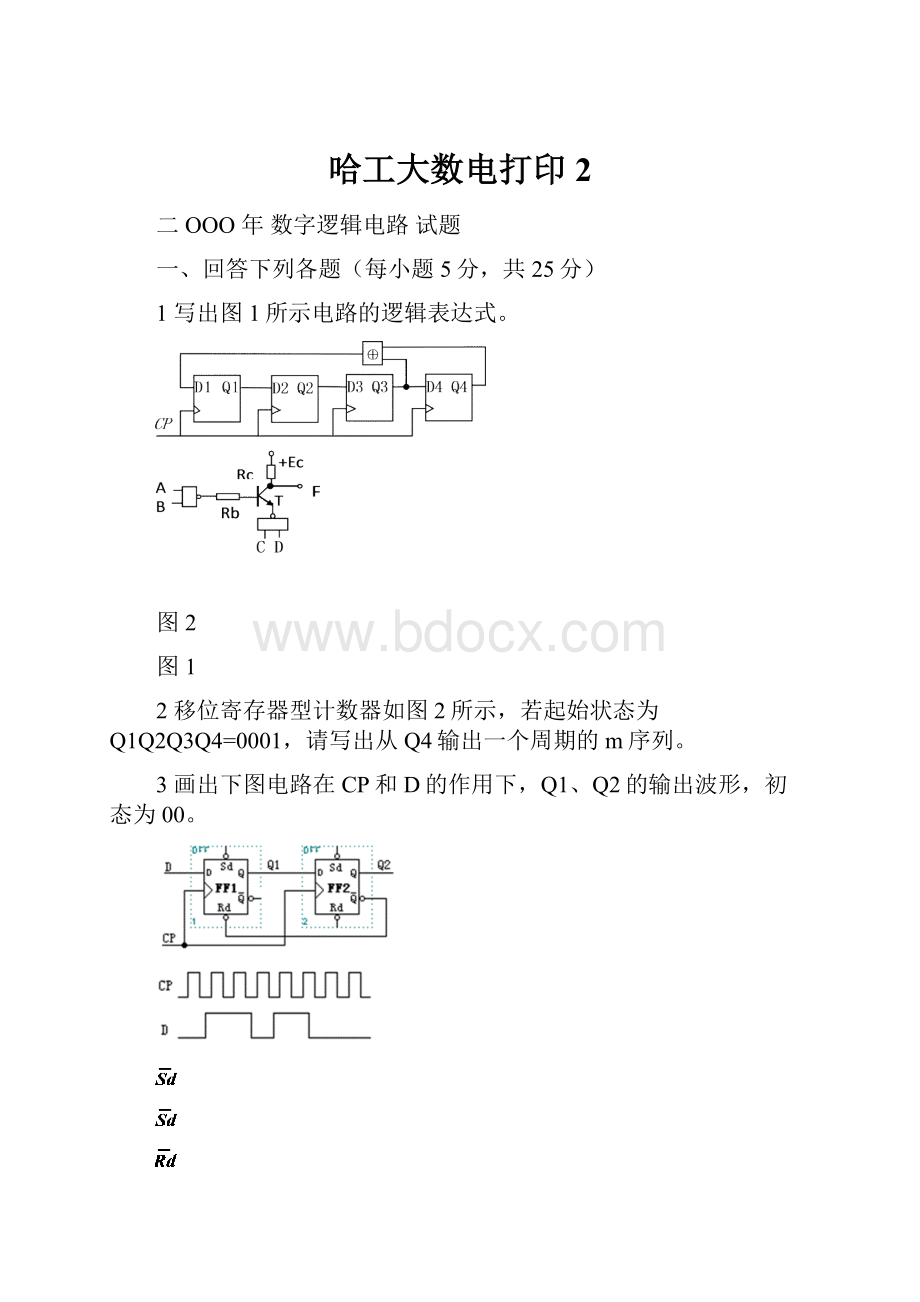

1写出图1所示电路的逻辑表达式。

图2

图1

2移位寄存器型计数器如图2所示,若起始状态为Q1Q2Q3Q4=0001,请写出从Q4输出一个周期的m序列。

3画出下图电路在CP和D的作用下,Q1、Q2的输出波形,初态为00。

二、由8选1数据选择器CT4151构成的电路如下图所示,请写出该电路输出函数Y的逻辑表达式,以最小项之和(Σm(┅,┅,))形式表示。

如果要实现逻辑函数Y=Σm(1,2,5,7,8,10,14,15),则图中接线应怎样改动?

(10分)

三、某大厅有一盏灯和分布在不同位置的四个开关(A、B、C、D)。

试利用四选一数据选择器为大厅设计一个电灯开关控制逻辑电路,使得人们可以在大厅的任何一个位置控制灯的亮或灭。

例如:

可以用A开关打开,然后用B(或C、D、A)开关熄灭。

(15分)

四、脉冲分配电路一般由计数器和译码电路组成,试用D触发器和与非门设计如图所示波形的脉冲分配器电路。

(15分)

五、试用JK触发器和门电路设计一自动售饮料机的时序控制电路。

其投币口每次只能投入一枚5角或1元的硬币,投入1.5元硬币后,自动售货机给出一瓶饮料。

如投入两元硬币,则在给出一瓶饮料的同时,退出一枚5角硬币。

(20分)

要求:

1状态设置合理,状态图标注清楚;

2画出逻辑电路图;

3检验自启动。

二OO一年数字逻辑电路试题

一、解答下列各题(每小题5分,共25分)

1.将D触发器转换成JK触发器,画出逻辑电路图。

2.试画出111序列检测器的状态图,当连续输入三个1时输出为1,否则输出为0。

3.

画出下图电路输出F的波形,并说明在不同输入(A,B,C)条件下,三态门G1输出端VO1的电压值。

4.

试用74161设计模7同步加法计数器。

5.画出下图电路CP和输出Q1Q2的波形图,说明Q1和Q2的关系。

二、2位并行A/D转换电路如图所示,输出为2位数字量B1B0,电压比较器输出为A2A1A0,在答题纸上完成表1,并设计A2A1A0到B1B0转换电路。

(8分)

表1

输入电压

A2A1A0

B1B0

Vi<1V

1V≤Vi<2V

2V≤Vi<3V

3V≤Vi<4V

三、由双四选一数据选择器74153构成的电路如图所示,请写出F的表达式,用最小项之和∑m的形式表示。

(10分)

74153功能表

E

A1A0

W

1

ⅹⅹ

0

0

00

D0

0

01

D1

0

10

D2

0

11

D3

四、计算机机房的上机控制电路的框图如下,图中DE为控制端,令上午、下午、晚上其取值分别为01、11、10;ABC为需上机的三个学生,其上机的优先顺序是,上午为ABC,下午为BCA,晚上为CAB;电路的输出F1F2F3为1时分别表示ABC能上机。

试用与非门设计该电路。

(20分)

五、利用JK触发器和门电路设计一个时序电路,用来控制红、绿两个发光二极管,要求红色管亮三个时钟周期,绿色管亮两个时钟周期,波形如图所示。

(20分)

二OO二年数字逻辑电路试题

一、解答下列各题(共34分)

1.某采集系统要求模数转换部分精度为0.5%。

应选多少位的模数转换器?

若用并行A/D,其中有多少个比较器?

并/串行有多少个比较器?

(5分)

2.两路同频方波信号,其相位差恒为90度,如图所示。

试设计一个检测电路判断A、B相位情况,当A超前B90度时,如图1-a所示,输出F为1;当B超前A90度时,如图1-b所示,输出F为0。

(5分)

3.某同步时序电路有一个输入和一个输出,当输入序列有奇数个1时输出为1,否则输出为0,试画出此同步时序电路的状态图。

(6分)

4.改正下图电路,并画出输出F和VO1的波形。

(6分)

5.试设计一个转换电路,当X=1时,将JK触发器转换成D触发器;当X=0时,将JK触发器转换成T触发器,画出逻辑电路图。

(6分)

6.试用两片74161设计一个模60加法计数器。

(6分)

74161功能表

CP

CTT

CTP

功能

φ

L

φ

φ

φ

异步清零

↑

H

L

φ

φ

置数

φ

H

H

L

H

保持

φ

H

H

H

L

保持

↑

H

H

H

H

计数

二、试分析下图电路,画状态转换图,并说明其工作原理。

其中:

Q2Q1为状态输出控制某程控放大器的增益,电路的三个状态(Q2Q1=00、01、10)分别对应10、20、40放大倍数,(11)状态为禁止态,X为控制输入,Y1、Y2为溢出指示。

(15分)

三、用双四选一数据选择器74153设计一个乘法器,用来完成两个两位二进制数的乘法运算(a1a0╳b1b0=P3P2P1P0)。

(15分)

74153功能表

A1A0

W

74153

1

ⅹⅹ

0

0

00

D0

0

01

D1

0

10

D2

0

11

D3

四、试用JK触发器和门电路设计一个同步模6格雷码计数器。

(20分)

要求:

1、写出三位格雷码,即循环码

2、以初始状态为001画出同步模6格雷码计数器状态图

3、电路接通电源时,必须置位到001状态

二OO三年数字逻辑电路试题

八、简答题(共25分)

1.32K字节的RAM有多少根地址线?

(2分)

2.一个6位全并行AD转换器里有多少个比较器?

(2分)

3.施密特触发器有几个稳定状态?

(2分)

4.格雷码(循环码)的特点是什么?

(2分)

5.举例说明逻辑代数中的对偶性。

(2分)

6.以输出低电平为例说明TTL门电路为什么有扇出限制?

(3分)

7.D/A转换方案中,转换速度最快的是哪一种?

为什么?

(3分)

8.EPLD是一类什么器件,可否用它实现时序电路?

(3分)

9.集成计数器芯片的同步清零与异步清零的区别。

(3分)

10.简述OC门电路的特点、功能及用途。

(3分)

九、试设计两个两位二进制数的大小比较器,当a1a0>b1b0时,F1=1;

当a1a0=b1b0时,F2=1;当a1a0 (10分) 十、试用3-8线译码器74138和与非门设计一位全加器。 (10分) 十一、分析题(共15分) 1.试分析如图由移位寄存器组成的序列产生器,分别写出dR、Q2输出的周期序列。 2.试分析如图计数器电路,在AB的控制下,可以实现几种模长的计数。 计数器的模分别是多少? 十二、试为一数据采集系统设计一个时序控制电路,其输入有时钟CP和控制启动信号Ctrl,输出为CLK,要求每来一个Ctrl负脉冲,经过3个CP周期延迟后,启动电路输出8个周期CLK(即16个CP周期),然后停止,等待下一次启动。 设计时使用的器件不限,可用任何器件和集成电路。 (15分) 二OO四年数字逻辑电路试题 八、简答题(每小题3分,共15分) (1)用开关原理说明三变量的与逻辑关系,写出逻辑函数 (2)试用对偶规则举例说明与、或运算及其定律的对偶性 (3)说明EPLD和FPGA特点 (4)试分别说明与非门和或非门空余输入端的 正确连接方法 (5)D/A转换器框图如图三所示,试说明能否用来 组成可程控放大器? 如能,请说明连接方法。 九、试用74161实现10分频,要求输出波形占空比为1: 1(6分) 十、试用D触发器设计两位可控左右移位寄存器(8分) 十一、某科研机构有一个重要实验室,其入口处有一自动控制电路如图四所示,图中DE为控制端,令上午、下午、晚上其取值分别为01、10、11。 现有三组科研人员(G1、G2、G3)在实验室做实验,A、B、C为对应G1、G2、G3的三个识别器,其上机的优先顺序是,上午为G1、G2、G3,下午为G2、G3、G1,晚上为G3、G1、G2;电路的输出F1、F2、F3为1时分别表示G1、G2、G3能上机同时打开实验室大门。 试分别用3-8线译码器和4选1数据选择器来完成电路设计,辅助门电路任选。 (15分) 十二、分析如图五所示时序电路分析并画出状态图(15分) 十三、试用集成计数器(任选)设计同步60进制BCD码加法计数器(8分) 十四、试用4片2114静态RAM(1K×4位)构成2K×8位的存储器(8分) 二OO五年数字逻辑电路试题 八、概念题(每小题2分,共10分) 1.试写出三种BCD编码形式? (2分) 2.试说明摩根定律和反演规则的关系? (2分) 3.试说明逻辑函数化简中最简与或表达式的条件? (2分) 4.试说明用硬件电路实现减法器的方法? (2分) 5.试述三态门的特点及应用? (2分) 九、简答题(每小题6分,共30分) 1.试建立1111序列检测器状态图,连续输入4个或4个以上的1,电路的输出为1,否则输出为0。 2.化简逻辑函数: F(A,B,C,D)=∑m(1,3,4,6,9,11,12,14),并用4选1数据选择器实现。 3.试实现一个三分频电路,输入为方波脉冲,要求输出信号占空比为1: 1。 4.分析如图所示触发器转换电路,分别说明当X=0和X=1的目标触发器是什么? 5.设输入为3位二进制数D2~D0,试根据下图示意设计一个组合逻辑电路,计算D2~D0中1的个数。 实现方式和器件不限。 十、试分析如图所示时序电路(10分) 十一、某数据采集系统的采集和存储部分电路原理框图如下图所示。 模拟输入信号(ViA)范围为0~500mV,信号调理电路的放大倍数为10倍,8位AD转换器的参考电压为5.1V。 数据经隔离器存入128×8bit的存储器中。 设系统工作时钟CLK为1MHz,AD转换采样率为100KHz(CP)。 (共25分)。 试完成下列任务: 1.计算AD转换器的分辨率及相对于模拟输入ViA的最小值? (4分) 2.设计分频器电路(6分) 3.设计地址发生器电路(10分) 4.如果采用两片4位的RAM(即128×4)构成存储器,试画出存储器部分的逻辑示意图(5分) 同步BCD加法计数器74160 4选1数据选择器逻辑符号128×4bitRAM逻辑符号 二00六年数字电路部分(共75分) 八、概念(每小题2分,共10分) 1.试写出三位循环(格雷)码? 2.试说明异步级联分频器的缺点? 3.试写出T触发器到D触发器的转换函数。 4.试说明“三人表决逻辑”中所包含最小项的个数? 5.试说明单稳态(振荡器)触发器有哪两种电路形式? 九、简答题(每小题5分,共20分)(可以不写详细设计过程) 1.试利用集成计数器和8选1数据选择器设计一个1011010序列发生器。 2.试用74138和与非门实现逻辑函数: F(A,B,C)=∑m(3,4,5,7)+∑Ф(0,2,6)。 3.一设计需要检测输入信号A的变化,当A有变化时(由高电平变到低电平、或由低电平变高电平、或正脉冲、或负脉冲),输出F为高。 设A初始状态不定(可能为高,也可能为低),F初始态为低,试设计该电路,直接画出电路,不用写设计过程。 4.试分析下图由4位加法器74283组成的两个两位二进制数运算电路的功能,说明运算结果数据中(F3,F2,F1,F0)每一位的含义及k的作用,说明何时输出为补码。 十、某进修班开设数字信号处理(5学分)、通信原理(4学分)、个人通信(3学分)和无线网络技术(2学分)四门课程。 若考试通过,可以获得相应的学分;若课程考试没通过,则得0学分。 规定至少获得9学分才可结业。 试用与非门设计该组合逻辑电路,判断进修生能否结业。 (13分) 十一、试分析如图所示同步时序电路,并给出结论(12分) 十二、某多功能信号发生器原理框图如下图所示,它可以产生4种信号(正弦波,三角波,阶梯波和梯形波)。 每种波形的一个周期用50个(字节)数据表示,依次分别预先存放在对应EPROM(64×8bit)存储器的前50个单元中。 K1、K2为波形输出选择控制端,功能见表1。 数模转换器(DAC)的参考电压为2.5V。 设系统输入工作时钟CLK为10MHz,DAC转换率设为4档(由K3,K4控制,见表2),分别为2MHz,1MHz,500KHz和250KHz(即CP)。 (共20分)。 试完成下列任务: 1.设计波形输出选择译码控制电路(4分) 2.设计分频控制电路(6分) 3.设计地址发生器电路(4分) 4.计算DA转换器的最小输出电压值? (3分) 5.若采用一片256×8位的EPROM来存储这4种波形数据,试说明应怎样存放数据,波形选择译码控制电路应怎样设计,画出简单示意图。 (3分) 表1 K1 K2 波形 0 0 正弦波 0 1 三角波 1 0 阶梯波 1 1 梯形波 表2 K3 K4 CP 0 0 2MHz 0 1 1MHz 1 0 500KHz 1 1 250KHz VREF 第4页 共6页 二00七年数字电路部分(共75分) 四、概念(每小题2分,共10分) 1.试写出一位比较器真值表。 2.试说明256分频至少需要多少个触发器? 3.试分别画出两变量“与逻辑”和“或逻辑”的开关图。 4.试说明OC门的特点及应用? 5.试说明8位逐次比较型AD转换器完成一次转换至少需要多少个时钟周期? 五、简答题(共20分) 1.试用2-4线译码器74139和与非门实现“三人表决”逻辑。 (6分) 2.试用D触发器构成右移移位寄存器,并完成串行序列延时三个时钟周期的电路(6分) 3.试分析如图所示多功能计数器电路,在A1A0的控制下,可以实现几种模长的计数。 计数器的模值分别是多少? (8分) 六、试用两片4位加法器74283和少量其它门电路设计一个8位二进制数带符号运算电路(加、减均可),两个8位二进制数为A(A7A6A5A4A3A2A1A0)和B(B7B6B5B4B3B2B1B0),其中A7,B7分别为A,B的符号位。 正数的符号位为0,负数的符号位为1。 做加运算时,k=0;做减运算时,k=1。 说明运算结果每一位的含义。 (12分) 第5页 共6页 表7-1 状态输出 速度 Q2 Q1 0 0 停止 0 1 1档 1 0 2档 1 1 3档 七、试用D触发器和少量其他门电路设计一个电子调速控制电路,其状态输出作为速度控制,见表7-1。 当外部输入K=1时,每来一个时钟脉冲增加一档,但到达最高档就不再增加了,同时给出满档指示,Y=1。 如果K=0,则每来一个时钟脉冲降低一档,直到停止,同时给出标志Z=1。 (13分) 八、某通信系统的可编程伪随机序列发生器电路结构示意图如图8-1所示,其64bit的数字码存储于一个8×8bit的ROM中,各位信息如表8-1所示。 电路工作时,每一个时钟CLK周期输出一个bit的串行数据,循环产生64位二进制序列。 试按下列要求进行序列发生器设计。 (20分) 1.若按列连续输出,如b07,b17,……,b77,b06,b16,……,b76,……,b00,b10,……,b70。 试完成电路设计? 2.若按行连续输出,如b00,b01,……,b07,b10,b11,……,b17,……,b70,b71,…,b77。 试完成电路设计? 第4页 共6页 二00八年数字电路部分(共75分) 四、概念题(每小题2分,共10分) 1.(123)十进制=()四进制=()八进制 2.TTL与非门的开门电阻Ron应取≥()欧姆,其对地最高电平是()伏。 3.试分别说明半加器和全加器的特点? 4.试说明32K字节的RAM有多少根地址线? 多少个存储单元(bit)? 5.试说明一个由4位移位寄存器构成的扭环计数器的主循环有几个状态? 五、简答题(每小题6分,共18分) 1.试用一片(只用一片,不加任何逻辑门)4位加法器74283(逻辑图见附图)实现5421BCD码到8421BCD码的转换电路。 2.试用一片3-8线译码器74138(逻辑图见附图)和与非门实现如下逻辑函数: f(A,B,C,D)=∑m(1,5,9,13)。 3.分析图3-1所示电路,写出输出逻辑函数F的最简表达式,说明当B=1时,G点的电平值为多少伏? 表6-1 供血血型 受血血型 A A,AB B B,AB AB AB O A,B,AB,O 六、试用四选一数据选择器和与非门为医院血站设计一个血型配对指示器,用以保证受血者的安全。 当供血血型与受血血型不符合表6-1所列情况时,输出为1,报警指示灯亮。 (15分) 第5页 共6页 七、试分析图7-1所示时序逻辑电路,分别求出P2,P1,P0及F的函数表达式,画出在CP作用下Q2,Q1,Q0,P2,P1,P0的波形图。 设控制参数B2B1B0=101,画出F的输出波形。 (15分) 八、莫尔斯电码由点(·)、划(-)两种符号按以下原则组成: ①一点为一基本信号单位,每一划的时间长度相当于3点的时间长度;②在一个字母或数字内,各点、各划之间的间隔应为两点的长度;③字母(数字)与字母(数字)之间的间隔为7点的长度。 国际救难信号“SOS”的莫尔斯电码为···———···。 按其设计规则,点用1表示,间隔用0表示,可以将“SOS”的莫尔斯电码变成如下的二值序列: 1001001000000011100111001110000000001001001 试设计此“SOS”序列的发生器电路。 (17分) 注: ①给定时钟信号为100KHz,器件任选; ②为设计方便,序列长度可以最多补“0”到64位,但不是必须的。 附图: 集成电路功能表 第6页 共6页 74166功能简表 CR Shift/ load CLK 并行输入 A…H 输出 QH 功能 L × × × L 清零 H × L × QH0 保持 H L ↑ A…H H 置数 H H ↑ × QGn 右移

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 哈工大数电打印 哈工大 打印

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx