CadenceAllegro元件封装制作流程.docx

CadenceAllegro元件封装制作流程.docx

- 文档编号:9848443

- 上传时间:2023-02-07

- 格式:DOCX

- 页数:23

- 大小:1.50MB

CadenceAllegro元件封装制作流程.docx

《CadenceAllegro元件封装制作流程.docx》由会员分享,可在线阅读,更多相关《CadenceAllegro元件封装制作流程.docx(23页珍藏版)》请在冰豆网上搜索。

CadenceAllegro元件封装制作流程

CadenceAllegro元件封装制作流程

1.引言

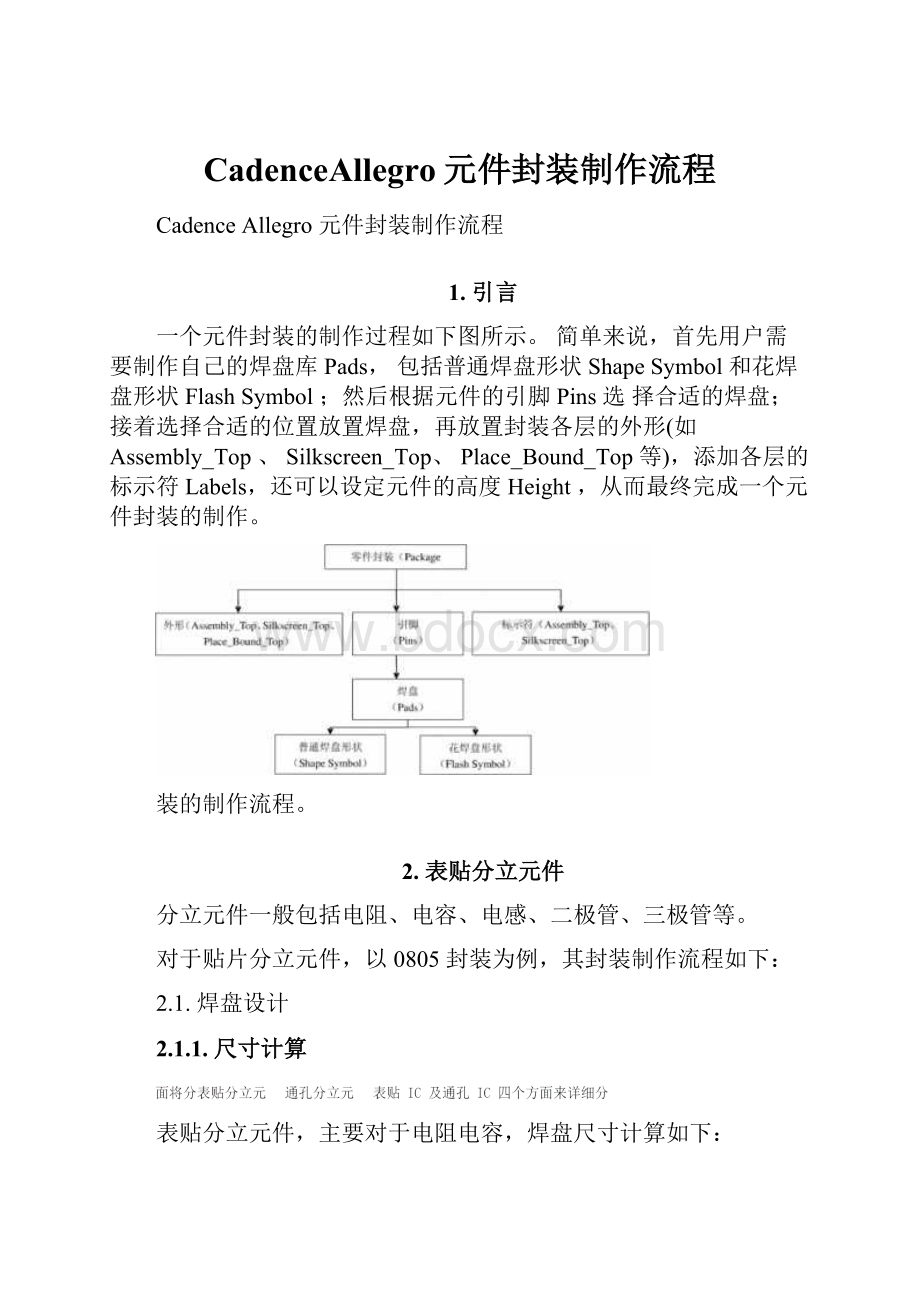

一个元件封装的制作过程如下图所示。

简单来说,首先用户需要制作自己的焊盘库Pads,包括普通焊盘形状ShapeSymbol和花焊盘形状FlashSymbol;然后根据元件的引脚Pins选择合适的焊盘;接着选择合适的位置放置焊盘,再放置封装各层的外形(如Assembly_Top、Silkscreen_Top、Place_Bound_Top等),添加各层的标示符Labels,还可以设定元件的高度Height,从而最终完成一个元件封装的制作。

装的制作流程。

2.表贴分立元件

分立元件一般包括电阻、电容、电感、二极管、三极管等。

对于贴片分立元件,以0805封装为例,其封装制作流程如下:

2.1.焊盘设计

2.1.1.尺寸计算

表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:

其中,K为元件引脚宽度,H为元件引脚高度,W为引脚长度,P为两引脚之间距离(边距离,非中心距离),L为元件长度。

X为焊盘长度,Y为焊盘宽度,R为焊盘间边距离,G为封装总长度。

则封装的各尺寸可按下述规则:

1)X=Wmax+2/3*Hmax+8mil

2)Y=L,当L<50mil;Y=L+(6~10)mil,当L>=50mil时

3)R=P-8=L-2*Wmax-8mil;或者G=L+X。

这两条选一个即可。

个人觉得后者更容易理解,相当于元件引脚外边沿处于焊盘中点,这在元件尺寸较小时很适合(尤其是当Wmax标得不准时,第一个原则对封装影响很大),但若元件尺寸较大(比如说钽电容的封装)则会使得焊盘间距过大,不利于机器焊接,这时候就可以选用第一条原则。

本文介绍中统一使用第二个。

注:

实际选择尺寸时多选用整数值,如果手工焊接,尺寸多或少几个mil影响均不大,可视具体情况自由选择;若是机器焊接,最好联系工厂得到其推荐的尺寸。

例如需要紧凑的封装则可以选择小一点尺寸;反之亦然。

另外,还有以下三种方法可以得到PCB的封装尺寸:

通过LPWizard等软件来获得符合IPC标准的焊盘数据。

直接使用IPC-SM-782A协议上的封装数据(据初步了解,协议上的尺寸一般偏大)。

如果是机器焊接,可以直接联系厂商给出推荐的封装尺寸。

2.1.2.焊盘制作

Cadence制作焊盘的工具为Pad_designer。

打开后选上Singlelayermode,填写以下三个层:

1)顶层(BEGINLAYER):

选矩形,长宽为X*Y;

2)阻焊层(SOLDERMASK_TOP):

是为了把焊盘露出来用的,也就是通常说的绿油层实际上就是在绿油层上挖孔,把焊盘等不需要绿油盖住的地方露出来。

其大小为SolderMask=RegularPad+4~20mil(随着焊盘尺寸增大,该值可酌情增大),包括X和Y。

3)助焊层(PASTEMASK_TOP):

业内俗称“钢网”或“钢板”。

这一层并不存在于印制板上,而是单独的一张钢网,上面有SMD焊盘的位置上镂空。

这张钢网是在SMD自动装配焊接工艺中,用来在SMD焊盘上涂锡浆膏用的。

其大小一般与SMD焊盘一样,尺寸略小。

其他层可以不考虑。

以0805封装为例,其封装尺寸计算如下表:

mm

mil

确定mil值

长

2

78.74015748

宽

1.27

50

高(max)

1.25

49.21259843

W(max)

0.7

27.55905512

X

1.330133333

52.36745407

50

Y

1.27

50

60

G

3.330133333

131.1076115

130

可见焊盘大小为50*60mil。

该焊盘的设置界面如下:

保存后将得到一个.pad的文件,这里命名为Lsmd50_60.pad。

2.2.封装设计

2.2.1.各层的尺寸约束

一个元件封装可包括以下几个层:

1)元件实体范围(Place_bound)

含义:

表明在元件在电路板上所占位置的大小,防止其他元件的侵入,若其他元件进入该区域则自动提示DRC报错。

形状:

分立元件的Place_bound一般选用矩形。

尺寸:

元件体以及焊盘的外边缘+10~20mil,线宽不用设置。

2)丝印层(Silkscreen)

含义:

用于注释的一层,这是为了方便电路的安装和维修等,在印刷板的上下两表面印刷上所需要的标志图案和文字代号等,例如元件标号和标称值、元件外廓形状和厂家标志、生产日期等等。

形状:

分立元件的Silkscreen一般选用中间有缺口的矩形。

若是二极管或者有极性电容,还可加入一些特殊标记,如在中心绘制二极管符号等。

尺寸:

比Place_bound略小(0~10mil),线宽可设置成5mil。

3)装配层(Assembly)

含义:

用于将各种电子元件组装焊接在电路板上的一层,机械焊接时才会使用到,例如用贴片机贴片时就需要装配层来进行定位。

形状:

一般选择矩形。

不规则的元件可以选择不规则的形状。

需要注意的是,Assembly指的是元件体的区域,而不是封装区域。

尺寸:

一般比元件体略大即可(0~10mil),线宽不用设置。

2.2.2.封装制作

Cadence封装制作的工具为PCB_Editor。

可分为以下步骤:

1)打开PCB_Editor,选择File->new,进入NewDrawing,选择Packagesymbol并设置好存放路径以及封装名称(这里命名为LR0805),如下图所示:

2)选择Setup->DesignParameter中可进行设置,如单位、范围等,如下图所示:

3)选择Setup->Grids里可以设置栅格,如下图所示:

Setup->UserPreferences中

4)放置焊盘,如果焊盘所在路径不是程序默认路径,则可以在

进行设计,如下图左所示,然后选择Layout->Pins,并在options中选择好配置参数,如下图中所示,在绘图区域放置焊盘。

放置时可以使用命令来精确控制焊盘的位置,如x-400表示将焊盘中心位于图纸中的(-40,0)位置处。

放置的两个焊盘如下图右所示。

5)

放置元件实体区域(Place_Bound),选择Shape->Rectangular,options中如下图左设置,放置矩形时直接定义两个顶点即可,左上角顶点为x-7540,右下角顶点为x75-40。

绘制完后如下图右所示。

6)

放置丝印层(Silkscreen),选择Add->Lines,options中如下图左所示。

绘制完后如下图右所示。

7)放置装配层(Assembly),选择Add->Lines,options中如下图左所示。

放置完后如下图右所示,装配层的矩形则表示实际元件所处位置。

8)放置元件标示符(Labels),选择Layout->Labels->RefDef,标示符包括装配层和丝印层两个部分,options里的设置分别如下图左和中所示,由于为电阻,均设为R*,绘制完

后如下图右所示。

9)放置器件类型(Device,非必要),选择Layout->Labels->Device,options中的设置如下图左所示。

这里设置器件类型为Reg*,如下图右所示。

10)设置封装高度(PackageHeight,非必要),选择Setup->Areas->PackageHeight,选中封装,在options中设置高度的最小和最大值,如下图所示。

11)至此一个电阻的0805封装制作完成,保存退出后在相应文件夹下会找到LR0805.dra和LR0805.psm两个文件(其中,dra文件是用户可操作的,psm文件是PCB设计时调用的)。

3.直插分立元件通孔分立元件主要包括插针的电阻、电容、电感等。

本文档将以1/4W的M型直插电阻为例来进行说明。

3.1.通孔焊盘设计

3.1.1.尺寸计算

=DRILL_SIZE+36mil,DRILL_SIZE<50mil=DRILL_SIZE+50mil,DRILL_SIZE>=50mil=DRILL_SIZE+60mil,DRILL_SIZE为矩形或椭圆形开口宽度=(OD-ID)/2+10mil

3.1.2.焊盘制作

以1/4W的M型直插电阻为例,其引脚直径20mil,根据上述原则,钻孔直径应该为

32mil,RegularPad的直径为48mil,Anti-pad的直径为68mil,热风焊盘的内径为52mil,外径为68mil,开口宽度为18mil。

焊盘制作过程分两大步骤:

制作热风焊盘和制作通孔焊盘。

首先制作热风焊盘。

使用PCBDesigner工具,步骤如下:

1)选择File->New,在NewDrawing对话框中选择Flashsymbol,命名一般以其外径和内径命名,这里设为TR_68_52,如下图所示。

2)

选择Add->Flash,按照上述尺寸进行填写,如下图左所示。

完成后,如下图右所示。

热风焊盘制作完成后,可以进行通孔焊盘的制作。

使用的工具为Pad_Designer。

步骤如

下:

1)File->New,新建Pad,命名为pad48cir32d.pad,其中,48表示外径,cir表示圆形,32表示内径,d表示镀锡,用在需要电气连接的焊盘或过孔,若是u则表示不镀锡,一般用于固定孔。

2)在Parameters选项中设置如下图所示。

图中孔标识处本文选用了cross,即一个“+”字,也可选用其他图形,如六边形等。

3)在Layer中需填写以下几个层。

一般情况下,一个通孔的示意图如下图所示。

a.顶层(BEGINLAYER)根据需要来选择形状和大小,一般与RegularPad相同,也可以选择其他形状用于标示一些特殊特征,例如有极性电容的封装中用正方形焊盘标示正端。

这里设置成圆形,直径为48mil。

b.中间层(DEFAULT_INTERNAL)选择合适尺寸的热风焊盘;注意,若热风焊盘存的目录并非安装目录,则需要在PCBDesigner中选择Setup->UserPreferences中的psmpath中加入适当路径,如下图所示。

c.底层(END_LAYER)一般与顶层相同,可以copy顶层的设置并粘贴到底层来。

d.阻焊层(SOLDERMASK_TOP和SOLDERMASK_BOTTOM):

SolderMask=RegularPad+4~20mil(焊盘直径越大,这个值也可酌情增大)。

e.助焊层(PASTEMASK_TOP和PASTEMASK_BOTTOM):

这一层仅用于表贴封装,在直插元件的通孔焊盘中不起作用,但可以设置,会被忽略。

f.预留层(FILMMASK_TOP和FILMMASK_BOTTOM):

预留,可不用。

最终该通孔焊盘layer层参数配置如下图所示。

3.2.封装设计

3.2.1.各层的尺寸约束

除丝印层的形状外,直插分立元件的约束与2.2.1节基本类似。

对于丝印层,其形状与元件性质有关:

1)对于直插式电阻、电感或二极管,丝印层通常选择矩形框,位于两个焊盘内部,且两端抽头;

2)对于直插式电容,一般选择丝印框在焊盘之外,若是扁平的无极性电容,形状选择矩形;若是圆柱的有极性电容,则选择圆形。

3)对于需要进行标记的,如有极性电容的电容的正端或者二极管的正端等,除却焊盘做成矩形外,丝印层也可视具体情况进行标记。

3.2.2.封装制作

仍然以1/4W的M型直插电阻为例,其引脚直径20mil,引脚间距400mil,元件宽度约80mil,元件长度为236mil,直插电阻封装的命名一般为AXIAL-xx形式(比如AXIAL-0.3、AXIAL-0.4),后面的xx代表焊盘中心间距为xx英寸,这里命名为AXIAL-0.4L。

其封装制作步骤如下(与2.2.2节中相同的部分将省略):

1)放置焊盘,放置的两个焊盘如下图所示。

2)放置元件实体区域(Place_Bound),绘制完后如下图右所示。

3)放置丝印层(Silkscreen),选择Add->Lines,options中如下图左所示。

绘制完后如下图右所示。

4)放置装配层(Assembly),选择Add->Lines,options中如下图左所示。

放置完后如下图右所示,装配层的矩形则表示实际元件所处位置。

5)放置元件标示符(Labels)和器件类型(Device),如下图左所示。

4.表贴IC

表贴IC是目前电子系统设计过程中使用最为广泛地,本文以集成运放AD8510的SO8为例来进行叙述。

其尺寸图如下所示。

4.1.焊盘设计

4.1.1.尺寸计算

1)对于如SOP,SSOP,SOT等符合下图的表贴IC。

其焊盘取决于四个参数:

脚趾长度W,脚趾宽度Z,脚趾指尖与芯片中心的距离D,引脚间距P,如下图:

S

焊盘尺寸及位置计算:

X=W+48mil

S=D+24mil

Y=P/2+1,当P<=26mil;Y=Z+8,当P>26mil。

2)对于QFN封装,由于其引脚形式完全不同,一般遵循下述原则:

PCBI/O焊盘的设计应比QFN的I/O焊端稍大一点,焊盘内侧应设计成圆形(矩形亦可)以配合焊端的形状,详细请参考图2和表1。

典型的QFN元件I/O焊端尺寸(mm)

典型的PCBI/O焊盘设计指南(mm)

焊盘间距

焊盘宽度(b)

焊盘长度(L)

焊盘宽度(X)

外延(Tout)

内延(Tin)

0.8

0.33

0.6

正常0.42

最小0.15

最小0.05

0.65

0.28

0.6

正常0.37

最小0.15

最小0.05

0.5

0.23

0.6

正常0.28

最小0.15

最小0.05

0.5

0.23

0.4

正常0.28

最小0.15

最小0.05

0.4

0.20

0.6

正常0.25

最小0.15

最小0.05

如果PCB有设计空间,I/O焊盘的外延长度(Tout)大于0.15mm,可以明显改善外侧焊点形成,如果内延长度(Tin)大于0.05mm,则必须考虑与中央散热焊盘之间保留足够的间隙,以免引起桥连。

通常情况下,外延取0.25mm,内延取0.05mm。

手工焊接时外延可更长。

以下是典型的例子:

4.1.2.焊盘制作

参考AD8056的SO8封装尺寸,W=(16+50)/2=33mil,P=50mil,Z=(19.2+13.8)/2=17.5mil,故而X取80mil,Y取25mil。

制作的详细过程同2.1.2,参数配置界面如下图所示。

4.2.封装设计

4.2.1.各层的尺寸约束

除丝印层外,表贴IC的各层约束规则与2.2.1类似,这里不再赘述。

对于丝印层,表贴IC的丝印框与引脚内边间距10mil左右,线宽5mil,形状与该IC的封装息息相关,通常为带有一定标记的矩形(如切角或者打点来表示第一脚)。

对于sop等两侧引脚的封装,长度边界取IC的非引脚边界即可。

丝印框内靠近第一脚打点标记,丝印框外,第一脚附近打点标记,打点线宽视元件大小而定,合适即可。

对于QFP和BGA封装(引脚在芯片底部的封装),一般在丝印框上切角表示第一脚的位置。

4.2.2.封装制作

参考AD8056的SO8封装尺寸,D=(228.4+244)/4=118.1mil,故而S=142mil,取140mil。

与2.2.2中重复的部分这里不再赘述。

1)放置焊盘

可以选择批量放置焊盘,options中设置如下图左所示,放置完后如下图右所示。

2)放置外形和标识这里与2.2.2基本,

5.通孔IC

本文档以一个DIP8封装为例来进行说明。

DIP封装的尺寸如下图所示。

5.1.通孔焊盘设计

通孔焊盘设计过程与3.1节类似,区别在于对于通孔IC,一般会用一个特殊形状的通孔来表示第一脚,这里第一脚的焊盘用正方形,其他为圆形。

引脚直径d(一般的引脚并非圆柱而是矩形,此时d应该取长度)为0.46mm,接近20

mil,故钻孔直径32mil,焊盘直径48mil,Anti-pad的直径为68mil,热风焊盘的内径为52mil,外径为68mil,开口宽度为18mil。

命名为pad48cir32d.pad,与3.1.2节相同。

由于还需要一个正方形的焊盘,命名为pad48sq32d.pad,其设置如下图所示。

5.2.封装设计

封装设计过程与前所述基本类似。

这里仅给出每一步的截图。

1)批量放置8个焊盘如下图左,更换掉1脚的焊盘后如下图右。

更换时可使用Tools->Replace命令,其options的设置如下图中所示。

2)放置各层外形和标识后如下图所示。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- CadenceAllegro 元件 封装 制作 流程

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《JAVA编程基础》课程标准软件16级.docx

《JAVA编程基础》课程标准软件16级.docx