大学数字逻辑复习.docx

大学数字逻辑复习.docx

- 文档编号:9794236

- 上传时间:2023-02-06

- 格式:DOCX

- 页数:25

- 大小:125.08KB

大学数字逻辑复习.docx

《大学数字逻辑复习.docx》由会员分享,可在线阅读,更多相关《大学数字逻辑复习.docx(25页珍藏版)》请在冰豆网上搜索。

大学数字逻辑复习

第0章绪论

一、模拟信号

模拟量:

时间和数值连续变化的物理量。

模拟信号:

模拟量的电信号。

模拟电路:

工作在模拟信号下的电路。

二、数字信号

数字量:

时间和数值不连续变化的物理量。

※数字信号:

数字量的电信号。

※数字电路:

工作在数字信号下的电路。

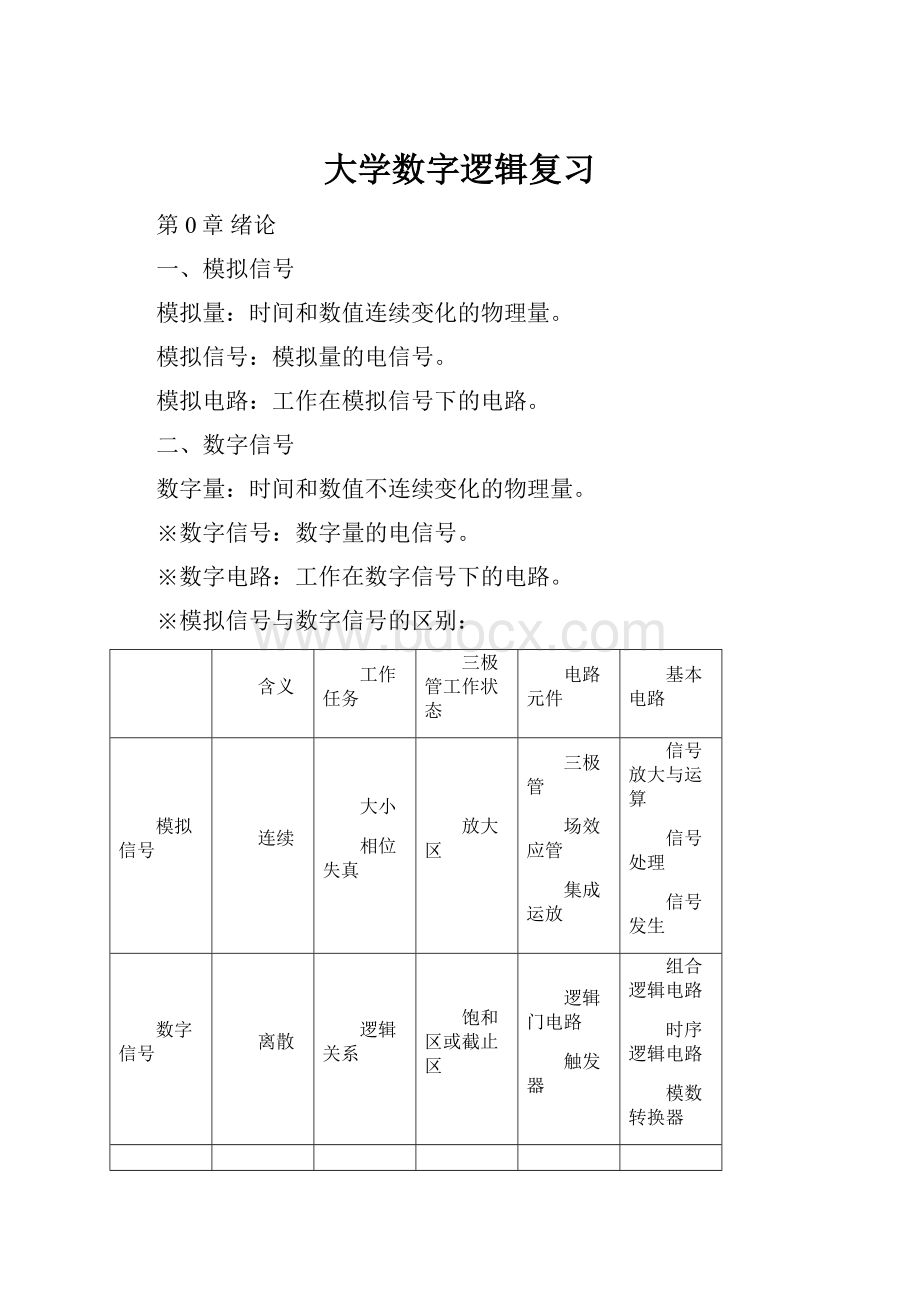

※模拟信号与数字信号的区别:

含义

工作任务

三极管工作状态

电路元件

基本电路

模拟信号

连续

大小

相位

失真

放大区

三极管

场效应管

集成运放

信号放大与运算

信号处理

信号发生

数字信号

离散

逻辑关系

饱和区或截止区

逻辑门电路

触发器

组合逻辑电路

时序逻辑电路

模数转换器

第1章逻辑函数

1.1数制与数制转换

一、数的表示法

(一)十进制

含义:

以10为基数的计数体制,如:

0~9。

(二)二进制

含义:

以2为基数的计数体制,如:

0和1。

(三)八进制

含义:

以8为基数的计数体制,如:

0~7。

(四)十六进制

含义:

以16为基数的计数体制,如:

0~9、A(10)、B(11)、C(12)、D(13)、E(14)、F(15)。

※数制小结:

数码

基数

位权

表示形式

十进制数

0~9

10

10i

D=∑ki×10i

二进制数

0~1

2

2i

D=∑ki×2i

八进制数

0~7

8

8i

D=∑ki×8i

十六进制数

0~9及A~F

16

16i

D=∑ki×16i

基数:

数码个数。

位权:

不同数位上数值大小的一个固定常数。

不同数制对照表:

十进制

二进制

八进制

十六进制

0

1

2

3

4

5

6

7

8

9

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

二、数制转换

(一)二进制数转换成十进制数

法:

整数部分从右往左(幂计0)

小数部分从左往右(幂计-1)

按权展开求和

例子:

例1.1.1

(二)十进制数转换成二进制数

法:

整数部分除2,余数从下往上排列

小数部分乘2,乘积整数部分从上往下排列

例子:

例1.1.3和例1.1.4

(三)二进制数转换成十六进制数

法:

整数部分从右往左4位二进制→等值十六进制

小数部分从左往右4位二进制→等值十六进制

不足4位补0

(四)十六进制数转换成二进制数

法:

十六进制→等值4位二进制

例子:

例1.1.7

(五)二进制数转换成八进制数

法:

整数部分从右往左3位二进制→等值八进制

小数部分从左往右3位二进制→等值八进制

不足3位补0

例子:

例1.1.6

(六)八进制数转换成二进制数

法:

八进制→等值3位二进制

※数制转换小结:

R进制数转换成十进制数:

将R进制数按权展开求和

十进制数转换成R进制数:

①整数部分除R取余数(下至上);②小数部分乘R取乘积整数部分(上至下)

二进制与R进制互转:

①3位二进制数对应1位八进制数;②4位二进制数对应1位十六进制数

三、算术、逻辑运算

算术运算:

当用两个数码表示两个数值时进行数值运算。

逻辑运算:

当二进制数码0和1表示逻辑状态时按某种因果关系进行运算。

四、编码

(一)二-十进制编码

含义:

用4位二进制码表示一个十进制数,简称BCD码。

分类:

有权码和无权码

✓有权码:

二进制码中的各位数码都有固定的位权值。

✓无权码:

二进制码中的各位数码没有固定的位权值。

※8421码:

4位二进制码从高到低的权依次为8、4、2、1。

2421码:

4位二进制码从高到低的权依次为2、4、2、1。

5121码:

4位二进制码从高到低的权依次为5、4、5、1。

※余3码:

8421码加0011。

余3格雷码:

某十进制数加3对应的格雷码。

右移码:

右边4位由前一码组右移一位,最左一位由前一码组最右一位取反。

(二)二进制编码

含义:

用n位二进制码来表示m个特定信息,2n≥m。

1.格雷码

※含义:

设二进制码B=Bn-1Bn-2…Bi+1Bi…B1B0

格雷码G=Gn-1Gn-2…Gi+1Gi…G1G0

转换后的格雷码为Gn-1=Bn-1Gi=Bi+1⊕Bi

※特点:

任意两个相邻的格雷码仅有一位不同;

十进制数2n-1的格雷码第n位为1,其余位为0;

2.奇偶校验码

※含义:

n位信息位和1位校验位P组成。

※分类:

奇校验和偶校验

•奇校验:

P的取值使奇偶校验码中“1”的个数为奇数。

•偶校验:

P的取值使奇偶校验码中“1”的个数为偶数。

特点:

编码简单、编码电路和检测电路简单;

只能查奇错,不能查偶错,不能错误定位和纠正错误;

1.2逻辑函数

1.4几种常用的复合逻辑及逻辑门

一、基本逻辑※

(一)基本逻辑

与:

Y=A·B,见0出0,全1出1

或:

Y=A+B,见1出1,全0出0

非:

Y=A,0则1,1则0

(二)复合逻辑

与非:

Y=AB,全1出0,见0出1

或非:

Y=A+B,全0出1,见1出0

与或非:

Y=AB+CD

异或:

Y=A⊕B,相同为0,相异为1

同或:

Y=A⊙B,相同为1,相异为0

二、常用公式※

三、运算规则※

代入规则:

F:

G替代所有A,等式仍成立。

反演规则:

F:

·<->+,0<->1,原变量<->反变量

例子:

例1.2.2

对偶规则:

F’:

·<->+,0<->1

例子:

例1.2.3

1.3逻辑函数的标准型

一、两种标准形式

(一)最小项及标准与或式

※最小项:

n个变量组成的与项,若每一个变量都以Ai或/Ai的形式出现一次且仅一次,则是最小项。

※标准与或式:

最小项的逻辑加构成的逻辑函数式。

※性质:

只有一个最小项的值为1,其余为0;

全部最小项之和为1;

(二)最大项及标准或与式

※最大项:

n个变量组成的或项,若每一个变量都以Ai或/Ai的形式出现一次且仅一次,则是最大项。

※标准或与式:

最大项的逻辑乘构成的逻辑函数式。

※性质:

只有一个最大项的值为0,其余为1;

全部最大项之积为0;

(三)最小项与最大项的关系

※相同编号的最小项和最大项互补:

mi=/MiMi=/mi

二、逻辑函数转换成标准型

(一)真值表

例子:

例1.3.1

标准与或式:

F=1的最小项之和

标准或与式:

F=0的最大项之积

(二)公式A+/A=1A·/A=0

例子:

例1.3.2

1.5逻辑函数的简化

一、公式化简※

含义:

运用逻辑代数的定理、公式和运算规则对逻辑函数进行等式变换,使逻辑式为最简式。

最简式:

与或式、或与式

①与或式:

与项个数最少、变量个数最少

②或与式:

或项个数最少、变量个数最少

例子:

例1.5.1例1.5.2例1.5.3例1.5.4例1.5.5例1.5.6

二、卡诺图化简※

(一)卡诺图

卡诺图/真值图:

将真值表改用格图表示,使最小项相邻排列。

(图1.5.1图1.5.2)

特点:

上下边界、左右边界、以对称轴对称的位置、几位置相邻的最小项均为逻辑相邻最小项。

(如:

m0和m4、m1、m2、m8

)

变量位置按从高到低、先行后列的顺序排列,影响最小项编号。

(如:

A、B、C、D)

变量取值1为原变量,取值0为反变量。

(二)作卡诺图

法:

最小项填1,不包含的最小项填0。

例子:

例1.5.7

(三)化简逻辑函数

1.合并规则

两项:

消去一个变量,保留公因子

四项:

消去两个变量,保留公因子

八项:

消去三个变量,保留公因子

十六项:

消去四个变量,1

结论:

2i个项合并成一项,消去i个变量,保留公因子

2.化简步骤

逻辑函数变换成与或式

画卡诺图

画圈合并

公因子相加

注意:

(1)孤立的单格单独画圈

(2)圈“1”须是2i个

(3)圈的数量少、围大、可重复包围、但圈需有新的最小项

(4)某个最小项被其它圈分别包围,则是多余圈需消除

(5)不能遗漏任一个最小项

例子:

例1.5.9例1.5.10例1.5.12例1.5.13

3.含无关项的逻辑函数化简

含无关项的逻辑函数:

n个变量的逻辑函数不是2n个最小项都为0或1,其中一部分有确定值,另一部分无确定值。

F=∑m+∑φ

∑φ:

无关项,包含约束项和任意项,用φ表示,“1”或“0”,包围圈须含最小项,不能全是无关项。

例子:

例1.5.14

第3章组合逻辑电路

3.1组合逻辑电路的设计

3.2组合逻辑电路的分析

数字电路的分类:

组合逻辑电路、时序逻辑电路

组合逻辑电路:

任意时刻的输出取决于该时刻输入状态,与之前状态无关。

特点:

电路由逻辑门构成,不含记忆元件。

输出无反馈到输入回路。

一、组合逻辑电路的设计

※设计步骤:

依据设计要求列出真值表;写出最简逻辑表达式;依据提供的器件类型进行函数表达式的变换;画逻辑图。

例子:

例3.1.1例3.1.2例3.1.3

二、组合逻辑电路的分析

※分析步骤:

写出电路的逻辑函数表达式;简化逻辑函数,求出最简逻辑函数或列真值表;描述电路的逻辑功能。

例子:

例3.2.1例3.2.2

3.3编码器

一、二进制编码器

(一)普通编码器

※含义:

编码器只能对一个输入信号进行编码,或为高电平或为低电平。

(二)优先编码器

※含义:

允同时输入两个以上的编码信号,但只对其中优先权最高的一个进行编码。

74LS148:

/QEX:

扩展输出端。

电路工作/IS=0且有编码输入:

/QEX=0

/QS:

选通输出端。

电路工作/IS=0且无编码输入:

/QS=0

/QC、/QB、/QA:

输出端

/IS:

使能输入端。

/IS=1,禁止编码、/IS=0,允编码

/I7~/I0:

输入端

例子:

图3.3.4

3.4译码与译码器

新课导入:

译码是编码的逆操作,把二进制代码转换成高或低电平信号输出。

实现译码功能的逻辑电路为译码器。

译码器也是数据分配器,即将单个数据由多路端口输出。

译码器分类:

二进制译码器、十进制译码器、显示译码器。

数据分配器:

原理:

1根输入线、n根地址线/控制线、2n根输出线,称1-2n路数据分配器。

含义:

将公共数据线上的数据按地址代码送到不同数据线上的逻辑电路。

一、二进制译码器

※含义:

译码器的输入二进制代码为n位,输出的信号个数为2n,也称n-2n线译码器。

(一)3-8线译码器

G1=0或/G2A+/G2B=1,禁止译码,/Yi=1

G1=0或/G2A+/G2B=0,允译码,/Yi=/mi(输出对应输入最小项的非)

(二)4-16线译码器

图见PPT

例子:

例3.4.1例3.4.2

二、十进制译码器

※含义:

译码器的输入是8421BCD码,输出为10个端口,也称4-10线译码器。

译码器拒绝“翻译”,具有拒绝非法码的功能。

例子:

例3.4.3

三、显示译码器

含义:

将译码输出的高低电平显示成0-9、字母、图案,这需要显示器件,而驱动显示器件的译码器为显示译码器。

(一)半导体数码管

构成:

7个发光二极管构成一个“8”。

分类:

共阴极、共阳极。

(二)显示译码器

含义:

输入为8421BCD码,输出为a-g7个高低电平信号,又称4-7线译码器或代码转换器。

/LT:

a-g=1,数码管显示“8”,译码时加高电平。

/RBI:

输入0000,输出a-g=0,熄灭显示的“0”。

/BI:

无论输入状态如,数码管全灭。

/RBO:

/RBO=LT·/RBI·/A3·/A2·/A1·/A0,熄灭本应显示的“0”。

例子:

3.5加法器&比较器

一、加法器

(一)半加器

※含义:

不考虑低位的进位,将两个1位的二进制数相加。

Si=Ai⊕BiCi=AiBi

(二)全加器

※含义:

考虑来自低位的进位,将两个1位二进制数及低位的进位相加。

Si=Ai⊕Bi⊕Ci-1Ci=AiBi+(Ai⊕Bi)Ci-1

1.串行进位加法器

原理:

Ai和Bi并行相加,产生的进位由低到高位逐级传递。

特点:

结构简单、运算速度慢。

2.超前进位加法器

原理:

进位信号与Gi、Pi有关,即进位信号只与Ai和Bi有关。

优点:

可以并行产生,实现快速进位。

例子:

图3.5.6图3.5.7

二、比较器

※含义:

比较一位或多位二进制数大小的电路。

(一)1位数值

FA>B=ABFA (二)4位数值 首先比较最高位,最高位相等时,再比较次高位,直到所有位数比较完为止。 若4位比较结果都相等,再看级联信号输入,级联输入信号由低位比较器输出而来。 没有更低位参与比较时,级联输入GA>B、SA 例子: 图3.5.10图3.5.11 3.6数据选择器 数据选择器: 根据输入地址码的不同,从多路输入数据中选择一路数据输出的电路。 一、双4选1数据选择器 W=(/A1/A0D0+/A1A0D1+A1/A0D2+A1A0D3)//S 二、8选1数据选择器 W=(/A2/A1/A0D0+/A2/A1A0D1+/A2A1/A0D2+/A2A1A0D3+A2/A1/A0D4+A2/A1A0D5+A2A1/A0D6+A2A1A0D7)//S 例子: 图3.6.4例3.6.1例3.6.2例3.6.3例3.6.4图3.6.9 3.8组合逻辑电路中的竞争冒险 一、产生的原因 F=A/A,1冒险 F=A+/A,0冒险 ※竞争: 多个信号经不同路径到达某一点有时间差。 ※冒险: 竞争导致电路产生暂时的错误的输出。 二、消除的法 ※引入选通脉冲: 电路稳定后再对输入信号的逻辑值取样 ※增加冗余项: 相邻项画圈 例子: 例3.8.1例3.8.2 第4章触发器 4.1RS触发器 一、基本RS触发器 (一)电路结构 ※Qn: 时钟脉冲出现之前的状态(原状态),称现态。 ※Qn+1: 时钟脉冲出现之后的状态(新状态),称次态。 (二)逻辑功能※ /S=1,/R=0: Q=0,置0态或复位 /S=0,/R=1: Q=1,置1态或置位 /S=1,/R=1: Qn+1=Qn,保持原态(记忆功能) /S=0,/R=0: Qn+1=/Qn+1=1,禁态(当/S=/R=0变为/S=/R=1时,触发器状态不确定) (三)特点※ 输入端状态直接影响输出端状态,无统一CP控制。 二、时钟RS触发器 (一)电路结构 (二)逻辑功能※ 1.CP=0 Qn+1=Qn 2.CP=1 S=0,R=0,Qn+1=Qn S=0,R=1,Qn+1=0 S=1,R=0,Qn+1=1 S=1,R=1,Qn+1=φ CP=1: Qn+1=S+/RQ SR=0 例子: 图4.1.6 (三)特点※ CP=0时,输出状态保持不变;CP=1时,输出状态随输入状态而改变。 CP=1时,触发器多次翻转,即空翻、次态不确定。 4.2JK触发器 一、主从JK触发器 (一)电路结构 解决RS=0(J、K不存在约束条件) (二)逻辑功能※ 当J=0,K=0时,Qn+1=Qn,不变 当J=0,K=1时,Qn+1=0,置0 当J=1,K=0时,Qn+1=1,置1 当J=1,K=1时,Qn+1=/Qn,取反 例子: 图4.2.4 (三)一次翻转和特点※ 含义: CP=1时,J出现干扰脉冲由0→1,Q=0→1。 特点: 解决了主从RS触发器的约束问题,但抗干扰能力弱。 二、边沿JK触发器 (一)电路结构 由时钟控制门和基本RS触发器组成。 (二)逻辑功能※ 1.CP=0 Qn+1=Qn 2.CP=0→1 Qn+1=Qn 3.CP=1→0 Qn+1=S+/RQ=JQ+/KQ J=0,K=0,不变 J=0,K=1,置0 J=1,K=0,置1 J=1,K=1,取反 (三)特点※ 边沿JK触发器解决了主从JK触发器一次变化问题,提高了触发器的抗干扰能力。 4.3D触发器 一、维持阻塞D触发器 (一)电路结构 /SD: 异步置位端 /RD: 异步复位端 触发式: CP上升沿触发 (二)逻辑功能※ 当CP=0时,Qn+1=Qn 当CP=0→1,D=0时,Qn+1=0(置0),Q4至门6输入端的连线称为置0维持线,Q6至门5输入端的连线称为置1阻塞线 当CP=0→1,D=1时,Qn+1=1(置1),Q3至门5输入端的连线称为置1维持线,Q3至门4输入端的连线称为置0阻塞线 所以,CP上升沿: Qn+1=D 例子: 图4.3.3 (三)特点※ 克服空翻、抗干扰能力比主从JK触发器强 二、CMOS正边沿D触发器 ※特点: 抗干扰能力比维持阻塞D触发器更强 4.4T和T’触发器 一、T触发器 CP作用后: T=0时,状态保持不变,Qn+1=Qn T=1时,状态翻转,Qn+1=/Qn 所以,Qn+1=/TQn+T/Qn 二、T’触发器 每来一个CP脉冲,触发器状态就翻转一次,翻转次数即CP脉冲的个数 所以,Qn+1=Qn 4.5集成触发器注意问题 一、触发器的选用 ※基本RS触发器: 无统一CP ※时钟RS触发器: 有空翻 ※主从RS触发器: 有约束条件 ※主从JK触发器: 抗干扰能力弱 二、画时序图的步骤 时序图: CP、输入信号、Qn+1之间对应关系的波形图。 ①以CP作用沿为基准划分时间沿到来前为现态,作用沿到来后为次态。 ②每个CP作用沿到来后,根据触发器的逻辑功能确定次态,主从JK在CP下跳沿翻转,维持阻塞D在CP上跳沿翻转,CMOS正边沿型JK和D在CP上跳沿翻转。 ③/SD和/RD不受CP的控制,有异步置1和异步清零的功能。 三、触发器的脉冲工作特性 建立时间tset: CP脉冲有效沿到来之前,输入信号必须保持稳定的时间。 保持时间tH: CP脉冲有效沿到来之后,输入信号必须保持的时间。 传输延迟时间tCPLH和tCPHL: 输出端从0变为1所需延时称为tCPLH。 输出端从1变0所需延时称为tCPHL。 维持时间tCPH和tCPL: CP脉冲高电平必须保持的时间称为tCPH。 CP脉冲低电平必须保持的时间称为tCPL。 第5章时序逻辑电路 5.1时序逻辑电路概述 一、基本概念 ※特点: ①由触发器和组合电路构成具有记忆功能的电路。 ②组合电路至少有一个输出反馈到存储电路的输入端,存储电路的输出至少有一个是组合电路的输入,同其它外输入共同决定电路的输出。 二、分类※ 按触发时间: 同步时序逻辑电路、异步时序逻辑电路。 按电路输出状态: mealy、moore。 按逻辑功能: 寄存器、移位寄存器、计数器、序列信号发生器。 三、描述法※ 输出程、激励程、次态程 5.2同步时序电路的设计 一、设计步骤※ 画状态图或状态表: 确定输入/输出变量,电路状态数目r 状态化简: 合并相同状态。 状态编码: 2k-1 选择触发器: 确定输出程、激励程 画逻辑电路图: 依据输出程、激励程 例子: 例5.2.1、例5.2.2、例5.2.5 5.3同步时序电路的分析 一、分析步骤※ 分析电路的组成 根据逻辑电路图写输出程、激励程 写次态程 根据输出程和次态程列状态转换表 画出状态图 电路功能描述 例子: 例5.3.1、例5.3.2、例5.3.3 5.4寄存器和锁存器 5.5移位寄存器 一、寄存器 (一)数码寄存器 ※含义: 只寄存数码而无移位功能。 (二)移位寄存器 1.单向移位寄存器 ※含义: 在CP作用下,每次将数码右移一位。 2.双向移位寄存器 ※含义: 具有既能左移又能右移逻辑功能的寄存器。 二、锁存器 ※含义: 具有“透明”特性的一种寄存器。 使能状态到来时,输出随输入信号变化。 使能状态结束时,跳变前那一时刻的输入数据被锁存。 5.6计数器 ※计数器: 统计输入脉冲个数的时序逻辑部件。 分类: ①按工作式: 同步计数器、异步计数器。 ②按逻辑功能: 加法计数器、减法计数器、可逆计数器。 ③按进位制: 二进制、十进制、任意进制。 ※模: 脉冲个数的最大值,用N表示。 ※模长: n位二进制计数器模长为2n,最大计数数值为2n-1。 例子: 例5.6.1、5.6.2、5.6.3 1.反馈清零※ 异步清零: M 同步清零: M-1 输入为0000,输出置M(M-1),与非门反馈至清零端。 2.反馈置数※ ①异步置数: M 同步置数: M-1 输入为0000,输出置M(M-1),与非门反馈至置数端。 ②异步置数: 15-M(加法)、255-M(加法) 同步置数: 16-M(加法)、256-M(加法) 输入为15-M/255-M(16-M/256-M),输出置最大值,进位或借位反馈至置数端。 ③异步置数: M(减法) 输入为M,输出置最大值,进位或借位反馈至置数端。 例子: 例5.6.4、5.6.5 5.7序列信号发生器 一、移存器型 ※设计步骤: 确定移存器级数并构建状态图。 列状态转换真值表。 画卡诺图求激励程。 画逻辑电路图。 例子: 例5.7.1、5.7.2 二、计数器型 ※设计步骤: 设计模M计数器。 令计数器每一个状态对应序列信号。 设计组合电路。 例子: 例5.7.3 第8章脉冲电路 8.1概述 一、脉冲信号 ※含义: 不具有连续正弦形状的信号。 特点: 间断、突变、整个波形由若干暂态组成。 ※主要参数: ①下降时间tf: 脉冲下降沿从0.9Vm下降到0.1Vm所需时间。 ②上升时间tr: 脉冲上升沿从0.1Vm上升到0.9Vm所需时间。 ③脉冲幅值Vm: 脉冲电压变化的最大幅度。 ④脉冲宽度tw: 从脉冲前沿0.5Vm起,到脉冲后沿0.5Vm为止的一段时间。 ⑤脉冲期T: 期性重复的脉冲序列中,两个相邻脉冲间的时间间隔。 ⑥占空比q: 脉冲宽度与脉冲期的比值。 q=tw/T 二、脉冲电路 ※含义: 产生、传输、变换和处理脉冲信号的电路。 组成: 开关电路(晶体管或场效应管)和惰性网络(RC或RL)。 运算放大器。 555定时器和RC。 电路: 施密特触发电路、单稳态触发电路、多谐振荡电路。 特点 触发式 备注 施密特 2个稳态 外加触发脉冲 单稳态 1个稳态 1个暂稳态 外加触发脉冲电路 暂稳态持续时间取决于电路本身参数 多谐振荡 无稳态 2个暂稳态 电路 自激产生脉冲波形 比较: 8.5555定时器及其应用 一、555定时器 (一)电路结构 电压比较器、分压器、泄放三极管、RS触发器、输出缓冲反相器。 (二)工作原理※ VI1>VR1且VI2>VR2: TD导通,Vo=0 VI1 TD和Vo输出状态不变 VI1 TD截止,Vo=1 VI1>VR1且VI2 TD截止,Vo=1 二、555定时器构成施密特触发器 (一)工作原理※ 1.输入信号VI从0逐渐升高的过程 VI 输出高电平 VCC/3 保持高电平 VI>2VCC/3: 输出低电平 2.输入信号VI从VI>2VCC

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 大学 数字 逻辑 复习

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

1212中级汽车维修工考试试题三.docx

1212中级汽车维修工考试试题三.docx