Volatile Memories.docx

Volatile Memories.docx

- 文档编号:9715010

- 上传时间:2023-02-06

- 格式:DOCX

- 页数:15

- 大小:539.24KB

Volatile Memories.docx

《Volatile Memories.docx》由会员分享,可在线阅读,更多相关《Volatile Memories.docx(15页珍藏版)》请在冰豆网上搜索。

VolatileMemories

VolatileMemories

1.Introduction

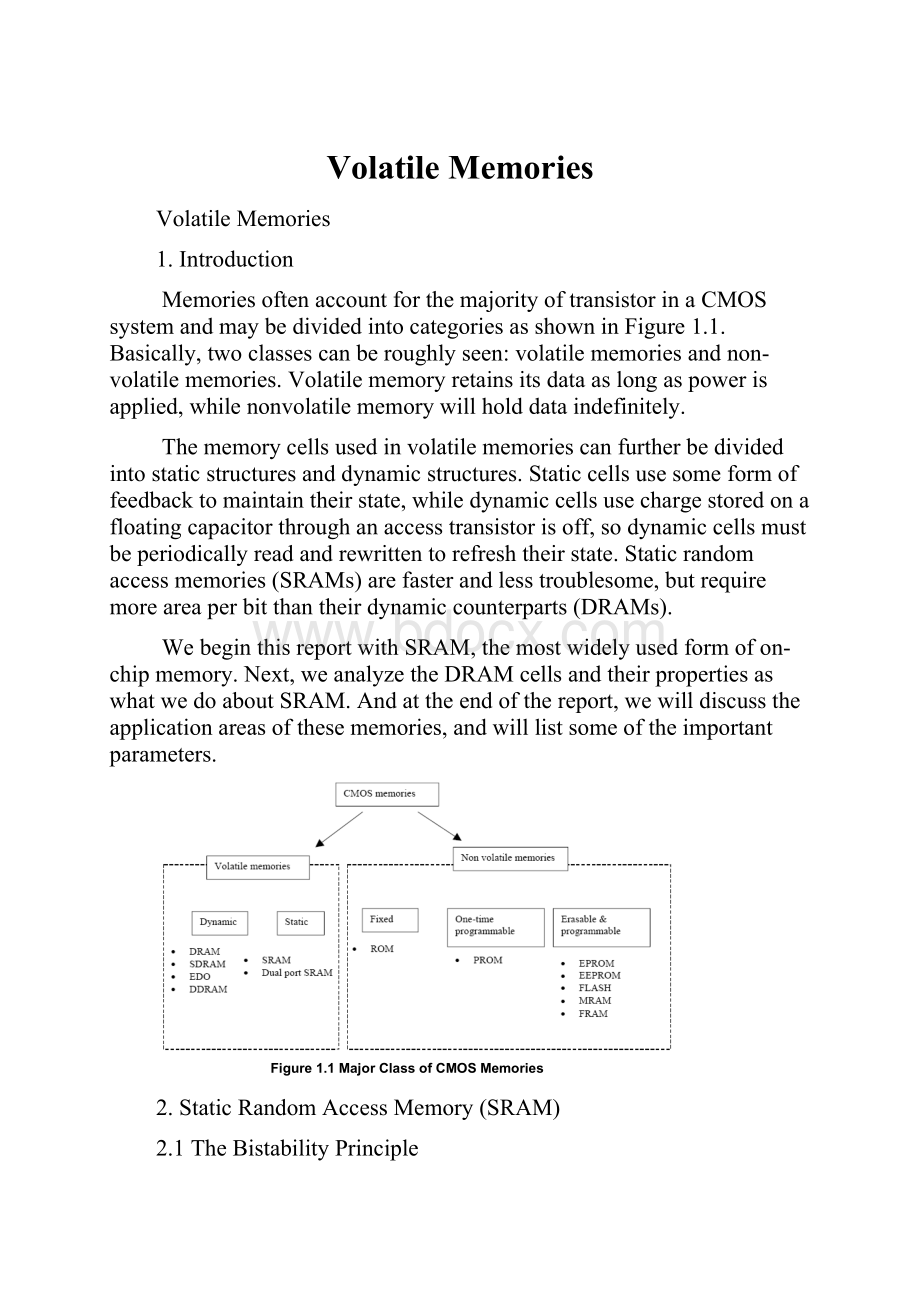

MemoriesoftenaccountforthemajorityoftransistorinaCMOSsystemandmaybedividedintocategoriesasshowninFigure1.1.Basically,twoclassescanberoughlyseen:

volatilememoriesandnon-volatilememories.Volatilememoryretainsitsdataaslongaspowerisapplied,whilenonvolatilememorywillholddataindefinitely.

Thememorycellsusedinvolatilememoriescanfurtherbedividedintostaticstructuresanddynamicstructures.Staticcellsusesomeformoffeedbacktomaintaintheirstate,whiledynamiccellsusechargestoredonafloatingcapacitorthroughanaccesstransistorisoff,sodynamiccellsmustbeperiodicallyreadandrewrittentorefreshtheirstate.Staticrandomaccessmemories(SRAMs)arefasterandlesstroublesome,butrequiremoreareaperbitthantheirdynamiccounterparts(DRAMs).

WebeginthisreportwithSRAM,themostwidelyusedformofon-chipmemory.Next,weanalyzetheDRAMcellsandtheirpropertiesaswhatwedoaboutSRAM.Andattheendofthereport,wewilldiscusstheapplicationareasofthesememories,andwilllistsomeoftheimportantparameters.

2.StaticRandomAccessMemory(SRAM)

2.1TheBistabilityPrinciple

Staticmemoriesusepositivefeedbacktocreateabistablecircuit—acircuithavingtwostablestatesthatrepresent0and1.ThebasicideaisshowninFigure2.1a,whichshowstwoinvertersconnectedincascadealongwithavoltage-transfercharacteristictypicalofsuchacircuit.Theresultingcircuithasonlythreepossibleoperationpoints(A,BandC),asdemonstratedonthecombinedVTC.Itiseasytoprovethevalidityofthefollowingimportantconjecture:

Whenthegainoftheinverterinthetransientregionislargerthan1,AandBaretheonlystableoperationpoints,andCisametastableoperationpoint.

Thetwostableoperationpointscanrepresent0and1inadigitalcircuit,suchasinstaticmemories.

2.2SRAMcell

ThefundamentalbuildingblockofastaticRAMisSRAMcellwhichisintroducedinFigure2.2.Thebistablecircuitisemployedinthis6-TSRAMcell,sothestorageofSRAMisbasedonpositivefeedbackwhichwehavediscussedbefore.Thecellisactivatedbyraisingthewordlineandisreadorwrittenthroughthebitline.

2.2.1OperationofSRAMcell

Tounderstandtheoperationofthememorycell,letusconsiderthereadandwriteoperationsinsequence.Whiledoingso,wealsoderivethetransistor-sizingconstraints.

(a)CMOSSRAMReadOperation

Assumethata1isstoredatQ.Wefurtherassumethatbothbitlinesarepre-chargedto2.5Vbeforethereadoperationisinitiated.Thereadcycleisstartedbyassertingthewordline,enablingbothpasstransistors

and

aftertheinitialwordlinedelay.Duringacorrectreadoperation,thevaluesstoredinQand

aretransferredtothebitlinesbyleavingBLatitspre-chargedvalueandbydischarging

through

~

.ThisisillustratedinFigure2.2.

Considerthe

sideofthecell.ThebitlinecapacitanceforlargermemoriesisinthepFrange.Consequently,thevalueof

staysatthepre-chargedvalue

uponenablingof

thereadoperation(WL→1).ThisseriescombinationofthetwoNMOStransistorspullsdown

towardsground.AsthedifferencebetweenBLand

buildsup,thesenseamplifierisactivatedtoacceleratethereadingprocess.

Theboundaryconstrainsonthedevicesizescanbederivedbysolvingthecurrentequationatthemaximumallowedvalueofthevoltageripple

.Weignorethebodyeffectforsimplicityandwrite:

Thevalueofthevoltagerise

asafunctionofCRfor0.25

technologyisplottedinFigure2.3.Tokeepthenodevoltagefromrisingabovethetransistorthreshold(about0.4V),thecellratiomustbegreaterthan1.2.Forlargememoryarrays,itisdesirabletokeepthecellsizeminimalwhilemaintainingreadstability.

Now,letusdiscussthereasonwhyCRshouldbelargerthan1.2.IfCR<1.2,then

>0.4,then,

willbeonandthevalueofQwillbepulleddowntozerothroughit;However,Qshouldbe1.Thistypeofmalfunctionisfrequentlycalledareadupset.AsillustratedinFigure2.4.Toavoidthismalfunction,acarefulsizingofthetransistorsisnecessary.Apreferredsolutionistominimizethesizeofthepasstransistor,andincreasethewidthoftheNMOSpull-downM5tomeetthestabilityconstraint.

(b)COMSSRAMWriteOperation

Weassumethata1isstoredinthecell(Q=1).A0iswritteninthecellbysetting

to1andBLto0.Duringtheinitiationofawrite,theschematicoftheSRAMcellcanbesimplifiedtothemodelofFigure2.5.Itisreasonabletoassumethatthegatesoftransistors

and

stayat

andGND,respectively,aslongastheswitchinghasnotcommenced.

Notethat

sideofthecellcannotbepulledhighenoughtoensurethewritingof1.Thesizingconstraint,imposedbythereadstability,ensuresthatthisvoltageiskeptbelow0.4V.Therefore,thenewvalueofthecellhastobewrittenthroughtransistor

.

However,acontradictionphenomenonwillappearifthevalueofQisnotpulldownto0quicklywhichisshowninFigure2.6.Atthebeginningofthiswriteoperation(write0intothecell),thevoltageofQ(1isstored)isbiggerthan0.4V,then

isonandpullsthevalueof

downtoground.SowemustmakesurethatthevoltageofQshouldbepulleddownquicklythrough

and

withthevalueofBLis0.

AreliablewritingofthecellisensuredifwecanpullnodeQlowenough—thisis,belowthethresholdvalueofthetransistor

.Theconditionforthistooccurcanbederivedbywritingoutthedccurrentequationsatthedesiredthresholdpoint,asfollows:

Thedependenceof

onPRfora0.25

processisplottedinFigure2.7.ThelowerPR,thelowerthevalueof

.Ifwewishtopullthenodebelow

thepull-upratiohastobebelow1.8.

2.3Summary

WhenanalyzingthetransientbehavioroftheSRAMcell,onerealizesthatthereadoperationisthecriticalone.Itrequiresthe(dis)chargingofthelargebitlinecapacitancethroughthestackofthesmalltransistorsoftheselectedcell.However,thewritetimeisdominatedbythepropagationdelayofthecross-coupleinverterpair,asthedriversthatforceBLand

todesiredvaluescanbelarge.Toacceleratethereadtime,SRAMsusesenseamplifierisactivated,anditquicklydischargesoneofthebitlines.

3.DynamicRandomAccessMemory(DRAM)

3.1ThreeTransistorDynamicMemoryCell

The3TarchitectureDRAMcellisshowninFigure3.1.ThiscellformedthecoreofthefirstpopularMOSsemiconductormemoriessuchasthefirst1-KbitmemoryfromIntel.Whilereplacedbymoreareaefficientcellsintheverylargememoriesoftoday,itisstillthecellofchoiceinmanymemoriesembeddedinapplicationspecificintegratedcircuits.Thiscanbeattributedtoitsrelativesimplicityinbothdesignandoperation.

(a)3TDRAMcellwrite/readoperation

vThecelliswrittentobyplacingtheappropriatedatavalueon

andassertingthewrite-wordline(WWL).

vThedataisretainedaschargeoncapacitance

onceWWLislowered.

vWhenreadingthecell,theread-wordline(RWL)israised.Thestoragetransistor

iseitheronoroffdependinguponthestoredvalue.

vThebitline

iseitherclampedto

withtheaidofaloaddeviceorispre-chargedtoeither

or

;

vTheseriesconnectionof

and

pulls

lowwhena‘1’isstored.And

remainshighintheoppositecase.TheprocessisplottedinFigure3.2.

(b)Propertiesof3TDRAMcell

vIncontrasttotheSRAMcell,noconstraintsexistonthedeviceratios.Thisisacommonpropertyofdynamiccircuits.Thechoiceofdevicesizesissolelybasedonperformanceandreliabilityconsiderations;

vIncontrasttootherDRAMcells,readingthe3Tcellcontentsisnondestructive;

vNospecialprocessstepsareneeded.Thestoragecapacitanceisnothingmorethanthegatecapacitanceofthereadoutdevice,andthismakesthe3Tcellattractiveforembeddedmemoryapplications;

vThevaluestoredonthestoragenodeXwhenwritinga’1’equalsVWWL-

.Thisthresholdlossreducesthecurrentflowingthrough

duringareadoperationandincreasesthereadaccesstime.Topreventthis,somedesignsbootstraptheword-linevoltage,orinotherwords,raiseVWWLtoavaluehigherthan

;

3.2OneTransistorDynamicMemoryCell

Anotherstructurecalledon-transistorDRAMcellcanbeobtainedbyreducingtwotransistorsandsacrificeinsomeofthecellproperties.The1TDRAMcellisundoubtedlythemostpervasivedynamicDRAMcellincommercialmemorydesign.AschematicisshowninFigure3.2.

(a)WriteOperation

vDuringawritecycle,thedatavalueisplacedonthebitlineBL,andthewordlineWLisraised.Dependingonthedatavalue,thecellcapacitanceiseitherchargedordischarged.

vThereisnoanyquestionsduringinwritingone‘0’intoacell,however,writinga‘1’intothecellmayneedmoretimetodiscuss;

v

WecanseethatthevoltageatthenodeXis:

v

Observethatathresholdvoltageislost,whichreducestheavailablecharge.However,thischargelosscanbecircumventedbybootstrappingthewordlinestoavaluehigherthan

;Andinthisreport,whenrestoreda‘1’inthecell,weassumethatthevoltageatnodeXiswith.

(b)ReadOperation

vBeforeareadoperationisperformed,thebitlineispre-chargedtoavoltageVPRE.

vUponassertingthewordline,chargeredistributiontakesplacebetweenthebitlineandstoragecapacitance.

vThisresultsinavoltagechangeonthebitline,thedirectionofwhichdeterminesthevalueofthedatastored.

vAccordingtothecharge-sharingequation,thevoltageswingonthebitlineduringreadingoperationcanbec

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Volatile Memories

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx