FPGA4位十进制频率计.docx

FPGA4位十进制频率计.docx

- 文档编号:9688680

- 上传时间:2023-02-05

- 格式:DOCX

- 页数:11

- 大小:280.47KB

FPGA4位十进制频率计.docx

《FPGA4位十进制频率计.docx》由会员分享,可在线阅读,更多相关《FPGA4位十进制频率计.docx(11页珍藏版)》请在冰豆网上搜索。

FPGA4位十进制频率计

4位十进制频率计

一、设计目的

用VerilogHDL语言设计一个能实现自动测频的4位十进制频率计。

1)测量范围:

1Hz~9999Hz

2)测量的数值通过4个数码管显示

3)频率超过9999Hz时,溢出指示灯亮,可以作为扩大测量范围的接口。

二、设计原理

1、若某一信号在T秒时间里重复变化了N次,则根据频率的定义可知该信号的频率fs为:

fs=N/T。

2、当T=1s时,N就是测得的频率。

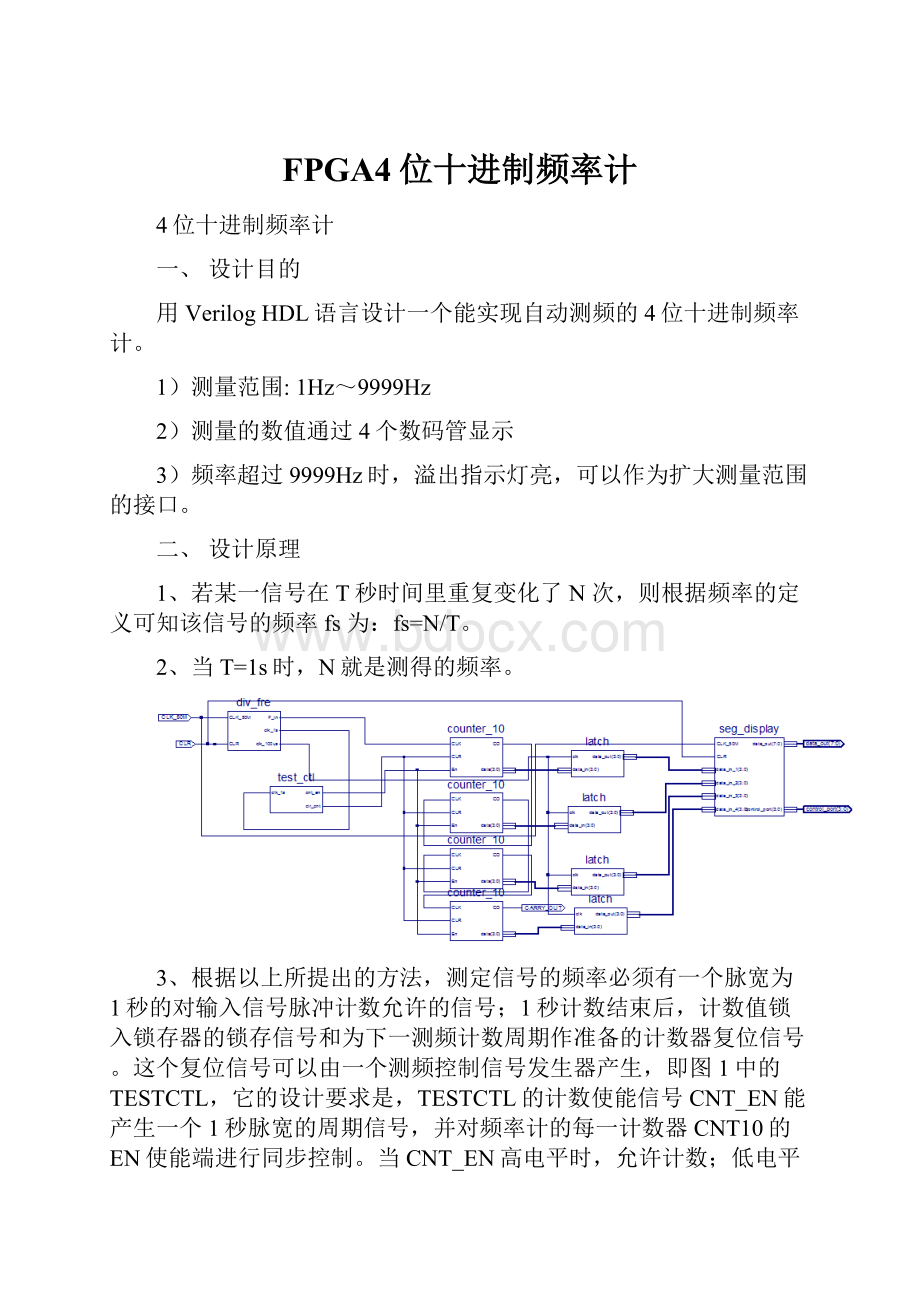

3、根据以上所提出的方法,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器复位信号。

这个复位信号可以由一个测频控制信号发生器产生,即图1中的TESTCTL,它的设计要求是,TESTCTL的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的EN使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,每锁存器进行一次锁存,并由数码管显示计数值。

设置锁存器是为了使显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号之后,必须有一清零信号RST_CNT对计数器进行清零,为下1秒钟的计数操作准备。

图1原理图

三、设计步骤

1、新建cym工程文件。

图2建立工程

由于是用VHDL语言进行设计,所以此处选择类型为HDL。

之后一直点击确认即可。

图3芯片信息配置

由于我们所采用的板子为RCXQ208_V5FPGA开发板,所以配置如图所示。

2、新建各个分模块并输入代码。

图4建立VHDL文件

3、建立顶层文件为原理图型,例化各个模块并连接。

图5建立VHDL文件

4、对设计进行综合,如果出现错误,根据提示改正。

图6综合

黄色感叹符号代表有警告,有些警告可以忽略,绿色小勾表示综合成功。

5、建立测试文件并进行仿真,验证设计。

图7建立激励文件

之后一直点击确认即可。

为了结合我们的下载板子的时钟信号,在测试文件中设置时钟单位为10ns,精度为1ps,如图:

图8设置时钟单位

仿真文件应验证个端口的正确性。

由于时钟单位为10ns,所以CLK_50M每一个仿真时间单位翻转一次即可产生一个50M的时钟信号。

开始时进行一次复位,使各寄存器初值正确。

control_port端为数码管位扫描端,所以其值一直在1110~1101~1011~0111循环。

data_out端为数码管显示的数字对应的七段数码管的二进制数据,它的值可以与control_port端对应到一起观察,转换为对应的十进制数据即是1110、1101、1011、0111对应的data端的信号由0~9循环。

对测试文件进行检查,出现绿色小勾表示无语法错误,可以进行仿真。

图9

6、根据板子锁定引脚,并生成下载文件。

下载板有两个时钟输出引脚,一个为40M的,一个为50M的。

本设计采用的是50M,所以CLK_50M引脚锁定为引脚P80,即net"CLK_50M"loc=p80。

CLR复位端连接一个轻触开关,为P57,即net"CLR"loc=p57。

CARRY_OUT溢出标志端用一个LED灯来表示,net"CARRY_OUT"loc=p22。

下载板数码管引脚图如图所示:

图10数码管端口图

由图可知data端和control_port端的引脚应该分别锁定为:

net"data_out[0]"loc=p102;

net"data_out[1]"loc=p99;

net"data_out[2]"loc=p107;

net"data_out[3]"loc=p109;

net"data_out[4]"loc=p112;

net"data_out[5]"loc=p100;

net"data_out[6]"loc=p106;

net"data_out[7]"loc=p108;

net"control_port[0]"loc=p127;

net"control_port[1]"loc=p128;

net"control_port[2]"loc=p129;

net"control_port[3]"loc=p132;

net"control_port[4]"loc=p120;

net"control_port[5]"loc=p122;

四、仿真结果

1、时钟信号

图11验证CLK信号

由图可知,CLK信号周期为20ns,时钟信号正确。

2、control_port信号

图12control_port信号

由图可知,control_port信号在预料的循环之内,所以正确。

3、data信号

图13data信号第二个扫描周期

图14data信号第三个扫描周期

图15data信号第四个扫描周期

图16data信号第五个扫描周期

由上图综合可知,data信号在预料的变化之内,所以正确。

五、体会

本次设计由于有了上一次跑表的设计,所以有了几分心得。

要做得快了不少,但还是有一定难度。

把难度大的设计分为各个难度较小的模块来设计,本就是我们自顶向下设计的一种重要思想。

该设计就用到了这种思想。

在简化的同时,我们应该确保各个模块的正确性,所以各个模块我们都应测试、仿真之后在综合到一起。

有时候分开各个模块都可以,但是综合在一起就有各种错误出现了。

所以我们在综合代码的时候,一点要小心又小心,确保引脚的对应关系无误。

逻辑顺序无误。

六、代码

1、VerilogHDL代码:

/************************4位十进制计数器***********************

LR(CLR),

.CARRY_OUT(CARRY_OUT),

.CLK_50M(CLK_50M),

.data_out(data_out),

.control_port(control_port)

);

//InitializeInputs

initialbegin

CLK_50M=0;

forever#1CLK_50M=~CLK_50M;

end

initialbegin

CLR=1;

#10CLR=0;

end

endmodule

3、引脚锁定:

net"CLK_50M"loc=p80;

net"CLR"loc=p57;

net"CARRY_OUT"loc=p22;

net"data_out[0]"loc=p102;

net"data_out[1]"loc=p99;

net"data_out[2]"loc=p107;

net"data_out[3]"loc=p109;

net"data_out[4]"loc=p112;

net"data_out[5]"loc=p100;

net"data_out[6]"loc=p106;

net"data_out[7]"loc=p108;

net"control_port[0]"loc=p127;

net"control_port[1]"loc=p128;

net"control_port[2]"loc=p129;

net"control_port[3]"loc=p132;

net"control_port[4]"loc=p120;

net"control_port[5]"loc=p122;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA4 十进制 频率计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx