数字逻辑实验报告2.docx

数字逻辑实验报告2.docx

- 文档编号:9641423

- 上传时间:2023-02-05

- 格式:DOCX

- 页数:6

- 大小:66.10KB

数字逻辑实验报告2.docx

《数字逻辑实验报告2.docx》由会员分享,可在线阅读,更多相关《数字逻辑实验报告2.docx(6页珍藏版)》请在冰豆网上搜索。

数字逻辑实验报告2

大作业2----基于VerilogHDL多功能代码转换电路的设计

13070036

段杰

1.分析逻辑命题

(1)设计需求:

在控制信号(或称操作码)的作用下,将输入的8421码分别转换成余3码、2421码、格雷BCD码

(2)需求分析:

输入端:

输入端:

I

控制元件:

control

输出端:

输出端:

out

报错:

error

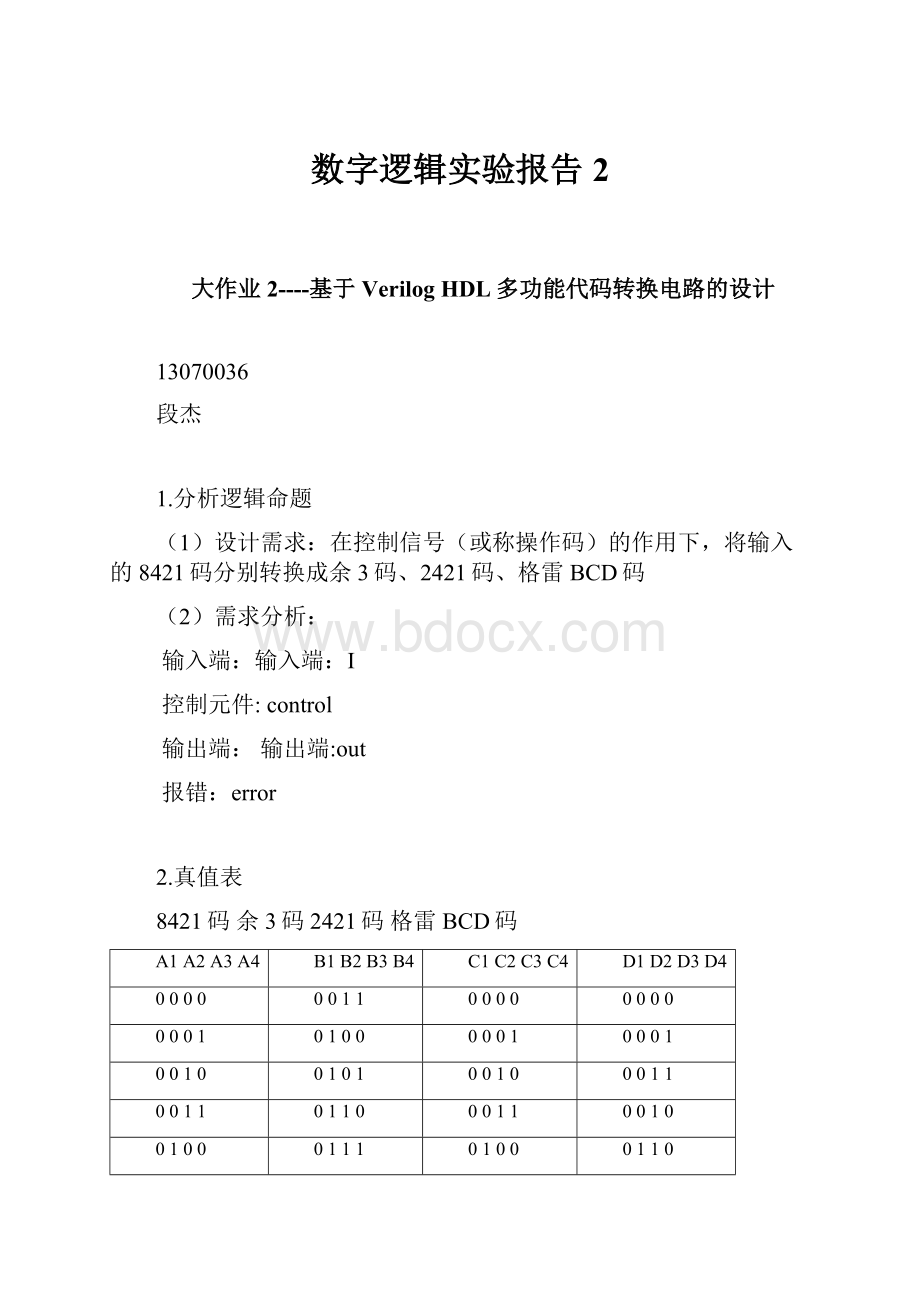

2.真值表

8421码余3码2421码格雷BCD码

A1A2A3A4

B1B2B3B4

C1C2C3C4

D1D2D3D4

0000

0011

0000

0000

0001

0100

0001

0001

0010

0101

0010

0011

0011

0110

0011

0010

0100

0111

0100

0110

0101

1000

1011

0111

0110

1001

1100

0101

0111

1010

1101

0100

1000

1011

1110

1100

1001

1100

1111

1000

1010

D

D

D

1011

D

D

D

1100

D

D

D

1101

D

D

D

1110

D

D

D

1111

D

D

D

3.VerilogHDL代码

modulehomework2(I,control,out,error);

input[3:

0]I;

input[1:

0]control;

output[3:

0]out;

outputerror;

reg[3:

0]out;

regerror;

always@(I)

begin

if(I>4'b1001)error=1;

else

begin

case(control)

2'b00:

out=I+4'b0011;

2'b01:

begin

if(I<4'b0101)out=I;

elseout=I+4'b0110;

end

2'b11:

begin

case(I)

4'b0000:

out=4'b0000;

4'b0001:

out=4'b0001;

4'b0010:

out=4'b0011;

4'b0011:

out=4'b0010;

4'b0100:

out=4'b0110;

4'b0101:

out=4'b0111;

4'b0110:

out=4'b0101;

4'b0111:

out=4'b0100;

4'b1000:

out=4'b1100;

4'b1001:

out=4'b1000;

default:

error=1;

endcase

end

2'b10:

begin

out=0;

error=1;

end

default:

error=1;

endcase

end

end

Endmodule

4.逻辑电路图

5.功能仿真

control:

00

如图所示,当control=00时,即8421转余3码时;

control:

01

当control=01时,即8421转2421码时:

control:

10

error=1

control:

11

8421码转格雷BCD码

6.符号图

7.功能表

control:

00---->out输出余3码

01---->out输出2421码

11---->out输出格雷BCD码

10---->error输出1

I>1001---->error=1

8.小结

基于逻辑门的设计方法与基于HDL设计方法的比较

(1)基于逻辑门的设计方法:

优点:

需要逻辑器件较少

缺点:

设计耗时,适用于小型电路

(2)基于HDL的设计方法:

优点:

设计简单

缺点:

器材较多,适用于大型电路

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 逻辑 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx