数字电路设计数字钟实验设计报告材料.docx

数字电路设计数字钟实验设计报告材料.docx

- 文档编号:9607562

- 上传时间:2023-02-05

- 格式:DOCX

- 页数:9

- 大小:313.73KB

数字电路设计数字钟实验设计报告材料.docx

《数字电路设计数字钟实验设计报告材料.docx》由会员分享,可在线阅读,更多相关《数字电路设计数字钟实验设计报告材料.docx(9页珍藏版)》请在冰豆网上搜索。

数字电路设计数字钟实验设计报告材料

数字钟实验设计报告

数字钟设计

一设计任务

1.基本功能:

以数字形式显示时、分、秒的时间,小时的计时要求为“24翻1”,分和秒的计时要求为60进位;

2.扩展功能:

校时、正点报时及闹时功能;

二电路工作原理及分析

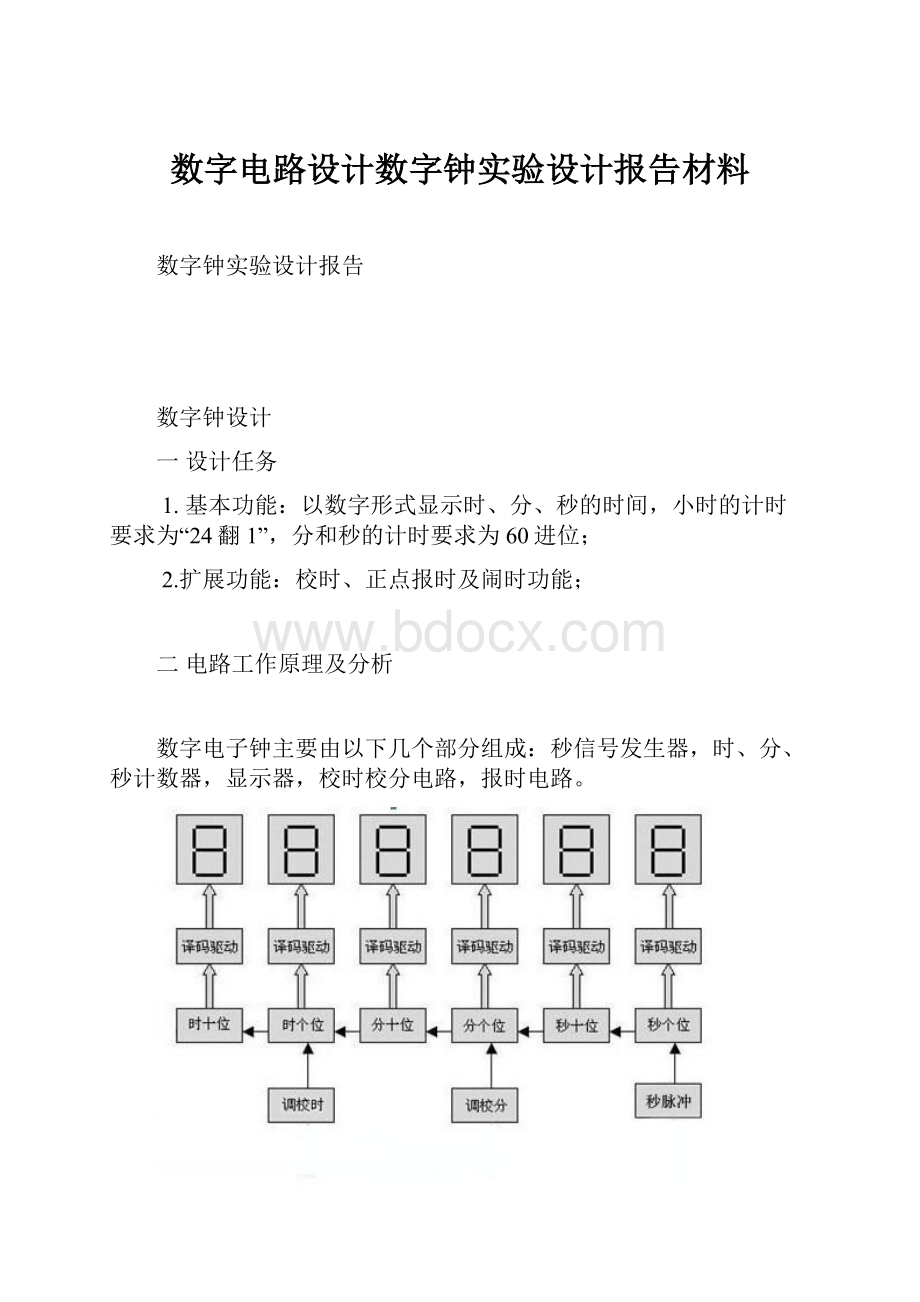

数字电子钟主要由以下几个部分组成:

秒信号发生器,时、分、秒计数器,显示器,校时校分电路,报时电路。

2.1数字钟的基本逻辑功能框图

图1数字钟的基本逻辑功能框图

2.2振荡器的设计

振荡器是数字钟的核心。

振荡器的稳定度及频率的精确度决定了数字钟的准确程度。

通常选用石英晶体构成振荡器电路。

一般来说,振荡的频率越高,计时精度越高。

如果精度要求不高则可以采用由集成逻辑门与R、C组成的时钟源振荡器或集成电路计时器555与R、C组成的多谐振荡器,电路参数如图2所示.接通电源后,电容C1被充电,当Vc上升到2Vcc/3时,使vo为低电平,同时放电三极管T导通,此时电容C1通过R2和T放电,Vc下降。

当Vc下降到Vcc/3时,vo翻转为高电平。

电容C1放电所需时间为

tpL=R2ln2≈0.7R2C1

当放电结束时,T截止,Vcc将通过R1、R2向电容器C1充电,一;Vc由Vcc/3上升到2Vcc/3所需的时间为

tpH=(R1+R2)C1ln2≈0.7(R1+R2)C

当Vc上升到2Vcc/3时,电路又翻转为低电平。

如此周而复始,于是,是在电路的输出端就得到一个周期性的矩形波。

其振荡频率为

f=1/(tpL+tpH)≈1.43/[(R1+2R2)C]

振荡周期:

T=T1+T2=(R1+2R2)C1In2得

R1+2R2=T/C1In2=0.142k

故选定R1=0.1K,R2=0.021

k

图2555振荡器(图中R1,R2值不为实际值)

图3555振荡器产生的波形

2.3时、分、秒计数器电路

时、分、秒计数器电路由秒个位和秒十位,分个位和分十位及时个位和时十位计数器电路构成,其中秒个位和秒十位计数器,分个位和分十位计数器为60进制计数器,而时个位和时十位为24进制计数器。

2.4校时电路

通过开关,触发器,逻辑门组成的校时电路来校时。

校时电路时用来对“时”、“分”、“秒”显示数字进行校对调整的.

三数字电路的设计

3.1计数电路的设计

由2个74LS90计数器和4个74LS290计数器组成的时分秒的计数电路。

3.1.1六十进制计数电路

秒计数和分计数单元为60进制计数器,其输出为8421BCD码。

采用十进制计数器74LS290来实现时间计数单元的计数功能。

由图可知,74LS90为异步清零计数器,有异步清零端12,13脚(高电平有效)。

图4六十进制计数器

(1)秒计数器电路的电路图如图4所示

秒个位计数单元为10进制计数器,无需进制转换,当QAQBQCQD从1001变成0000时,U1向U3的输入端发出一个脉冲信号,使秒十位进1位。

秒十位计数单元为6进制,当QAQBQCQD变成0110时,通过与QBQC相连的导线,给U3两个清零端一个信号,把它的两个清零端都变成1,计数器的输出被置零,跳过0110到1111的状态,又从0000开始,如此重复,十位和个位合起来就是60进制。

(2)分计数器

分的个位和十位计数单元的状态转换和秒的是一样的,只是它要把进位信号传输给时的个位计数单元,电路图如图4所示

3.1.2二十四进制计数器电路

时计数单元为24进制计数器,其输出为8421BCD码。

采用十进制计数器74LS90来实现时间计数单元的计数功能。

时计数器电路的电路图如图5所示

图5二十四进制计数器

当“时”十位的QAQBQCQD为0000或0001时,“时”的个位计数单元是十进制计数器,当个位的QAQBQCQD到1010时,通过与非门使得个位74LS90上的清零端为0,则计数器的输出直接置零,从0000开始。

当十位的QAQBQCQD为0010时,通过与非门使得该74LS90的清零端为0,“时”的十位又重新从0000开始,此时的个位计数单元变成4进制,即当个位计数单元的QAQBQCQD为0100时,就要又从0000开始计数,这样就实现了“时”24进制的计数。

3.2校时电路的设计

数字钟应具有分校正和时校正功能,因此,应截断分个位和时个位的直接计数通路,并采用正常计时信号与校正信号可以随时切换的电路接入其中。

如图6所示,当开关J1按下时,直接给分个位计数器一个脉冲信号,使分计数器进1位,同时不影响数字钟的运行。

同理,由J2对时计数器进行校对。

图6校时校分电路

3.3整点报时设计

仿广播电台正点报时电路的功能要求时:

每当数字钟计时快要到正点时发出声响,通常按照4低音1高音的顺序发出间断声响,以最后一声高音结束的时刻

是整点时刻。

每当数字钟计时快要到正点时发出声响,按照4低音1高音的频率发出间

断声响,前4低音声响频率为500HZ,后1高音声响频率为1000HZ。

并以最后一

声高音结束的时刻为正点时刻。

本设计中,报时电路采用TTL与非门。

报时电路如图1.5所示。

4声低音分别发生在59分51秒、53秒、55秒及57秒,最后一声高音发生在59分59秒,声响均持续1秒。

如表1.2所示。

由表可得式1.1。

只有当分十位的Q2M2Q0M2=11,分个位的Q3M1Q0M1=11,秒个位的Q2S2Q0S=11及秒个位的Q0S1=1时,音响电路才能工作。

3.4报时电路的安装与调试

按照原理图及实物连线图接线。

报时音响电路采用三极管3DG130来推动喇叭。

报时所需的500Hz和1000Hz音频信号,分别取分频器的500Hz输出端和1000Hz输出端。

四主要芯片的技术参数

4.174LS90芯片

74LS90芯片结构及引脚分布如图7所示,74LS90计数器是一种中规模的二一五进制计数器。

它由四个主从JK触发器和一些附加门电路组成,整个电路可分两部分,其中FA触发器构成一位二进制计数器;FD、FC、FB构成异步五进制计数器,在74LS90计数器电路中,设有专用置“0”端R1、R2和置位(置“9”)端S1、S2。

图774LS90芯片

4.274LS290芯片

74LS190芯片的管脚分布如图8所示,其中,R9

(1)、R9

(2)称为置“9”端,R0

(1)、R0

(2)称为置“0”端;A、B端为计数时钟输入端,QAQBQCQD为输出端,NC表示空脚。

74LS290具有以下功能:

置“9”功能:

当R9

(1)=R9

(2)=1时,不论其他输入端状态如何,计数器输出QAQBQCQD=1001,而1001(2进制)=9(10进制),故又称为异步置数功能。

置“0”功能:

当R9

(1)和R9

(2)不全为1,并且R0

(1)=R0

(2)=1时,不论其他输入端状态如何,计数器输出QAQBQCQD=0000,故又称为异步清零功能或复位功能。

计数功能:

当R9

(1)和R9

(2)不全为1,并且R0

(1)和R0

(2)不全为1时,输入计数脉冲,计数器开始计数。

图874LS290芯片

五心得体会

通过这次综合试验设计,大大提高了我分析问题的能力,同时提高了运用电工领域有关的软件进行电路模拟仿真的能力,将自己在课堂上学到的数电知识得到充分发挥,解决了很多问题,同时学到了很多元件和芯片的各种用途及性能,从中学到了很多书上没有明白的问题

本次的课程设计,是对所学的数电知识的一次综合应用,既考验了我的知识掌握程度,也锻炼了我的动手能力。

在此过程中,我学到很多新知识,对电工电子课程的学习也更有兴趣了。

虽然此次课程设计花费了一番功夫,却让我收获了很多,让我知道了学无止境,永远不能满足现有的知识,人生就像在爬山,一座山峰的后面还有更高山峰在等着你。

在这次数字电子钟课程设计中,也非常感谢同学的帮助!

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电路 设计 数字 实验设计 报告 材料

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《Java程序设计》考试大纲及样题试行.docx

《Java程序设计》考试大纲及样题试行.docx