数字电路小系统设计实验.docx

数字电路小系统设计实验.docx

- 文档编号:9467413

- 上传时间:2023-02-04

- 格式:DOCX

- 页数:17

- 大小:175.86KB

数字电路小系统设计实验.docx

《数字电路小系统设计实验.docx》由会员分享,可在线阅读,更多相关《数字电路小系统设计实验.docx(17页珍藏版)》请在冰豆网上搜索。

数字电路小系统设计实验

实验数字电路小系统设计(6学时分2次完成)

钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能,在定时控制、定时检测等方面也有广泛应用。

一、实验目的

设计一个包含脉冲波形产生、计数、译码、显示及控制逻辑等部件的数字,并在面包板上实现。

二、实验思路和实验前准备

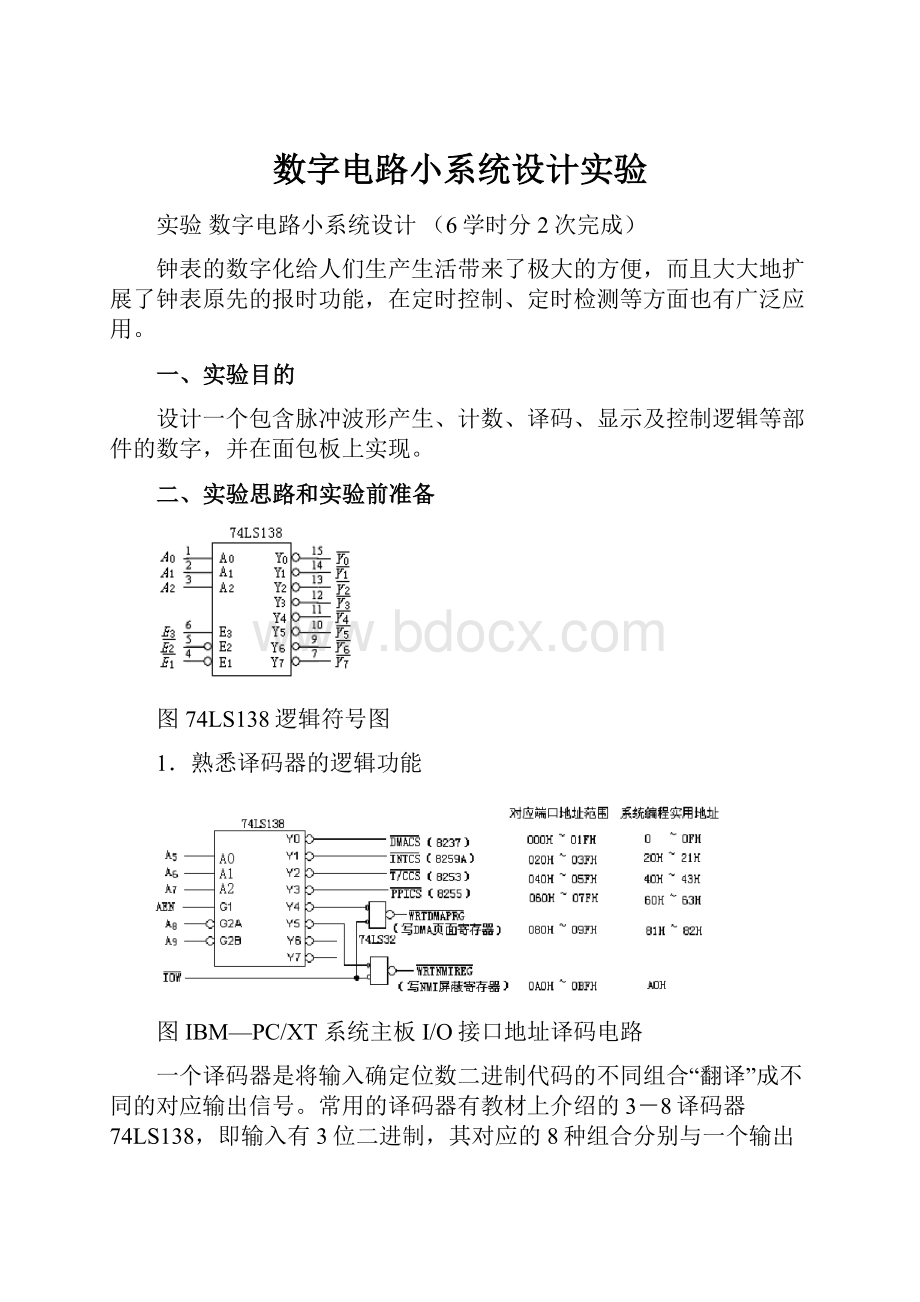

图74LS138逻辑符号图

1.熟悉译码器的逻辑功能

图IBM—PC/XT系统主板I/O接口地址译码电路

一个译码器是将输入确定位数二进制代码的不同组合“翻译”成不同的对应输出信号。

常用的译码器有教材上介绍的3-8译码器74LS138,即输入有3位二进制,其对应的8种组合分别与一个输出对应,其逻辑符号如图。

当所有74LS138的输入控制端有效时,输出与输入最小项的对应关系是

(i=0,1,…7)。

因此教材中已经介绍了它可以实现多输出逻辑函数。

但在数字系统的设计中,译码器的另一个更为重要的作用是地址译码,也就是说,译码器将A0、A1、A2输入的三位地址“翻译”成8个输出信号,A0、A1、A2的一个确定值仅对应

有一个输出为低电平有效。

一般在数字计算机系统中,译码器的这8个输出信号分别接到其它器件的片选端

(ChipSelect),其上的横线代表片选信号是低电平有效,即低电平选中该芯片,它就可以与计算机通信数据。

因此74LS138的8个输出最多可以连接8个计算机外设

接口,而任一时间最多只选中一个工作。

图就是早期的PC计算机使用74LS138译码器构成计算机中DMA控制器8237、中断控制器8259A、计数/定时器T/C(8253)、并行可编程接口PPI(8255A)、DMA页面寄存器及NMI屏蔽寄存器的片选或控制端。

根据图中连接方法,可得到各芯片或寄存器的地址空间如图右面所列。

在信号AEN=1时,大家分析图中所标的各个芯片的地址范围是否正确?

这一部分在学习微型计算机原理时会有更深刻的体会。

译码器还有许多其它的型号,与集成逻辑门中介绍的方法一样,可以在丰富的网络资源中得到找到需要的相关信息。

另外,在实验前,有必要先介绍一下器件符号的概念,对于同一个器件的逻辑符号图或引脚图,不同的器件手册或教材使用的引脚符号和表示形式都不一样,也许大家在学习过程中已经注意到这一点。

为了与教材保持一致,我们对逻辑符号图进行规范,即逻辑符号框图内所有变量均为正逻辑(即框内符号上没有非号),逻辑符号框图外输入端的小圆圈表示该输入控制端为低电平有效,而输出端的小圆圈表示反码输出。

即小圆圈实现了逻辑非运算,那么逻辑符号框图外对应的每个引脚的符号或变量名就默认为:

当逻辑符号框图外引脚没有小圆圈时,那么该引脚对应的变量名与框图内符号一样,但用斜体表示是变量。

例如,图中的A0、A1、A2和E3;当框图外引脚有小圆圈时,那么该引脚对应的变量名是在框内符号上冠一非号,例如,图中的

、

、…

、

和

。

以后框图外引脚对应的变量名不再标出,但使用时按照以上规定。

但要注意这只是教材的规定,并不是标准,其它的参考书或器件手册中的标法可能会五花八门。

因此,使用器件时,大家学会使用器件的方法是最重要的,这样面对不断出现的新器件才不会束手无策。

通过大量的使用集成器件,大家会发现使用中小规模的集成器件只要了解以下几点即可:

1)当输入信号端有小圆圈(一般是控制输入端),表示该端为低电平有效,当输出信

号端有小圆圈,表示器件工作时该端输出低电平有效;

2)多控制端芯片只有当所有控制端同时有效时,才可以实现芯片的逻辑功能;

3)如果资料中给出了器件的功能表,要学会看对应的功能表,器件功能以功能表为准;

4)资料也是经常会有出错的情况,遇到问题可以通过实验来最后验证。

2.集成计数器

计数器的功能是累计输入脉冲个数。

它是数字系统中使用最为广泛的时序逻辑部件。

计数器的种类非常繁多,为了降低集成电路的价格,所以厂家会批量生产通用的十六进制(二进制)和十进制计数器。

虽然有通用的十六进制和十进制计数器,但实际应用中时常会用到其它进制计数,比如,数字钟的24和60进制等,对于其它进制计数器的设计,可以通过教材中介绍的使用反馈的方法来实现。

例如,现有一块十六进制计数器74LS393,其功能如表,管脚符号如图。

使用74LS393的清0端MR端作为反馈清0,实现十进制计数器如图所示。

图给出了24进制计数器设计举例。

3.LED(LightEmittingDiode)显示器(七段数码管)

LED显示器在许多的数字系统中作为显示输出设备,使用非常广泛。

它的结构是由发光二极管构成如图所示的a、b、c、d、e、f和g七段,并由此得名,实际上每个LED还有一个发光段dp,一般用于表示小数点,所以也有少数的资料将LED称为八段数码管。

LED内部的所有发光二极管有共阴极接法和共阳极接法两种,即将LED内部所有二极管阴极或阳极接在一起并通过com引脚引出,并将每一发光段的另一端分别引出到对应的引脚,LED的引脚排列一般如图所示,使用时以具体型号的LED资料为依据。

通过点亮不同的LED字段,可显示数字0,1,┅,9和A,b,C,d,E,F等不同的字符及自定义一些段发光代表简单符号。

图为LED的使用举例,图中的LED为共阳极接法,因此,com端接5V电压,其它引脚端通过限流电阻接到锁存器74LS373的输出,当各段输入端为逻辑“1”,对应的LED不亮;各段输入端为逻辑“0”时,对应LED才发亮。

使用时要根据LED正常发光需要的电流参数估算限流电阻取值。

电阻取值越小,电流大,LED会更亮,但要注意长时间过热使用烧坏LED。

在实验中当共阳极LED与74LS47译码器配合使用时,因为

不是每个引脚接限流电阻,故需要在总回路中限流,应在com端图LED结构和引脚

和Vcc之间串接1个470Ω限流电阻,如图所示

LED多数情况用于显示十进制数字,要将0~9的数字用7段显示,必须将数字转换为LED对应七段码的信息,比如,要显示“0”,就是让a、b、c、d、e和f段发光,显示“1”,

让b和c段发光,等等如表所示。

然后根据LED是共阴极还是共阳极接法确定LED各输入端应接逻辑1还是逻辑0,如果是共阳接法,要显示“0”时,a、b、c、d、e和f段就要输入逻辑0,共阴极接法则恰巧相反。

也就是说,对于共阴极和共阳极两种不同的接法,显示同一个字符时,对应的显示段码是不同的,互为反码。

表列出了这两种接法下的字形段码关系表。

表中的段码数字是以LED的8段与二进制字节数以下列对应关系为前提得到的:

比如为了显示“0”,对应共阴极应该使D7D6D5D4D3D2D1D0=00111111B,即3FH;对共阳极应该使D7D6D5D4D3D2D1D0=B,即C0H。

如表所示,从表中可以看出,对于同一个显示字符,共阴极和共阳极的七段码互为反码。

将待显示内容“翻译”为LED段码的过程,可以由软件查表方法实现译码,这在学习微型计算机有关课程时会使用。

也可以采用专用芯片,比如,带驱动的LED七段译码器74LS47及74LS48、74LS49等,依靠硬件实现译码。

表7段LED显示器字符段码表

显示字符

共阴极段码

共阳极段码

显示字符

共阴极段码

共阳极段码

0

3FH

C0H

C

39H

C6H

1

06H

F9H

d

5EH

A1H

2

5BH

A4H

E

79H

86H

3

4FH

B0H

F

71H

8EH

4

66H

99H

·

80H

7FH

5

6DH

92H

P

73H

82H

6

7DH

82H

U

3EH

C1H

7

07H

F8H

T

31H

CEH

8

7FH

80H

Y

6EH

91H

9

6FH

90H

8.

FFH

00H

A

77H

88H

“灭”

00H

FFH

b

7CH

83H

┇自定义

┇

┇

4.七段译码器

七段译码器也称为BCD—七段显示译码器,顾名思义,它是将输入的BCD码翻译成LED显示该BCD的七段信息输出。

七段译码器有输出低电平有效和高电平有效的多种型号。

当选用的LED是共阳极接法时,应使用低电平输出有效的七段译码器,如7446和7447等;当选用的LED是共阴极接法时,应使用高电平输出有效的七段译码器,如7448和7449(OC输出)等。

七段译码器驱动LED的原理如图所示,图中的“?

”是表示LED和七段译码器之间一般还要接限流电阻或其它匹配电路,或者驱动译码器是OC输出,需要接上拉电阻。

七段译码器内部一般包含了LED的驱动电路,驱动共阳极LED的译码器(输出低电平对应段亮)驱动电流一般较大(灌电流),如果该电流与LED器件的正常工作电流近似,那么可以直接驱动LED,如果驱动电流大于LED正常电流许多,那么两者之间要加限流电阻,根据LED的参数估算限流电阻的大小;如果七段译码器驱动能力不够大,特别是驱动共阴极LED时,可以在两者之间加适当的上拉电阻,比如7448驱动共阴极的BS201时,要LED有正常显示亮度就要加上拉电阻。

LED也有多种型号,如BS211、BS212、BS213为共阳型;BS201、BS202、BS203为共阴型。

每种型号的LED厂家手册都提供了详细功能及参数介绍(可以通过资料或网络查找),比如,七段共阴磷砷化镓显示器BS201主要参数:

1)消耗功率PM=150mW

2)最大工作电流IFM=100mA

3)正常工作电流IF=40mA

4)正向压降VF≤

5)发红色光

6)BS201燃亮电压为5v

共阴极BS202LED的PM=300mW,IFM=200mA,IF=60mA,VF≤,VR≥5V,发红光。

实验中采用七段共阳极数码管(TFK-433)和74LS47七段驱动器,查找它们的详细资料,分析两者之间应如何连接?

画出连线图。

5.多个LED的动态扫描显示

在许多实际的系统中,经常需要多个LED显示系统的信息,比如,数字钟实验要显示时、分和秒信息,就必须要6个LED,对这些LED的控制也可以和上面一位LED显示器一样,采用6个七段译码器驱动每一个LED,并使所有LED的公共端始终接有效信号,即共阴极LED公共端接地,共阳极LED公共端接电源。

这种LED显示方式称为静态显示方式。

采用静态方式,LED亮度高,但这是以复杂硬件驱动电路作为代价的,硬件成本高。

图多位LED动态显示电路

因此,在实际使用时,特别是有微处理器的系统中,如果用多位的LED显示,一般采取动态扫描方式、分时循环显示,即多个发光管轮流交替点亮。

这种方式的依据是利用人眼的滞留现象,只要在1秒内一个发光管亮24次以上,每次点亮时间维持2ms以上,则人眼感觉不到闪烁,宏观上仍可看到多位LED同时显示的效果。

动态显示可以简化硬件、降低成本、减小功耗。

图是一个6位LED动态显示电路,段驱动器输出LED字符7段代码信息,位驱动器输出6个LED的位选信号,即分时使Q0~Q5轮流有效,使得LED0~LED5轮流显示。

6.熟悉计数器、七段译码器和LED显示器逻辑功能

按图连线,用74LS393实现一位十进制计数器;由七段共阳极数码管(TFK-433)显示计数结果,其引脚排列同图;数码管由BCD—七段显示译码器(74LS47)驱动,其引脚排列如

图所示。

TFK-433和74LS47之间按实验前准备分析的方式连接。

一位十进制计数器的译码、显示电路原理图如图所示,

搭接电路并实验。

ET-3200A数字学习机上的1Hz信号可以作为计数输入,或者用555定时器构成1Hz信号作为计数器时钟输入。

7.验证人眼的滞留现象

首先,将ET-3200A学习机上的1Hz时钟信号接到逻辑显示器的L4端,观察L4的显示效果;然后,将1KHz时钟信号接到逻辑显示器的L4端,观察L4的显示效果;最后将100KHz时钟信号接到逻辑显示器的L4端,观察L4的显示效果。

记录观察的到现象,分析原因。

8.555定时器组成的多谐振荡器

555定时器是一种模拟和数字电路相混合的集成电路。

它结构简单、性能可靠、使用灵活,通过外接少量的电阻和电容元件即可组成多种波形发生器,广泛应用于定时延迟控制电路、报警、检测、自控及家用电器等。

555定时器有TTL和CMOS两种结构类型,多种型号。

该实验使用5G555构成多谐振荡器。

5G555的功能如表所示,引脚排列如图所示。

电路芯片各引脚功能为:

1脚——(CND)地

2脚——(

)低电平触发(<十

)

3脚——(OUT)输出端

4脚——(

)复位端(不用时接Vcc)

5脚——(C-U)电压控制端,可改变上、下触发电位,不使用时通过电容接到地。

6脚——(TH)高电平触发(>十

)

7脚——(DIS)放电端

8脚——(Vcc)电源端(Vcc=5V~18V)

表5G555功能表

TH

OUT

DIS

X

X

L

L

导通

H

L

导通

H

不变

不变

X

H

H

截止

由功能表可见,555的输出逻辑主要由以下3个引脚控制

1)引脚4——复位端

为0则输出OUT为逻辑0;

2)引脚6——高电平触发TH>十

,DIS放电管导通,输出OUT为0;

3)引脚2——低触发电平

<十

,DIS放电管截止,输出OUT为1。

由555定时器构成的多谐振荡器电路如图所示,所产生的信号振荡频率为:

f=1/(T1+T2)=(R1+2R2)C

试选择电路的R1、R2和C参数,若R1=20KΩ、R2=62KΩ、C=10uF和C=时,计算输出信号的周期、频率各为多少?

VDDuC

R1

uO

R2t

uOt1t2t3t4

uC

CT1T2

t

(a)(b)

图555定时器构成的多谐振荡器及工作波形图

(a)电路图(b)波形图

9.数字钟结构框图

图数字钟结构框图

在进行一个设计之前首先要搞清楚命题要求,划分系统,给出设计框图。

对于一个简单的数字钟系统,其结构一般如图所示,主要包括时间基准电路、计数器电路、控制电路、译码和显示电路。

其中的控制逻辑电路是比较灵活多样的,不断完善它可以增强数字钟的功能。

时基电路可以由石英晶体振荡电路构成,如果晶振频率为1MHz,经过6次十分频就可以得到秒脉冲信号;也可以用5G555多谐振荡器组成。

计数器实现时分秒计时,秒和分采用60进制计数,时采用24进制计数。

可以由多片中规模集成计数器实现。

译码电路可以由七段译码器完成,显示由6个LED构成。

控制电路由数字钟功能确定,功能越多控制电路当然就越复杂。

图手动校“分”电路

比如,要求数字钟实现校时功能,那么就需要在“时”“分”“秒”的计数输入端加入校时控制电路,图为一个手动校“分”的常用例子,当控制开关K在1位置,电路处于正常计时状态,当控制开关K在2位置,通过手动单次脉冲开关进行校分。

校时也可以通过同样的方法实现。

在实验中用手动校“秒”就没有多大意义了。

三、实验内容和步骤

根据前边知识的预习及准备,要求画出设计原理图及实验连线图,用开放实验下发的元器件和面包板,设计一个包含脉冲波形产生的计数、译码、显示及控制逻辑等部件的数字电子钟系统,在面包板上实现。

根据设计的数字钟电路连线图,课外搭接好电路。

1.前3学时内完成以下单元电路调试和总体电路联调:

1)用555定时器设计一个频率符合要求的脉冲波形产生电路;

2)用74LS393和74LS08设计一个二位计数器电路;

3)用74LS47和LED显示器设计一个二位译码、显示电路;

4)完成二位计数、译码、显示电路;

5)组合完成一个含有计数、译码、显示及控制逻辑的数字钟系统。

2.后3学时内完成相关电路波形的参数测试和数据分析:

1)更换脉冲波形产生电路中的电容,用LED指示灯观测输出频率的变化,并分析RC与频率变化的关系;

2)用双踪示波器测量555定时器组成的脉冲波形产生电路中,电容C上的充、放电电压Vc波形与输出电压Vo波形之间的相位关系,正确标出波形幅值、周期和脉宽;将测量得到的数据与理论计算值比较,分析误差。

3)用双踪示波器观测74LS393计数器CP与各Q端波形的相位关系,即从0000状态开始,正确画出CP与Q3、Q2、Q1、Q0的十进制波形图。

四、实验报告:

实验题目:

数字电路小系统设计

1.设计报告:

1)目的、任务及要求;

2)电路组成及工作原理。

2.调试报告:

1)所用仪器及实验器材;

2)实验电路管脚连线图;

3)调试方法及步骤(单元调试,总体联调);

4)脉冲波形产生电路参数(R1、R2、C)计算及元件选取;

5)RC的不同组合与频率的关系;

6)正确记录并分析如下各点波形:

(1)用示波器测量脉冲波形产生电路中,电容C上的充、放电电压Vc波形与输出电压Vo波形之间的相位关系,正确标出波形幅值、周期和脉宽;并将测量得到的实验数据与理论计算值比较,分析误差。

(2)用示波器观测计数器CP与各Q端波形的相位关系,即从0000状态开始,画出CP与Q3、Q2、Q1、Q0的十进制波形图。

3.总结报告:

1)总结单元电路调试、总体电路联调方法;

2)在不损坏元器件且学有余力的情况下,调试中同学可以互设故障,相互排除,交流讨论,激发学习兴趣,提高分析和解决实际问题的能力,把所得收获充实到报告中。

3)附上实验原始记录,写出存在问题和建议。

五、实验设备

双踪示波器、函数发生器、数字学习机、开放实验面包板、万用表、双路直流稳压电源。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电路 系统 设计 实验

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

1212中级汽车维修工考试试题三.docx

1212中级汽车维修工考试试题三.docx