DSPTMS320C54X系列芯片结构与基本特征精.docx

DSPTMS320C54X系列芯片结构与基本特征精.docx

- 文档编号:9442692

- 上传时间:2023-02-04

- 格式:DOCX

- 页数:17

- 大小:348.38KB

DSPTMS320C54X系列芯片结构与基本特征精.docx

《DSPTMS320C54X系列芯片结构与基本特征精.docx》由会员分享,可在线阅读,更多相关《DSPTMS320C54X系列芯片结构与基本特征精.docx(17页珍藏版)》请在冰豆网上搜索。

DSPTMS320C54X系列芯片结构与基本特征精

TMS32QC54x的

基本结构和特征

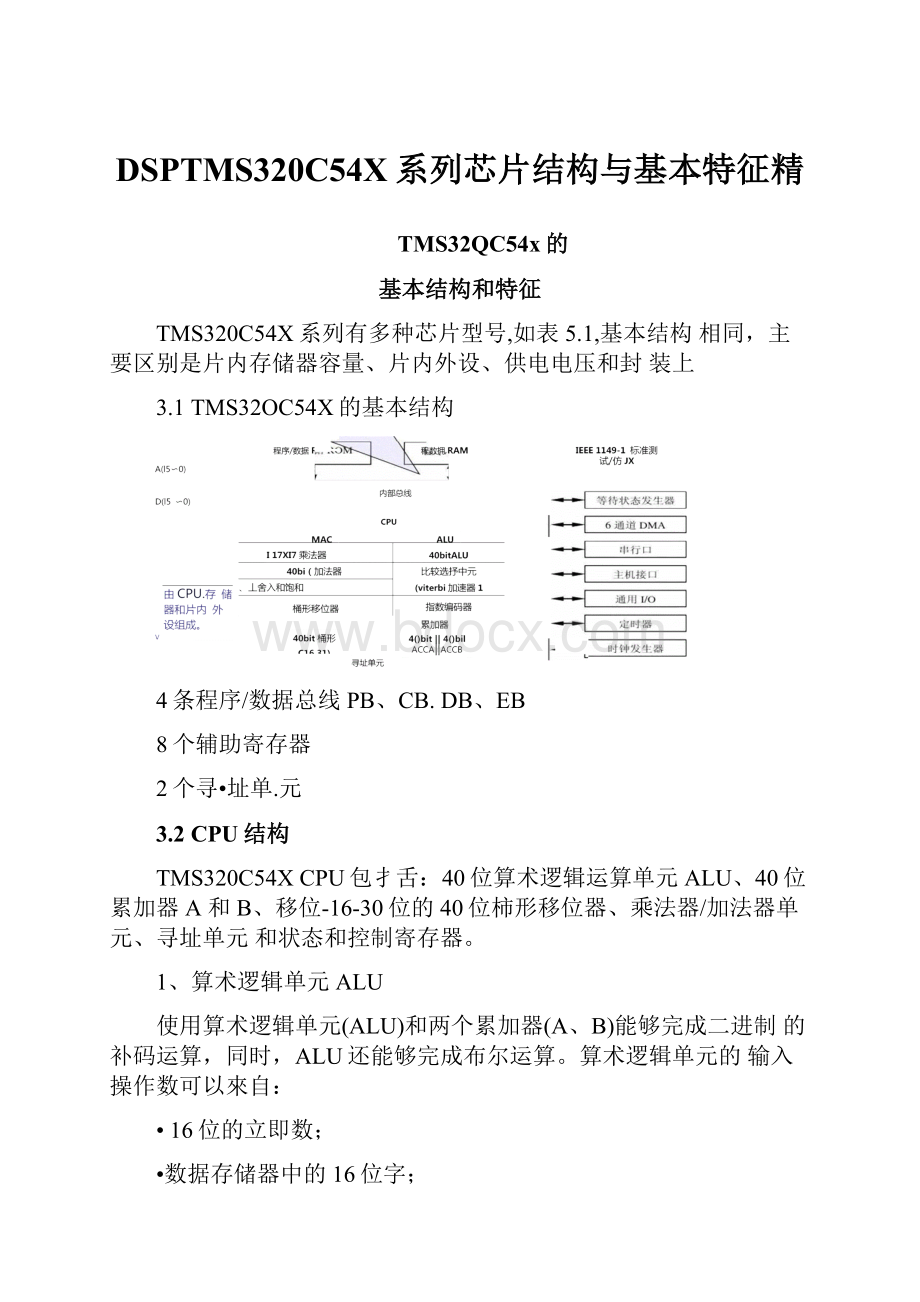

TMS320C54X系列有多种芯片型号,如表5.1,基本结构相同,主要区别是片内存储器容量、片内外设、供电电压和封装上

3.1TMS32OC54X的基本结构

4条程序/数据总线PB、CB.DB、EB

8个辅助寄存器

2个寻•址单.元

3.2CPU结构

TMS320C54XCPU包扌舌:

40位算术逻辑运算单元ALU、40位累加器A和B、移位-16-30位的40位柿形移位器、乘法器/加法器单元、寻址单元和状态和控制寄存器。

1、算术逻辑单元ALU

使用算术逻辑单元(ALU)和两个累加器(A、B)能够完成二进制的补码运算,同时,ALU还能够完成布尔运算。

算术逻辑单元的输入操作数可以來自:

•16位的立即数;

•数据存储器中的16位字;

•暂存器T中的16位字;

•数据存储器屮读出的2个16位字;

•累加器A或B中的40位数;

•移位寄存器的输出。

•即町完成双16位运算(C16=l),也町进行40位运算。

2、比较选择存储单元CSSU

通信领域常常用到维持比(Viterbi)算法,该算法需要完成大量的加法/比较/选择(ACS)运算。

CSSU单元支持各种Viterbi算法,其中加法由ALU单元完成,将ST1中的C16置1,所有的双字指令都会变成双16位算术运算指令,这样ALU就可以在一个机器周期内完成两个16位数的加/减法运算,其结果分别存放在累加器的高16位和低16位屮。

CSSU可以垠人限度地完成累加器高字与低字的比较操作,即选择累加器中较人的字,并存储在数据存储器中,且不改变状态寄存器ST0中的测试/控制位TC字段和状态转移寄存器TRN的值。

CSSU利用优化的片内硬件加速Viterbi的蝶形运算。

3、指数编码器

指数编码器是一个专用硕件,它支持单周期指令EXP。

它可以求出累加器中的指数值,并以二进制补码形式存放于T中。

用EXP和NORM指令可以对累加器中的内容归一化,完成定点数和浮点数之间的转换。

4、累加器A和B

累加器A和B都可以配置成乘法器/加法器或ALU的日的寄存器。

40位的累加器A、B可以分成三部分分别映射在数据存储空间的0页:

39-3231-1615-0

AG

AH

AL

39—3231—1615-0

AG

AH

AL

A

B

安全位高字低字

AL:

8H,AH:

9H,AG:

AH

BL:

BH,BH:

CH,BG:

DH

累加器的作用:

累加器A和B都可以配置成乘法器/加法器或ALU的FI的寄存器。

提供ALU的另一个输入。

可作为乘法器(只有A)/加法器的输入、通过桶形移位器实现移位和循环移位。

5、桶形移位器

40位桶形移位器的输入端來自:

©DB,取得16位输入数据;

2DB和CB,取得32位输入数据;

340位累加器A或B。

40位桶形移位器的输出端接至:

1ALU的一个输入端;

2CSSU单元输入端。

桶形移位器(40位)用来为输入的数据进行定标,可以进行以下操作:

1ALU运算前,对來自数据存储器的操作数或者累加器的值进行定

标;

2对累加器的值进行算术或逻辑移位;

3对累加器归一化处理;

4对累加器的值存储到数据存储器Z前进行定标。

桶形移位寄存器的控制:

1操作数带符号位/不带符号位扩展控制:

ST1寄存器的SXM位:

当SXM=1时,执行符号位扩展。

2移位位数的控制:

指令中的移位数就是移位的位数。

正值表示左移,负值表示右移。

移位数可以用以下方式定义:

(1)指令操作数中给定的一个4或5位的立即数值表示一个移位数值,范围为(・16〜15)。

⑵状态寄存器ST1的累加器移位方式(ASM)位,共5位,表示一个范围为・16〜15的移位数。

(3)T寄存器中最低6位的数值表示一个范围为・16〜31的移位数。

例如:

ADDA,-4,B:

累加器A右移4位后加到累加器B

ADDA,ASM,B;累加器A按ASM规定的移位数移位后加到累力II器B

NORMA;按T寄存器中的数值对累加器归一化

6、乘法器/加法器单元

乘法器/加法器的控制:

(1)乘法器工作控制:

状态寄存器ST1中的FRCT位=1时,小数相乘方式,乘法结果左移1位,以消去多余的符号位。

FRCT二0时,整数相乘方式。

(2)乘法运算的饱和处理:

当SMUL=1时,在用MAC或MAS指令进行累加以前,对乘法结果作饱和处理。

(3)加法运算的饱和处理:

当OVM=1时,在用MAC或MAS指令进行累加以后,对加法结果作饱和处理,然后保存到累加器A或B。

ALU运算发生正数溢出,目的累加器置成正的最人值(OO7FFFFFFFH);发生负数溢出置成负的最人值(FF80000000H)如果发生溢出则ST1的OVA位或OVB位置1。

⑷乘加结果的舍入(圆整)处理:

如MAC、MAS等指令,如果带后缀R,就对结果进行舍入处理,即加2】5至结果,并将目的累加器的低16位清0。

7、状态和控制寄存器

C54x有3个状态和控制寄存器:

1状态寄存器O(STO);

2状态寄存器1(STI);

3处理器工作方式状态寄存器(PMST)o

使川置位指令SSBX和复位指令RSBX可以单独设置和清除状态寄存器的各位。

⑴状态寄存器STO和ST1:

STO主要反映寻址要求和计算的中间运行状态。

其各位定义如下:

bit

15-13

12

11

10

9

8-0

位定义

ARP

TC

C

OVA

OVB

DP

bit

15-13

12

11

10

9

8-0

位定义

ARP

TC

C

OVA

OVB

DP

STO各位的含义

STO主要反映寻址要求和计算的中间运行状态。

bit

15-13

12

11

10

9

8-0

位定义

ARP

TC

C

OVA

OVB

DP

ARP(AssistantRigisterPointer):

辅助寄存器指针

TC(TestControlSignal):

测试/控制标志。

C(Carry):

进位标志。

加法进位时置1。

减法借位时清0。

OVA(OverflowA):

累加器A的溢出标志。

OVB(OverflowB):

累加器B的溢出标志。

DP(DataMemeryPagePointer):

数据存储器页指针。

DP的9位数作为高位将指令中的低7位作为低位结合,形成16位直接寻址方式下的数据存储器地址。

ST4各位含义

ST1主要反映寻址要求、计算的初始状态设置、I/O及中断控制。

其各位定义如下:

bit

15

14

13

12

11

10

9

含义

BRAF

CPL

XF

HM

INTM

0

OVM

bit

8

7

6

5

4-1

-舍义・

SXM.

C16

•鼻■

FRCT

CMPT

ASM.

4CpiCC151011/A111111llcll

I

C

)

BRAF(BlockRepeatActionFlag):

块重复操作标志。

CPL(Compilermode):

直接寻址编辑方式标志位。

XF(ExternalFlag):

XF引脚状态控制位

HM(HoldMode):

芯片响应HOLD信号时,CPU保持工作方式标志。

INTM(lnteruptMode);中断方式控制位。

OVM(OverflowMode):

溢出方式控制位。

SXM(Sign-extensionMode):

符号位扩展方式控制位。

C16(DoubleprecisionArithmaticMode):

双16位/双精度算术运算方式控制位。

FRCT(FractionMode):

小数方式控制位。

CMPT(CompatibilityMode):

间接寻址辅助寄存器修正方式控制位。

ASM(AccumulateShiftMode):

累加器移位方式控制位。

(2)处理器工作模式状态寄存器PMST

7

■

5

1

6

5

4

3

2

O

称

IP

SAVI

KF

T

S

S

HF

F

O

O

O

O

无效

E

处理器工作模式状态寄存器PMST

位

7

■

5

1

6

5

4

3

2

O

称

名

RTP

I

SAVI

KF

T

S

S

HFF.1

O

O

O

O

无效

E

IPTR:

中断向量指针;

MP/MC:

微处理器/微型计算机工作方式位

OVLY:

RAM重复占位位。

AVSI:

地址可见位。

DROM:

数据ROM位。

CLKOFF:

CLKOUT时钟输出关断位。

SMUL:

乘法饱和方式位。

SST:

存储饱和付

3.3C54X片内存储器系统

1、读写总线

(1)稈序总线:

PB

(2)数拯总线:

CB、DB、EB

(3)地址总线:

PAB、CAB、DAB、EAB

2、片内存储器

(1)ROM:

(2)DARAM:

双操作,CPU可在一个周期内两次读/写

(3)SARAM:

单操作,每个机器周期只可被访问一次

3、存储器空间

(1)程序空间:

64K字,要执行的指令和执行中要用到的系数表

(2)数据空间:

64K字,各种数据

(3)1/O空间:

64K字,映射外围设备接口

4、存储器的分配

(1)处理器工作方式状态寄存器(PMST)的3个状态位MP/MC、OVLY位、DROM位控制C54x片内存储器映射到程序或数据存储空间

MP/MCft=0/1,则片内ROM安排到程序空间(微计算机方式)/不安排到程序空间(微处理器方式),片内ROM16K,地址为C000H—FFFFH(MP/MC位=0).

OVLY位=1/0,则片内RAM安排到程序和数据空间/只安州到数据仔储空间;OVLY位=1,片内DRAMnJ'作为程序存储器空间,0000H—7FFFH

DROM位=1/0,则部分片内ROM安排到/不安排到数据空间;DROM位=1,片内ROM16K,其数据空间地址为C000H—FFFFH;此时片内DRAM/SRAM在数据空间地址安排为OOOOH—BFFFH

(2)在存储空间最后的2KROM(F800H—FFFFH)是由TI公司定义的,一般:

参数表(口、A率压扩表、正弦函数查找表)、

自检程序(FFOOH—FF7FH)、中断向量表(FF80H—FFFFH)o

(3)在数据空间的前80H个地址单元是存储器映射寄存器,其中:

:

、26个CPU寄存器,见下表

•外设寄存器(20H—5FH)•高速暂存区(60H—7FH)

(4)对数据空间的RAM,C54X采川分块方式,这样在两个不同块的数据可在同一周期读写。

(5)C54X有一个独立编址的I/O设备空间。

它是一个64K字的地址空间(OOOOh〜FFFFh),都在片外。

访问I/O是对I/O映射的外部器件进行访问,两条指令可以对其寻址:

PORTR(读I/O设备)、PORTW(向I/O设备写),引脚MSTRB有效访问存储器,引脚IOTRB有效访问I/O设备。

(6)不同类型存储器访问时总线使用情况如表5.10,P85.

存储器映像CPU寄存器

地址卩

名称&

说明心

0H卩

iMRf

中断屏蔽寄存器》

IHp

IFRp

中断标志奇存器*

2〜5H「

—p

保留"

6Hp

STOu

状态寄存器0门

7H"

STI2

伏态奇存器2

8H。

A»

漿加器A低字,15〜0位.

9HP

AHp

異加器A高字,31〜16位二

AH门

AW

累加器現保护位,39—32

BH」

BL^

漿加器Bfg壬1A0位卩

CHa

BHa

累加器B高字.31〜"拉门

DH「

B3

累加器B保护位,39~32位a

EHq

D

暂时寄存器•

FHp

TRN^

转檢寄存器••

10HP

AR2

稱助寄存器2

10H"

AROj

辅助寄存器2

11H~

ARla

補助寄存器2

12HQ

AR2^

辅助寄存器2"

13Hq

AR3^

辅助寄存器3"

14H"

ARQ

稱助寄存器4p

15HQ

ARA

稱助寄存器5p

16Hs

ARQ

辅助寄存器6门

17H^

AR7^

補助寄存器2

18Hp

SPp

堆栈指针Q

19Hp

BKe

循环镰冲大小寄存器“

IAHp

BRCp

拱重夏计数器卩

1BH*

RSQ

块重复首址畫特器门

1CH*

REAa

块重复尾址寄吏.讀门

lDHa

PMSTa

姬里器模式状态寄存器门

lEH^

XPO

程序计数器扩展寄存器」

3.4C54X中断系统

1、中断类型

C54X中断系统有两种中断:

软件中断(INTR、TRAP、RESET)和硬件中断硬件中断引发方式:

•通过中断引脚触发的外部硬件中断

•通过片内I/O设备接口中断信号触发的内部破件屮断

2、中断分类

可屏蔽中断和不可屏蔽中断。

可屏蔽屮断:

可以用软件來屏蔽或使能的硬件和软件屮断

C54xDSP最多可以支持16个用户可屏蔽中断

非屏蔽中断:

这些中断是不能够屏蔽的。

包括所有的软件中断,以及两个外部硕件中断(RS复位和NMI)

3、中断标志寄存器(IFR)

中断标志寄存器:

是一个'C5402存储器映射的CPU寄存器,可以识别和清除有效的中断。

当一个屮断出现时,IFR屮的相应的屮断标志位置1,直到CPU识别该中断为止

resvd

DMAC5

DMAC4

BXINT1

DMAC3

BRINT1

DMAC2

HPINT

INT3

15-14

13

12

11

10

9

8

TINT1

DMAC1

DMACO

BXINTO

BRINTO

TINTO

INT2

INT1

INTO

7

6

5

4

3

2

1

0

屮断标志清除:

1C54xDSP复位(RS引脚为低电平)。

2中断得到处理。

3将1写到IFR中的适当位,相应的诡未处理完的中断被清除。

4利用合适的中断号执行INT时旨令。

4、中断屏蔽寄存器(IMR)

中断屏蔽寄存器(IMR):

是一个存储器映射的CPU寄存器,主要用來屏蔽外部和内部中断。

resvd

DMAC5

DMAC4

BXINT1

DMAC3

BRINT1

DMAC2

HPINT

INT3

15-14

13

12

11

10

9

8

TINT1

DMAC1

DMAC0

BXINT0

BRINT0

TINTO

INT2

INT1

INTO

7

6

5

4

3

2

1

0

状态寄存器ST1中的INTM位=1,IMR无效。

当ST1中的INTM位=0时,IMR寄存器中的某一位为1,就使能相应的中断。

用户可以对IMR寄存器进行读写操作。

5、C54xDSP处理中断的步骤

⑴屮断请求。

通过软件(程序代码)或硬件(引脚或片内外设)请求挂起主程序。

如果中断源正在请求一个可屏蔽中断,则当中断被接收到时中断标志寄存器(IFR)的相应位被置1。

硬件中断由如下信号发出请求:

•INT3-INT0弓I脚。

•/RS和/NMI引脚。

•RINTO、XINTO、RINT1和XINT1(串行口中断)。

•TINT(定时器中断)。

软件中断请求:

•INTRK:

指令操作数(K中断号)表示CPU分支转移到哪个中断向量地址。

ST1寄存器的中断模式位(INTM)被设置为1用以禁止可屏蔽中断。

•TRAP:

该指令执行的功能与INTR指令一致,但不设置INTM位。

•RESET:

该指令执行•个卄屛蔽软件复位,RESET指令影响ST0和ST1寄存器,但是不会影响PMST寄存器。

当应答RESET指令时,INTM位被设置为1用以禁止可屏蔽中断。

⑵应答中断。

软件中断和非屏蔽硬件中断会立刻被应答,可屏蔽中断仅仅在如下条件满足后才被应答:

•高优先级。

当超过一个硬件屮断同时被请求时,DSP按照中断优先级响应中断请求。

•INTM位为0。

当响应一个中断后,INTM位被置1。

如果程序使用RETE指令退出屮断服务程序后,从屮断返回后INTM重新为0。

使用硕件复位(RS)或执行SSBXINTM语句(禁止中断)会将INTM位置1。

通过执行RSBXINTM语句(使能屮断),可以复位

INTM位。

INTM不会自动修改IMR或IFR寄存器。

•IMR屏蔽位为1。

每个可屏蔽中断在IMR寄存器中都冇自己的屏蔽位。

为了使能一个中断,可以将其屏蔽位置1。

⑶执行中断服务程序(ISR)

一旦中断被应答,发出中断响应信号IACK,清除IFR屮的相应的屮断标志位,C54xDSP执行屮断向量地址所指向的分支转移指令,并执行中断服务程序(ISR)o

6、中断向量地址的计算

中断向量可以映射到除保留区域外程序存储器的任何128字页面的起始位置。

中断向量地址是由PMST寄存器中的IPTR(9位中断向量指针)和左移2位后的中断向量序号(中断向量序号为0-31,左移2后变成7位)所组成。

例如,如果的中断向量号为16或10h,左移2位后变成40h,若IPTR=0001h,则中断向量的地址为OOCOh,中断示。

向量

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

位

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

3.4C54X引脚

1、地址和数据信号

A22.A21.——、A0;输出/高阻,外部程序、数据和I/O空间复用地址引脚;保持状态或者IEEE1149测试时为高阻态。

D15、D14、——、DO;输入/输出/高阻,外部程序、数据祖I/O空间读写复用引脚;保持状态或者IEEE1149测试时为咼B且态。

2、初始化、中断和复位信号

LACK;输出/高阻,中断响应信号。

INTO、INT1、INT2、INT3:

输入,外部可屏蔽中断请求信

nNM1:

输入,不可屏蔽中断请求信号。

RS:

输入,复位信号

MP/MC:

输入,微处理器/微型计算机方式选择。

CNT:

输入,I/O电平选择。

(CNT=1,5V;CNT=0,3V)

3、多处理器信号

BIO:

输入,控制分支转移的信号。

XF:

输出/高阻,CPU标志输出。

4、存储器控制信号

DS>PS、IS:

输出/高阻,外部数据、程序、—170空同选择信号。

MSTRB:

输出/高阻,CPU读写外部程序、数据空间。

^READY:

输入,数据准备好信号。

R/W:

输出/高阻,外部读写控制。

IOSTRB:

输出/高阻,CPU读写I/O空间。

HOLD:

输入,外部请求控制地址、数据和控制信号。

HOLDA:

输出/高阻,CPU保持响应信号。

MSC:

输出/高阻,CPU微状态完成信号,软件等待到最后一个状态时发出。

受到软件等待状态寄存器(SWWSR)的控制。

IAQ:

输出/高阻,表示止在执行指令的地址出现在地址总线上。

15

1412

119

86

53

20

保WXPA(仅TMS32OC548)

I/O

HiData

LowData

HiProg

LowProg

R

R/W

R/W

R/W

R/W

R/W

其它主要是关于各片内外设I/O接口的引脚。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- DSPTMS320C54X 系列 芯片 结构 基本特征

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx