EDA洗衣机控制器.docx

EDA洗衣机控制器.docx

- 文档编号:9389234

- 上传时间:2023-02-04

- 格式:DOCX

- 页数:12

- 大小:77.64KB

EDA洗衣机控制器.docx

《EDA洗衣机控制器.docx》由会员分享,可在线阅读,更多相关《EDA洗衣机控制器.docx(12页珍藏版)》请在冰豆网上搜索。

EDA洗衣机控制器

第一章设计说明

1.1设计要求

●设置2种工作方式:

洗衣、甩干;

●显示倒计时时间:

洗衣时间为5分,甩干时间为15秒;

●具有紧急情况手动停止功能。

●用2个拨码开关设置工作方式:

洗衣、甩干;

●用3个动态数码管显示时间。

1.2设计思路

通过三个减法计数器(十进制、六进制、五进制)同步连接以实现倒计时功能;在启动前使用两个拨码开关对计数器预置初值,以实现两种功能(洗衣:

五分钟倒计时,甩干:

15秒钟倒计时),另外由一个拨码开关控制计时器的启动与暂停(洗衣机的启动与急停);使用三个共阴极数码管显示时间,显示方式为动态扫描法。

1.3模块介绍

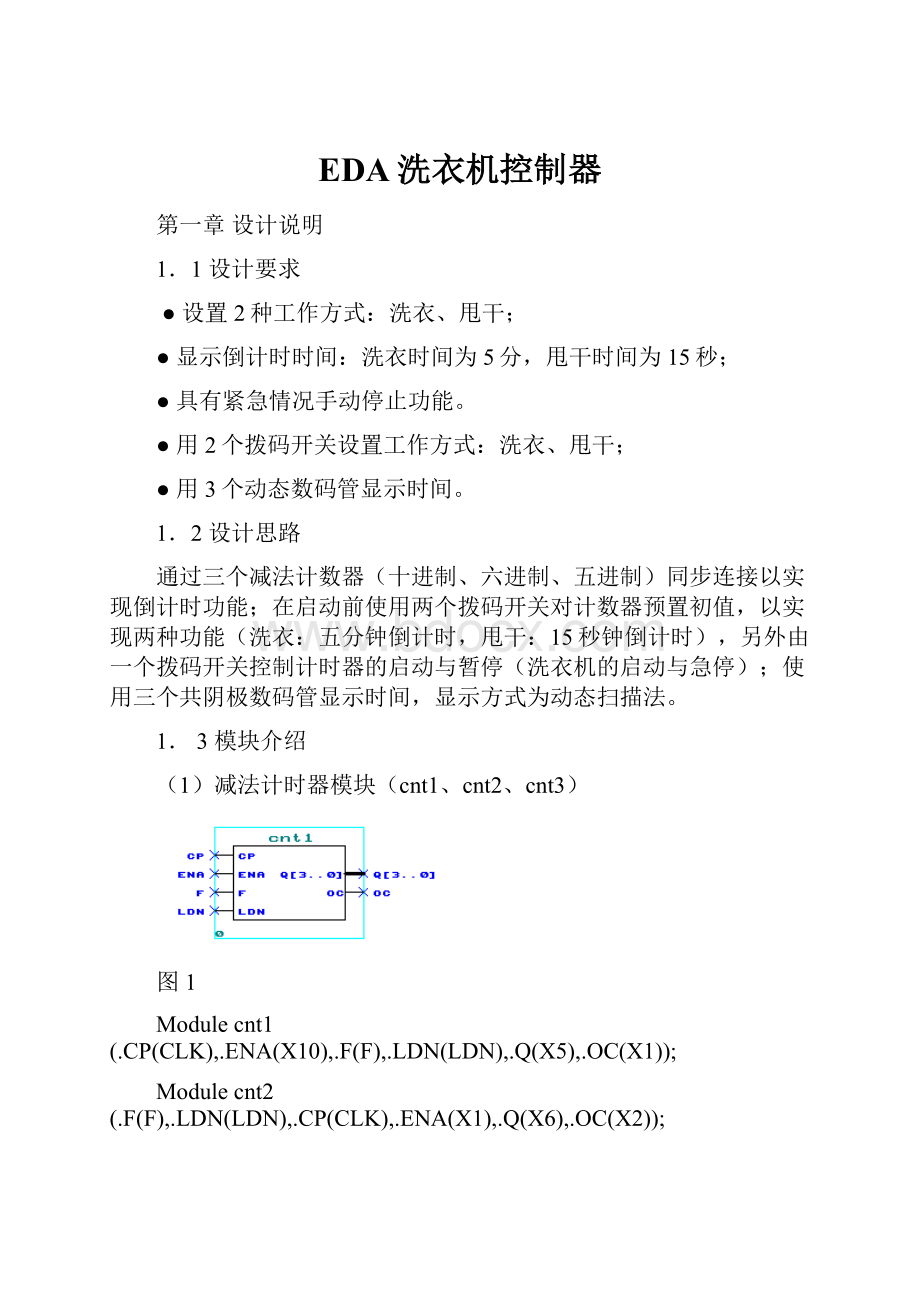

(1)减法计时器模块(cnt1、cnt2、cnt3)

图1

Modulecnt1(.CP(CLK),.ENA(X10),.F(F),.LDN(LDN),.Q(X5),.OC(X1));

Modulecnt2(.F(F),.LDN(LDN),.CP(CLK),.ENA(X1),.Q(X6),.OC(X2));

Modulecnt3(.F(F),.LDN(LDN),.CP(CLK),.ENA(X4),.Q(X7),.OC(X3));

三个减法计数器模块分别为十进制、六进制、五进制。

CLK为时钟信号输入端;ENA为减法计数器使能端;F、LDN为预置数控制端,当LDN有效时进入预置数状态,这时F为“1”则置为十五秒,F为“0”则置为五分钟;Q为计数值输出端;OC为借位端。

(2)数码管动态扫描模块

图2

Modulecnt4(.CLK(CLK1),.Q1(X5),.Q2(X6),.Q3(X7),.Q(X8),.SEG(SEG[2:

0]));

CLK为高频时钟信号输入端;Q1、Q2、Q3为显示信号输入端;Q为显示信号输出端;SEG为数码管位选信号输出端。

(3)七段显示译码模块

Moduledec7s(.A(X8),.Q(Q[6:

0]));

A译码信号输入端,Q为共阴极数码管段位信号输出端。

(4)RS触发器模块

Modulers_ff(.Q(X9),.QN(X11),.SD(LDN),.RD(X12));

SD、RD分别为置一与置零输入端,Q为输出端。

(5)顶层模块

图3

moduletop(Q,SEG,CLK,CLK1,FNC,F,LDN);

Q为数码管段控信号输出;SEG为数码管位控信号输出;CLK为计数器时钟信号输入端;CLK1为动态扫描高频时钟信号输入端;FNC为计数器启动暂停控制信号输入端;F、LDN为功能控制信号输入端。

第二章VerilogHDL设源程序

2.1moduletop(Q,SEG,CLK,CLK1,FNC,F,LDN)(顶层模块)

moduletop(Q,SEG,CLK,CLK1,FNC,F,LDN);

inputCLK,CLK1,FNC,F,LDN;

output[6:

0]Q;

output[2:

0]SEG;

wireX4,X9,X10,X11,X1,X2,X3,X12;

wire[3:

0]X5,X6,X7,X8;

rs_ffu6(.Q(X9),.QN(X11),.SD(LDN),.RD(X12));

assignX10=(X9&&FNC);

assignX12=((~X3)&&X2&&X1);

cnt1u1(.CP(CLK),.ENA(X10),.F(F),.LDN(LDN),.Q(X5),.OC(X1));

cnt2u2(.F(F),.LDN(LDN),.CP(CLK),.ENA(X1),.Q(X6),.OC(X2));

assignX4=(X1&&X2);

cnt3u3(.F(F),.LDN(LDN),.CP(CLK),.ENA(X4),.Q(X7),.OC(X3));

cnt4u4(.CLK(CLK1),.Q1(X5),.Q2(X6),.Q3(X7),.Q(X8),.SEG(SEG[2:

0]));

dec7su5(.A(X8),.Q(Q[6:

0]));

endmodule

2.2modulecnt1(CP,ENA,F,LDN,Q,OC)(十进制计数器1)

modulecnt1(CP,ENA,F,LDN,Q,OC);

inputCP,ENA,F,LDN;

outputOC;

output[3:

0]Q;

regOC;

reg[3:

0]Q_TEMP,Q;

always@(posedgeCP)

begin

if(F&&LDN)Q_TEMP=4'b0101;

elseif((~F)&&LDN)Q_TEMP=4'b1001;

if(ENA)

if(Q_TEMP>4'b0000)Q_TEMP=Q_TEMP-1;

elseQ_TEMP=4'b1001;

elseQ_TEMP=Q_TEMP;

end

always

begin

if(Q_TEMP==4'b0000&&ENA)OC=1'b1;

elseOC=1'b0;

Q=Q_TEMP;

end

endmodule

2.3modulecnt2(F,LDN,CP,ENA,Q,OC);(六进制计数器2)

modulecnt2(F,LDN,CP,ENA,Q,OC);

inputCP,F,LDN,ENA;

outputOC;

output[3:

0]Q;

regOC;

reg[3:

0]Q,Q_TEMP;

always@(posedgeCP)

begin

if(F&&LDN)Q_TEMP=4'b0001;

elseif((~F)&&LDN)Q_TEMP=4'b0101;

if(ENA)

if(Q_TEMP>4'b0000)Q_TEMP=Q_TEMP-1;

elseQ_TEMP=4'b0101;

elseQ_TEMP=Q_TEMP;

end

always

begin

if(Q_TEMP==4'b0000&&ENA)OC=1'b1;

elseOC=1'b0;

Q=Q_TEMP;

end

endmodule

2.4modulecnt3(F,LDN,CP,ENA,Q,OC)(五进制计数器3)

modulecnt3(F,LDN,CP,ENA,Q,OC);

inputCP,F,LDN,ENA;

outputOC;

output[3:

0]Q;

regOC;

reg[3:

0]Q_TEMP,Q;

always@(posedgeCP)

begin

if(F&&LDN)Q_TEMP=4'b0000;

elseif((~F)&&LDN)Q_TEMP=4'b0100;

if(ENA)

if(Q_TEMP>4'b0000)Q_TEMP=Q_TEMP-1;

elseQ_TEMP=4'b0100;

elseQ_TEMP=Q_TEMP;

end

always

begin

if(Q_TEMP==4'b0000&&ENA)OC=1'b0;

elseOC=1'b1;

Q=Q_TEMP;

end

endmodule

2.5modulecnt4(CLK,Q1,Q2,Q3,Q,SEG);(动态扫描模块)

modulecnt4(CLK,Q1,Q2,Q3,Q,SEG);

inputCLK;

input[3:

0]Q1,Q2,Q3;

output[3:

0]Q;

output[2:

0]SEG;

reg[3:

0]Q;

reg[2:

0]SEG;

reg[1:

0]TMP;

always@(posedgeCLK)

begin

if(TMP<2)TMP=TMP+1;

elseTMP=0;

case(TMP)

0:

beginSEG=3'b010;Q=Q1;end

1:

beginSEG=3'b001;Q=Q2;end

2:

beginSEG=3'b000;Q=Q3;end

endcase

end

endmodule

2.6modulers_ff(Q,QN,SD,RD)(RS触发器模块)

modulers_ff(Q,QN,SD,RD);

inputSD,RD;

outputQ,QN;

assignQ=~(RD||QN);

assignQN=~(SD||Q);

endmodule

2.7moduledec7s(A,Q)(共阴极显示译码模块)

moduledec7s(A,Q);

input[3:

0]A;

output[6:

0]Q;

reg[6:

0]Q;

always@(A)

begin

case(A)

0:

Q='b0111111;

1:

Q='b0000110;

2:

Q='b1011011;

3:

Q='b1001111;

4:

Q='b1100110;

5:

Q='b1101101;

6:

Q='b1111101;

7:

Q='b0000111;

8:

Q='b1111111;

9:

Q='b1101111;

endcase

end

endmodule

第三章波形仿真图

3.1顶层模块相关波形图

(1)15秒倒计时预置数(甩干功能选择)

图4

(2)5分钟倒计时预置数(洗衣功能选择)

图5

(3)紧急停止功能

图6

(4)紧急停止后重启

图7

(5)洗衣时间到计时停止

图8

3.2动态扫描模块波形图

图9

3.3减法计数器波形图

(1)借位信号输出

图10

(2)计时开始前预附初值

图11

第四章管脚锁定及硬件连线

I\O端口

扩展板接口

硬件连接

备注

CLK

75

频率组B(1hz)

自锁

CLK1

83

频率组C(1024hz)

自锁

F

40

拨码开关sw2

内锁

FNC

41

拨码开关sw3

内锁

LDN

39

拨码开关sw1

内锁

Q0

85

数码管a段

自锁

Q1

86

数码管b段

自锁

Q2

87

数码管c段

自锁

Q3

88

数码管d段

自锁

Q4

89

数码管e段

自锁

Q5

90

数码管f段

自锁

Q6

92

数码管g段

自锁

SEG0

173

位选ss0

自锁

SEG1

174

位选ss1

自锁

表1

第五章总结

本次EDA课程设计学习了通过MAX-PLUSⅡ软件,利用verilogHDL硬件描述语言对PLD芯片(EP1K30QC208-3)进行编程,以实现简单的数字系统。

此项技术的核心:

基于芯片的设计方法——采用PLD(可编程逻辑器件),利用EDA开发工具,通过芯片设计来实现系统功能。

这里提到的EDA软件能帮助设计者自动完成几乎所有的设计过程(化简、生成电路原理图、验证电路正确性),再选择合适的PLD芯片,可以在一片芯片中实现整个数字系统,在将PLD芯片安装到电子设备上即完成设计。

在verilogHDL硬件描述语言,不但可以直接描述真值表,然后由软件进行逻辑抽象,而且可以通过行为描述的方法进行数字电路设计。

设计者首先进行功能模块设计,在各功能模块设计完成以后通过顶层文件即可进行功能模块连接,最后完成整个数字系统的设计。

相比于基于电路板的设计方法,这种方法及高效并且正确性高。

课设中,我拿到的题目是《洗衣机控制器的设计》。

通过减法计数器和RS触发器两个关键模块实现了设计要求。

首先,通过EDA课设增加了我对PLD(可编程逻辑器件)的EDA设计技术有了一定的了解。

其次,通过电路功能仿真以及模块的功能描述,让我对数字电子技术的理解有了一个新的角度。

最后,感谢各位指导老师的真诚教导,你们的经验是送给我们最珍贵的礼物。

参考文献

1.郑兆兆、李艳艳、周莲莲等.EDA课程设计指导书.电气工程学院.2010年9月:

38—40。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 洗衣机 控制器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx