43LPMROM宏模块H的使用.docx

43LPMROM宏模块H的使用.docx

- 文档编号:9338567

- 上传时间:2023-02-04

- 格式:DOCX

- 页数:12

- 大小:485.09KB

43LPMROM宏模块H的使用.docx

《43LPMROM宏模块H的使用.docx》由会员分享,可在线阅读,更多相关《43LPMROM宏模块H的使用.docx(12页珍藏版)》请在冰豆网上搜索。

43LPMROM宏模块H的使用

4.3--LPM-ROM宏模块H的使用

D

图4-29 MegaWizardPlug-InManager对话框

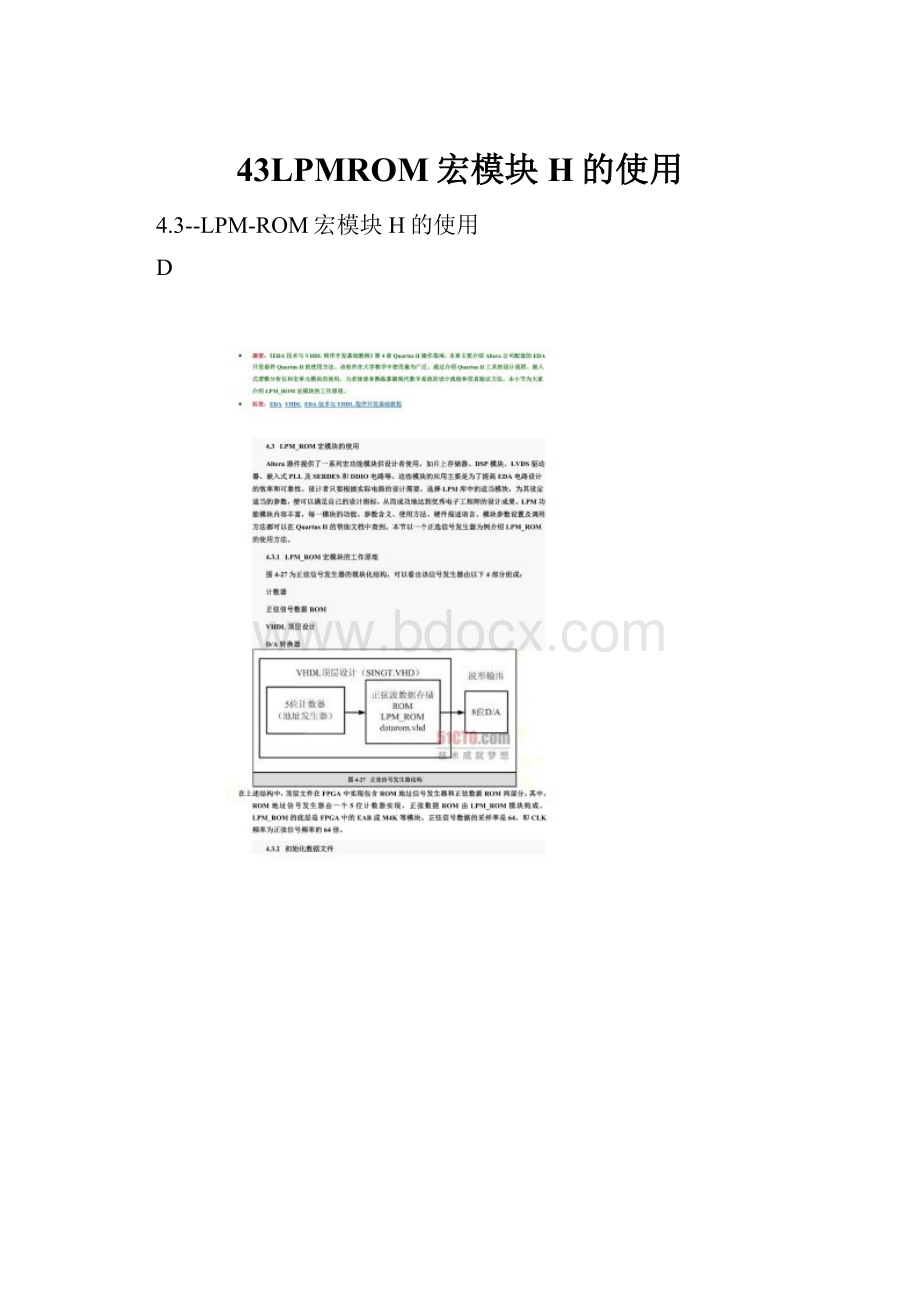

单击Next按钮,出现图4-30所示的窗口,在左栏选择Storage项下的ROM:

1-PORT,再选Cyclone器件和VHDL语言方式,最后输入ROM文件存放的路径和文件名:

F:

\VHDL\sin_gnt\data_rom.vhd,单击Next按钮。

(点击查看大图)图4-30 LPM宏功能设定

2.选择ROM控制线和地址、数据线

在图4-31和图4-32所示的窗口中选择地址与数据的位宽分别为6和8,选择地址所存控制信号inclock,去除输出锁存功能。

(点击查看大图)图4-31 选择data_rom模块数据线和地址线宽度

(点击查看大图)图4-32 选择地址锁存信号inclock

4.3.3 定制LPM_ROM元件

(2)

3.选择数据文件

单击Next按钮进行图4-33所示的窗口,选择"Yes,usethisfileforthememorycontentdata"单选按钮并在Filename文本框中选择数据文件romd.mif,最后选中"AllowIn-SystemMemory…"复选框,完成ROM文件data_rom.vhd的生成。

"AllowIn-SystemMemory…"是Altera的新功能,支持对FPGA中的ROM进行"在系统"测试和读写,且不影响数字系统的正常工作。

(点击查看大图)图4-33 调入ROM初始化数据文件并选择在系统读写功能

按顺序完成以上三步的操作后,Quartus会自动生成data_rom的VHDL源程序,如例4-1所示。

通过阅读程序,读者可以很快了解LPM_ROM调用mif数据文件的方式以及与其他元件进行连接的方法。

【例4-1】data_rom的源程序

1.LIBRARY ieee;

2.USE ieee.std_logic_1164.all;

3.LIBRARY altera_mf;

4.USE altera_mf.all;

--使用宏功能库中的所有元件

5.

6.ENTITY data_rom IS

7. PORT

8. (

9. address :

IN STD_LOGIC_VECTOR (5 DOWNTO 0);

10. inclock :

IN STD_LOGIC ;

11. q :

OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

12. );

13.END data_rom;

14.

15.ARCHITECTURE SYN OF data_rom IS

16. SIGNAL sub_wire0 :

STD_LOGIC_VECTOR (7 DOWNTO 0);

17. COMPONENT altsyncram --例化

altsyncram元件,调用LPM模块altsyncram

18. GENERIC (

--参数传递

19. address_aclr_a :

STRING;

20. init_file :

STRING;

21. intended_device_family :

STRING;

--类属参量数据类型定义

22. lpm_hint :

STRING;

23. lpm_type :

STRING;

24. numwords_a :

NATURAL;

25. operation_mode :

STRING;

26. outdata_aclr_a :

STRING;

27. outdata_reg_a :

STRING;

28. widthad_a :

NATURAL;

29. width_a :

NATURAL;

30. width_byteena_a :

NATURAL

31. );

32. PORT (

33. clock0 :

IN STD_LOGIC ;

34. address_a :

IN STD_LOGIC_VECTOR (5 DOWNTO 0);

35. q_a :

OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

36. );

37. END COMPONENT;

38.BEGIN

39. q <= sub_wire0(7 DOWNTO 0);

40. altsyncram_component :

altsyncram

--参数传递映射

41. GENERIC MAP (

42. address_aclr_a => "NONE",

43. init_file => "romd.mif",

44. intended_device_family => "Cyclone",

45. lpm_hint => "ENABLE_RUNTIME_MOD=YES,

INSTANCE_NAME=ROM1",

46. lpm_type => "altsyncram",

47. numwords_a => 64,

48. operation_mode => "ROM",

49. outdata_aclr_a => "NONE",

50. outdata_reg_a => "UNREGISTERED",

51. widthad_a => 6,

52. width_a => 8,

53. width_byteena_a => 1

54. )

55. PORT MAP (

--声明元件连接关系

56. clock0 => inclock,

57. address_a => address,

58. q_a => sub_wire0

59. );

60.END SYN;

4.3.4 顶层文件的仿真测试

顶层文件的仿真测试是检查整个系统是否能够正常工作最有效的方法。

在生成data_rom.vhd文件后,完成项目的操作流程与4.1节基本相同,包括编辑顶层设计文件,例化刚刚生成的LPM_ROM宏模块、创建工程、全程编译、观察RTL电路、仿真、了解时序分析报告、指定引脚及下载测试等。

例4-2给出了一个使用LPM_ROM宏模块的顶层设计范例。

【例4-2】顶层设计文件

1.LIBRARY IEEE;

--声明IEEE库

2.USE IEEE.STD_LOGIC_1164.ALL;

--声明程序包

3.USE IEEE.STD_LOGIC_UNSIGNED.ALL;

4.ENTITY SINGT IS

5. PORT(CLK:

IN STD_LOGIC;

--实体声明

6. DOUT:

OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

7.END;

8.ARCHITECTURE DACC OF SINGT IS

9.COMPONENT data_rom

--声明LPM_ROM

10. PORT(address:

IN STD_LOGIC_VECTOR(5 DOWNTO 0);

11. inclock:

IN STD_LOGIC;

12. q:

OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

13.END COMPONENT;

14. SIGNAL Q1:

STD_LOGIC_VECTOR(5 DOWNTO 0);

15.BEGIN

16. PROCESS(CLK)

17. BEGIN

18. IF CLK'EVENT AND CLK='1' THEN

19.Q1<=Q1+1;

20. END IF;

21.END PROCESS;

22. U1:

data_rom PORT MAP(address=> Q1,q=>DOUT,

inclock=>CLK); --调用data_rom

23. END;

例4-2为顶层设计文件的VHDL代码,仿真结果如图4-34所示。

使用嵌入式逻辑分析仪测试波形,所得结果如图4-35所示,参数设置为1024位采样深度,使用信号源的时钟CLK,触发位置为重点,触发信号是地址发生器的最高位且为上升沿触发,由图4-35可以看到一个正弦信号波形。

(点击查看大图)图4-34 正弦信号发生器的仿真波形

(点击查看大图)图4-35 用SignalTapII实时观察正弦信号发生器的结果

4.4 本章小结

本章主要讲述了采用EDA软件QuartusII进行VHDL设计的操作方法以及嵌入式逻辑分析仪(SignalTapII)和LPM_ROM宏模块的使用。

熟练掌握这些操作对于工程师快速、高效地设计正确的数字系统有很大帮助。

通过本章的学习,读者应该掌握以下几个知识点:

掌握QuartusII基本设计流程;

掌握嵌入式逻辑分析仪的设计目的、原理和使用方法;

掌握LPM_ROM宏模块的工作原理和使用方法。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 43 LPMROM 模块 使用

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《Java程序设计》考试大纲及样题试行.docx

《Java程序设计》考试大纲及样题试行.docx