EDA实验指导图文精.docx

EDA实验指导图文精.docx

- 文档编号:9260676

- 上传时间:2023-02-03

- 格式:DOCX

- 页数:45

- 大小:2.28MB

EDA实验指导图文精.docx

《EDA实验指导图文精.docx》由会员分享,可在线阅读,更多相关《EDA实验指导图文精.docx(45页珍藏版)》请在冰豆网上搜索。

EDA实验指导图文精

《EDA与数字系统课程设计》日程安排

星期三上午:

Max+Plus2使用练习。

完成一个简单门电路的设计输入、编译、仿真、实验验证。

做图1-3-3十进制计数器。

完成设计输入、编译、仿真、实验验证。

下午:

做图形文件练习。

做图1-2-6、不做图1-3-4,改做Z60.GDF(六十进制。

用Z60.GDF制作十二进制计数器(01~12,二十四进制计数器(00~

23和百进制计数器。

星期二上午:

介绍VerilogHDL语言

下午:

做VerilogHDL文本输入

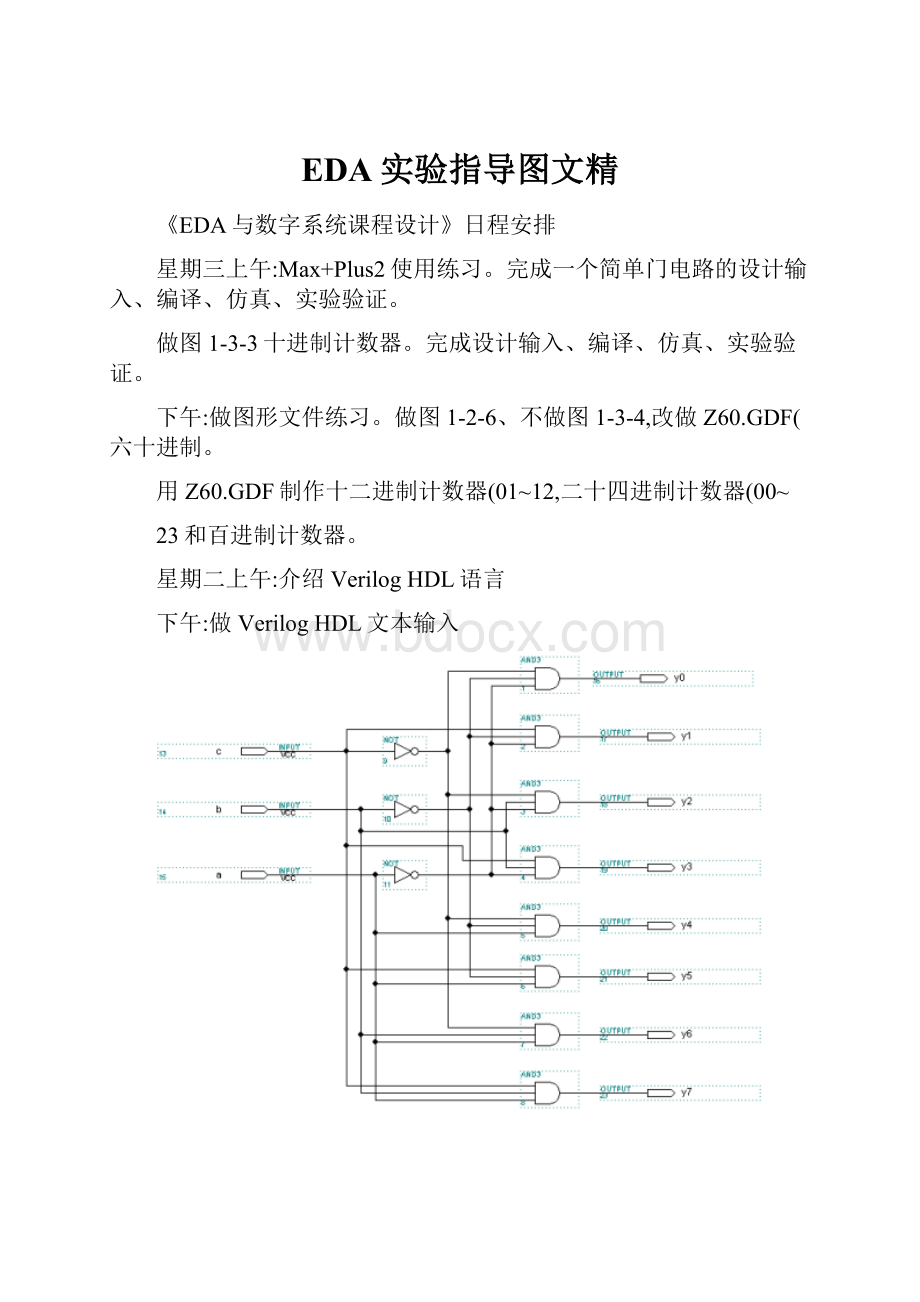

图1-2-63-8译码器

图1-3-3用74LS161实现十进制加法计数器

例1-4-1图

常用词语解释:

EDA:

ElectronicDesignAutomation

电子设计自动化

CPLD:

ComplexProgrammableLogicDevice复杂可编程逻辑器件

HDL:

HardwhareDescriptionLanguage

硬件描述语言

EDA实验指导

电气与自动化学院EDA实验室

一、EDA工具与软件

目前在教学上使用的EDA软件和对应芯片:

Max+plusII、quartusII(Altera公司

ISPexpert(Lattice公司

Fundation(Xilinx公司

具有CPLD设计输入、编译,摸拟仿真、下载制片等功能;

具有原理图输入和文本输入两种输入方式。

(AHDL、VHDL、VerilogHDL

1.1MAX+PLUSII10.0(BASELINE

支持的器件:

1、FLEX10K10系列

如EPF10K10LC84-4

2、MAX7000S系列

如EPM7128SLC84-15

1.2HDL语言

AHDL(*.tdf

VerilogHDL(*.v

VHDL(VeryHighSpeedIntergatedCircuitHardwareDescriptionLanguage(*.vhd参见教材《EDA与数字系统设计》第二、三章

1.3EDA设计步骤

2、编译(检查语法错误

3、仿真(时序检查

4、管脚分配

5、编译(检查系统设计错误

6、下载

7、实验验证

1-6在计算机上完成

二、MAX+PLUSII软件使用指导

2.1设计输入方式

1.图形输入方式(.gdf文件

2.文本输入方式

AHDL(TheAlteraHardwareDescriptionLanguage

VHDL

VerilogHDL

图形输入方式的过程(1

1.双击:

我的电脑图标,进入F:

盘,新建一个文件夹,用英文字母命名。

zwy00

2.进入Windows桌面,双击Max+plusII10.0BASELINE图标

(或者X:

\maxplus2\max2win.exe

3.启动File/New菜单,选择GraphicEditor,打开原理图编辑器;

图形输入方式的过程(2

1.元器件放置(双击编辑工作区空白处,弹出对话框

2..在元器件之间添加连线,copy,放大

3.添加输入、输出引脚,并给它们命名;

4.保存原理图在自己的目录下,方法:

FILE/SAVEAS

5.输入文件名:

如zand(扩展名为.GDF

6.(画图过程中定时保存文件,以免文件丢失。

2.2编译(项目文件

1.把当前文件转换成顶层文件

2.点击Assign/Device菜单,弹出对话框,选择:

Devicefamily选FLEX10K,Device选EPF10K10LC84-4

3.启动Max+plusII/Compiler菜单,选择Start,开始编译;

若电路有错,编译器停止编译,并显示出错信息;

若电路无错,则编译通过,生成扩展名为*.sof文件,以备硬件下载时用。

4.在确认该模块逻辑功能正确的前提下,关闭编译对话框,启动File/Creatdefault

symbol,生成扩展名为*.sym符号文件。

该符号文件可以作为一个元器件在其他图形文件(.GDF中使用

当前文件转换成顶层文件

把当前文件转换成顶层文件

2.3计算机仿真(时序模拟编译通过后进行时序模拟

2.3.1建立波形输入文件扩展名是*.scf

1.打开菜单File/New,选WaveformEditorFile(.scf,OK;

2.在波形编辑器窗口中单击鼠标右键,选EnterNodesfromSNF,打开对话框;

3.在Type区选中Inputs和Outputs,单击List按钮,可在其右下方看到设计中的输入输出信号,

单击“=>”可将这些信号选到SelectedNodes&Groups区,OK。

2.3.2编辑输入节点波形

1.在菜单Options中选中SnaptoGrid和ShowGrid,打开GridSize(20ns,设置网格时间大小;点

击File/EndTime设置摸拟时间的长短(如2us。

2.使用绘制图形工具条绘制输入各个节点波形,高、低电平,CLK周期选择等。

3.可以将Q3、Q2、Q1、Q0作为一个组Q[3..0]来观测。

4.选File/Saveas存盘,生成zand.SCF波型文件。

2.3.3时序模拟

1.在菜单MaxplusII中选Simulator,打开对话框,可以改变摸拟Starttime和Endtime。

2.单击Start,开始模拟;

3.模拟完毕,单击Open*.SCF得模拟结果,可对模拟结果进行检查。

(注意动态响应的滞后

2.4管脚分配

1.启动Max+plusII/FloorplanEditor菜单,对话框中,显示该设计项目的信号列表和目标芯片的管脚图;

2.选择不同的下载板(器件,管脚分配方法不一样。

管脚分配时应注意实验箱的实际情况,选择手动分配管脚。

输入逻辑信号A,B只能分配给27、28管脚与信号开关相连,输出电平Y只能分配给16、17、18中的任1个管脚与发光管相连。

(参见:

三、EDA实验装置使用说明

3.管脚分配好后,再进行编译。

4.*用Assign/pinlocationchip可以对分配好的管脚进行修改,

2.5下载

1.关闭实验箱电源。

2.检查实验板下载线与计算机并口是否连接好?

3.打开实验箱电源。

4.启动Max+PlusII/Programmer菜单,确认对话框中的信息:

File:

zand.sof,

device:

EPF10K10LC84-4;

5.如果是第一次使用该软件,启动Options/Hardwaresetup菜单,

在HardwareType中选ByteBlaster(MV

6.选择Configure完成下载

*如果在下载对话框中给出的文件不正确,

*可在File/slectPogrammingFile中选择要下载文件,重新下载。

2.6VerilogHDL语言输入操作方法

(一、VerilogHDL语言文本文件输入操作方法

在F:

盘中新建一个文件夹,如:

F:

\ZWY01

1进入Windows操作系统,打开Max+plusII10.0;

2启动File/New菜单,选择TextEditorfile,打开文本编辑器,输入文件;

3输入文件后,点击File/Saveas,保存文件,如:

SEL.V

文件名SEL与文本文件中的MODULE后的模块名相同;

文件的扩展名是.V

不能搞错

4把当前文件转换成顶层文件

点击Assign/Device菜单,弹出对话框,选择:

Devicefamily选FLEX10K,

Device选EPF10K10LC84-4

COMBILE(编译;

5关闭编译对话框,启动File/Creatdefaultsymbol,生成扩展名为*.sym符号文件,再

编译一次。

该符号文件可以作为一个元器件在其他图形文件(.GDF中使用

6可以对文本文件进行仿真,管脚分配,下载和验证。

(与图形文件方法相同

(二、特别注意两种设计输入的扩展名:

1.原理图设计输入,对应的文件名称是*.gdf,其扩展名称是.gdf,如zadd.gdf,产生的波形文件名是zadd.scf,编译后产生的下载文件是zadd.sof

2.VerilogHDL设计输入对应的文件名称是*.v,其扩展名称是.v,如addt.v(更不能是addt.tdf,产生的波形文件名是addt.scf,编译后产生的下载文件是addt.sof,File/Createdefaultsymbol产生符号文件名称是addt.sym,此符号文件可以作为一个元器件在其他图形文件(.GDF中使用。

3.*.gdf与*.v文件名称不能相同。

如果在一个文件夹中出现相同名称的.v和.gdf(或.tdf文件,如zadd.v和zadd.gdf(或zadd.tdf,将产生非常严重的错误。

解决问题的办法是:

在该文件所在的文件夹中,保留zadd.v文件,删除文件名是zadd的其他类型的文件,重新产生符号文件zadd.sym

三、EDA实验装置使用说明

EPF10K10LC84-4为目标芯片的实验板,管脚与外围信号已连接好,必须按下表进行管脚分配。

表一EPF10K10管脚分配表(5

注:

1、MAX+PLUSII在管脚分配时按照此表进行手动分配管脚,不要选择自动分配管脚。

2、在实验板上所有连线已经接好。

3、在实验板上有三路时钟信号。

时钟CP1:

与PLD器件的42号管脚相连,频率调节范围:

1/256Hz~1Hz,1Hz~256Hz。

时钟CP2:

与PLD器件的1号管脚相连,频率调节范围:

1Hz~256Hz,256Hz~16KHz。

时钟CP3:

与PLD器件的43号管脚相连,频率调节范围:

256Hz~16KHz,16KHz~4MHz。

实验箱中器件分布图:

四、动态显示控制电路原理

当用七段显示器显示的位数较多时,例如显示八位BCD码十进制数,为了节省硬件开支,常用动态显示方法,即对各显示管进行循环扫描,分时使用显示器驱动电路。

该电路由五个部分组成:

四位同步计数器74161,3线-8线译码器,四位八选一数据选择器,BCD-七段显示译码器和八位显示器等。

1、四位同步计数器:

四位同步计数器的输入时钟CLK,计数器输出信号0123QQQQ,取扫描信号和数据选择信号012SELSELSEL=012QQQ,所用时钟CLK的频率决定动态显示循环扫描频率,利用人眼的视觉惯性,扫描频率应大于50HZ,根椐计数器的分频关系,同步计数器的输入时钟CLK=400HZ左右.

2、3-8线译码器:

在输入时钟CLK某一周期内,3-8译码器输入扫描信号012SELSELSEL,译码器输出八位显示器位控信号18MSMS。

如表1所示,此刻,位控信号只选通一个显示器。

3、四位八选一数据选择器和BCD-七段显示译码器:

在输入时钟CLK某一周期内,具体显示哪一位数是由数据选择信号012SELSELSEL控制的(如表1所示,数据选择器根椐数据选择信号012SELSELSEL的数值从八路输入数据中选择一位BCD码十进制数,通过BCD-七段显示译码器译成七段显示码(如表2所示,送给七段显示器,与此同时,由位控信号选通一个显示器,显示一位十进制数。

4、在连续8个时钟周期内,八个显示器轮流点亮一个时钟周期,只要输入连续时钟CLK,就能实现八位十进制数的动态显示。

表1由012SELSELSEL控制显示器、数据选择顺序表

D

CB

DCBA

CLKD8D7D1

《EDA与数字系统设计》第一版教材

第一章MAX+plus2使用练习

1.1MAX+plus2简介

MAX+plus2(Multiplearraymatrixandprogrammablelogicusersystem是一个完全集成化、易学易用的可编程逻辑设计环境,它可以在多种平台上运行,其图形界面丰富,加上完整的、可即时访问的在线文档,使设计人员可以轻松地掌握软件的使用。

MAX+plus2开发系统有很多特点:

1.界面开放

MAX+plus2是Altera公司的EDA软件,但它可以与其它工业标准的设计输入、综合与

校验工具相连接,设计人员可以使用Altera或标准EDA工具设计输入工具来建立逻辑设计,用MAX+plus2编译器(Compiler对Altera器件设计进行编译,并使用Altera或其它EDA校验工具进行器件或板级仿真。

目前,MAX+plus2支持与Candence、Exemplarlogic、MetorGraphics、Synopsys、Synplicity、Viewlogic等公司所提供的EDA工具接口。

2.与结构无关

MAX+plus2系统的核心Compiler支持Altera公司的FLEX10K、FLEX8000、FLEX6000、MAX9000、MAX7000、MAX5000和Classic可遍程逻辑器件系列,提供了与结构无关的可编程逻辑环境。

MAX+plus2的编译器还提供了强大的逻辑综合与优化功能,使用户可以容易地把设计集成到器件中。

3.丰富的设计库

MAX+plus2提供丰富的库单元供设计者调用,其中包括74系列的全部器件和其它多种

逻辑功能部件,调用库元件进行设计,可以大大减轻设计人员的工作量,缩短设计周期。

4.模块化工具

设计人员可以从各种设计输入、处理和校验选项中进行选择,从而使MAX+plus2可以

满足不同用户的需求,根据需要,还可以添加新功能。

例如,在本教材中,侧重点在于用MAX+plus2进行各种设计输入(图形或HDL输入、编译(Compiler、仿真(Simulator、底层编辑(FloorplanEditor及PLD器件编程校验(Programmer或Configure,并不过多涉及功能测试向量(WaveformEditor、逻辑综合与试配(LogicSynthesize等。

5.硬件描述语言

MAX+plus2软件支持各种HDL设计输入选项,包括VHDL、VerilogHDL和Altera公

司的AHDL。

MAX+plus2软件的启始界面如图1-1-1所示。

本章将通过一些例子来说明利用MAX+plus2进行数字功能模块或数字系统设计的过程。

1.2基于MAX+plus2的电路设计过程

在进入设计之前,需要先建立一个文件夹为用户存放设计文件用,即用户库。

用户库的名称用英文字母表示,例如E:

\maxplus2\lgl。

例1-2-1用原理图输入法设计一个3线-8线译码器。

步骤1、进入Windows操作系统,打开MAX+plus2;步骤2、启动File\ProjectName菜单,输入设计文件的名称(原理图文件的扩展名为.gdf如图1-2-1所示;

步骤3、点击Assign\Device菜单,选择器件(例如EPF10K10LC84-3,OK,如图1-2-2所示;

图1-2-1输入设计文件名称

图1-2-2选择器件

步骤4、启动File\New菜单,如图1-2-3所示,选择GraphicEditorFile,OK,打开原理图编辑器。

步骤5、原理图设计输入

(1元器件放置

在空白处双击鼠标左键,弹出器件选择界面如图1-2-4所示,图中SymbolLibraries中列出文件目录分别的是用户库、基本元器件库、宏功能库和可调参数库。

选择其中任一库,如基本元器件库,则此库中所有元器件的符号名称列在SymbolFiles中,点击所需的元件或在SymbolName中输入元件名,如and3(三输入与门、not(非门、input(输入端口、output(输出端口等,OK即可。

若要安放相同的元件,只要按住Ctrl键,同时用鼠标拖动该元件。

(2在器件之间添加连线

图1-2-4器件选择界面

把鼠标移到元件引脚附近,则鼠标光标自动由箭头变为十字,按住鼠标左键拖动,即可画出连线。

如图1-2-5。

步骤6、给输入、输出引脚命名

电路图绘制完成后,给输入、输出引脚命名,即将PIN_NAME改为:

a,b,c和y0,y1,……y7,如图1-2-6所示。

步骤7、保存原理图

在菜单File\Save下保存原理图,对于第一次输入的新原理图,出现类似文件管理的对话框,

将图1-2-6给输入、输出引脚命名

文件存入用户库、文件名为L38.gdf。

步骤8、编译

启动MAX+plusII\Compiler菜单,按Start开始编译,如图1-2-7,若电路中有错,则显示出错提示。

若电路无错,则编译通过,生成.sof和.pof文件,以备硬件下载或编程时用,同时生成.rpt文

件,可详细查看编译结果。

步骤9、时序模拟仿真

编译通过以后就可以进行时序模拟仿真。

1.建立波形输入文件

(1在菜单File/New下选择WaveformEditorFile.scf,如图1-2-8所示。

(2波形编辑器窗口如图1-2-9所示,在Name下方单击鼠标右键,出现浮动菜单,选择EnterNodesfromSNF……,进入对话框如图1-2-10所示。

图1-2-8

打开波形输入编图1-2-9波形编辑器窗口

(3在Type区选择Inputs和outputs,单击List按钮,则在Availablenodes&Groups中出现所有输入、输出节点名称,选择需要仿真的节点名称,单击=>按钮,则它们被添加到SelectedNodes&Groups中,OK。

2.编辑输入节点波形

(1在图1-2-11所示的界面中对输入节点波形进行编辑,可以设置的项有:

在菜单

Options中选择SnaptoGrid(画线时网格对齐、ShowGrid(显示网格,并打开GridSize…..,设置网格大小(如20.0ns,并点击file/EndTime设置模拟时间的长短(如2s。

(2用波形绘制工具条绘制输入节点a,b,c的波形。

(3选File\save保存文件,生成扩展名为.scf的波形文件。

3.时序模拟仿真

(1选择菜单Max+plusII\Simulator,界面如图1-2-12所示;

(2单击Start,开始模拟仿真;

(3仿真完毕后,单击OpenSCF,打开仿真结果,如图1-2-13所示。

分析仿真结果可见,

波形图满足表1-2-1所列的3线-8线译码器的真值表(注意有仿真延时和竞争冒险现象。

图1-2-11波形编辑选项

波形绘制

工具条

图1-2-10添加输入、输出节点

图1-2-12时序模拟仿真界面

表

步骤10、管脚分配

仿真模拟正确后,就可以准备下载至PLD芯片进行硬件验证了。

在下载前需要进行管脚分配,启动MAX+plusII\FloorplanEditor菜单,则显示该设计项目的信号列表和目标芯片的管脚图,如图根据EPF10K10与外部器件管脚分配表

1-2-14所示。

用手动方式完成管脚分配。

过程如下:

(1按键,所有的输入、输出口出现在UnassignedNodes栏内,用户可以用

手动方式分配管脚。

(2用鼠标左键按住某输入/输出口名称,拖到下面芯片的某一管脚上,松开鼠标,便完成一个管脚的分配。

(3按键,软件自动分配管脚。

注意:

芯片上有一些特定功能的管脚,进行管脚编辑时一定要注意不能使用它们。

另外,在实验步骤3中若选择器件为Auto,则不允许对管脚进行再分配。

管脚分配时选择手动分配管脚。

输入逻辑信号a,b,c只能分配给27、28、29……中的任三个管脚与信号开关相连,输出电平y0,y1,……y7只能分配给16、17、18……中的任8个管脚与发光管相连。

(4管脚分配结束后,再进行一次编译。

图1-2-14管脚分配

表1.2.2EPF10K10与外部器件管脚分配表(5

步骤11、下载

(1用专用连接线将计算机并口与下载箱相连,打开实验箱电源;(2启动MAX+plusII\programmer菜单,出现图1-2-17的对话框。

(3如果是第一次使用该软件,启动Options\HardwareSetup菜单(见图1-2-18,在HardwareType中选择ByteBlaster(MV。

(4如果是以EPF10K10LC84-4为目标芯片,选中下载文件L38.sof,Configure即可完成下载。

(5如果是以EPM7128SLC84-6为目标芯片,选中下载文件L38.pof,Program键完成下载。

注意:

若下载后提示下载不成功信息,按以上各步检查是否设置正确,并检查计算机与实验箱硬件连接,排除故障,再次尝试下载。

步骤12、设计文件下载至PLD芯片后,根据步骤9管脚分配的结果,改变数据开关的电平,验证发光管的状态是否满足表1-2-1,硬件系统示意图如图1-2-19所示。

图1-2-15PLD引脚与外部人工连接

例1-2-2用VerilogHDL设计一个3线-8线译码器。

步骤1-3与原理图输入法时相同。

步骤4、启动File\New菜单,如图1-2-20,选择TextEditorFile,OK。

步骤5、在硬件描述语言输入界面下,键入VerilogHDL代码如下。

moduledecoder(out,in;output[7:

0]out;input[2:

0]in;reg[7:

0]out;always@(inbegincase(in

3'd0:

out=8'b00000001;3'd1:

out=8'b00000010;3'd2:

out=8'b00000100;3'd3:

out=8'b00001000;3'd4:

out=8'b00010000;3'd5:

out=8'b00100000;3'd6:

out=8'b01000000;3'd7:

out=8'b10000000;endcaseend

endmodule

图1-2-19三线-八线译码器硬件系统示意图

步骤6、保存设计文件

在菜单File\Saveas下保存文本文件,生成decoder.v。

编译、仿真、管脚分配、下载等步骤与图形输入法相同。

注意:

.v文件描述的功能模块可以生成一个符号,放在用户库中,供其它原理图输入文件调用,调用的方法与从器件库中取元器件的方法相同。

生成功能模块的方法为:

选择菜单file\createdefaultsymbol,经过与编译相同的过程后,生成的功能模块被放入用户库,如图1-2-21所示。

1.3计数器设计

例1-3-1用D触发器设计一个异步4

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 实验 指导 图文

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

1212中级汽车维修工考试试题三.docx

1212中级汽车维修工考试试题三.docx