verilog上机练习一二参考程序.docx

verilog上机练习一二参考程序.docx

- 文档编号:9102141

- 上传时间:2023-02-03

- 格式:DOCX

- 页数:17

- 大小:16.64KB

verilog上机练习一二参考程序.docx

《verilog上机练习一二参考程序.docx》由会员分享,可在线阅读,更多相关《verilog上机练习一二参考程序.docx(17页珍藏版)》请在冰豆网上搜索。

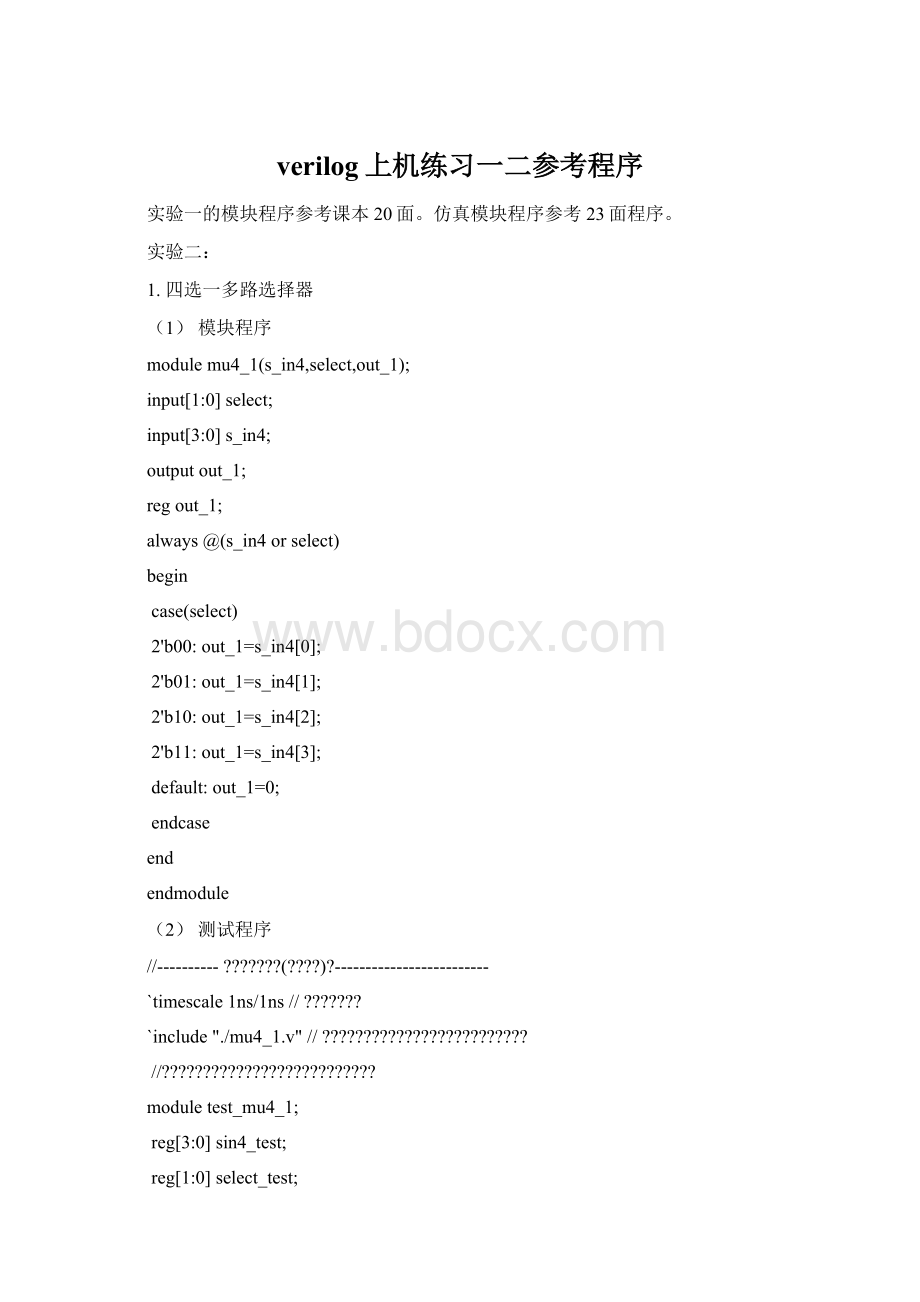

verilog上机练习一二参考程序

实验一的模块程序参考课本20面。

仿真模块程序参考23面程序。

实验二:

1.四选一多路选择器

(1)模块程序

modulemu4_1(s_in4,select,out_1);

input[1:

0]select;

input[3:

0]s_in4;

outputout_1;

regout_1;

always@(s_in4orselect)

begin

case(select)

2'b00:

out_1=s_in4[0];

2'b01:

out_1=s_in4[1];

2'b10:

out_1=s_in4[2];

2'b11:

out_1=s_in4[3];

default:

out_1=0;

endcase

end

endmodule

(2)测试程序

//----------?

?

?

?

?

?

?

(?

?

?

?

)?

-------------------------

`timescale1ns/1ns//?

?

?

?

?

?

?

`include"./mu4_1.v"//?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

//?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

moduletest_mu4_1;

reg[3:

0]sin4_test;

reg[1:

0]select_test;

regclock;

wireout1_test;

initial//initial?

?

?

?

?

?

?

?

?

?

?

?

begin

sin4_test=4'b0000;

select_test=2'b00;

clock=0;//?

?

?

?

?

?

?

?

end

always#50clock=~clock;//?

?

?

?

?

?

?

?

always@(posedgeclock)//?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

a?

b

begin

sin4_test={$random}%4;//?

?

a?

0?

?

1?

?

?

?

?

end

initial

begin

#20000select_test=2'b01;

#20000select_test=2'b10;

#20000select_test=2'b11;

#20000select_test=2'b00;

end//?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

initial

begin#100000$stop;end//?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

mu4_1m(.s_in4(sin4_test),.select(select_test),.out_1(out1_test));//?

?

?

?

?

?

?

t.m

endmodule

2.比较器(比较大于,小于,等于)

(1)模块程序

modulecompare_sbe(small_out,big_out,equal_out,a,b);

inputa,b;

outputequal_out,small_out,big_out;

assignequal_out=(a==b)?

1:

0;

assignbig_out=(a>b)?

1:

0;

assignsmall_out=(a 1: 0; endmodule (2)测试程序 //------------------------------------------------------------- //----------? ? ? ? ? ? ? (? ? ? ? )? `timescale1ns/1ns//? ? ? ? ? ? ? `include"./compare_sbe.v"//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? modulecompare_sbe_test; rega_test,b_test; wireequal_out,small_out,big_out; initial//initial? ? ? ? ? ? ? ? ? ? ? ? begin a_test=0; b_test=0; #100a_test=0;b_test=1; #100a_test=1;b_test=1; #100a_test=1;b_test=0; #100a_test=0;b_test=0; #100$stop;//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? end compare_sbem(.small_out(small_out),.big_out(big_out),.equal_out(equal_out),.a(a_test),.b(b_test));//? ? ? ? ? ? ? t.m endmodule 3.编码器 (1)模块程序 modulecode8_3(indata8,outdata3); input[7: 0]indata8; output[2: 0]outdata3; reg[2: 0]outdata3; always@(indata8) begin case(indata8) 8'b0000_0001: outdata3=3'd0; 8'b0000_0010: outdata3=3'd1; 8'b0000_0100: outdata3=3'd2; 8'b0000_1000: outdata3=3'd3; 8'b0001_0000: outdata3=3'd4; 8'b0010_0000: outdata3=3'd5; 8'b0100_0000: outdata3=3'd6; 8'b1000_0000: outdata3=3'd7; default: outdata3=3'd0; endcase end endmodule (2)测试程序 //------------------------------------------------------------- //----------? ? ? ? ? ? ? (? ? ? ? )? `timescale1ns/1ns//? ? ? ? ? ? ? `include"./code8_3.v"//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? modulecode8_3_test; reg[7: 0]indata8; wire[2: 0]outcode3; initial//initial? ? ? ? ? ? ? ? ? ? ? ? begin #100indata8=8'b0000_0001; #100indata8=8'b0000_0010; #100indata8=8'b0000_0100; #100indata8=8'b0000_1000; #100indata8=8'b0001_0000; #100indata8=8'b0010_0000; #100indata8=8'b0100_0000; #100indata8=8'b1000_0000; #100indata8=8'b1100_0100; #100indata8=8'b1100_0101; #100$stop;//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? end code8_3m(.indata8(indata8),.outdata3(outcode3));//? ? ? ? ? ? ? t.m endmodule 4.译码器 (1)模块程序 moduledecode3_8(indata3,outdata8); input[2: 0]indata3; output[7: 0]outdata8; reg[7: 0]outdata8; always@(indata3) begin case(indata3) 3'd0: outdata8=8'b0000_0001; 3'd1: outdata8=8'b0000_0010; 3'd2: outdata8=8'b0000_0100; 3'd3: outdata8=8'b0000_1000; 3'd4: outdata8=8'b0001_0000; 3'd5: outdata8=8'b0010_0000; 3'd6: outdata8=8'b0100_0000; 3'd7: outdata8=8'b1000_0000; default: outdata8=8'b0000_0000; endcase end endmodule (2)测试程序 //------------------------------------------------------------- //----------? ? ? ? ? ? ? (? ? ? ? )? `timescale1ns/1ns//? ? ? ? ? ? ? `include"./decode3_8.v"//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? moduledecode3_8_test; reg[2: 0]indata3; wire[7: 0]outcode8; initial//initial? ? ? ? ? ? ? ? ? ? ? ? begin #100indata3=3'd1; #100indata3=3'd2; #100indata3=3'd3; #100indata3=3'd4; #100indata3=3'd5; #100indata3=3'd6; #100indata3=3'd7; #100indata3=3'd0; #100$stop;//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? end decode3_8m(.indata3(indata3),.outdata8(outcode8));//? ? ? ? ? ? ? t.m endmodule 5.触发器 (1)模块程序 moduledbuff(d,clk,en,rst,q); inputd,clk,en,rst; outputq; regq; always@(posedgeclkornegedgerst) begin if(! rst) begin q<=0; end else begin if(! en) begin q<=0; end else begin q<=d; end end end endmodule (2)测试程序 //----------? ? ? ? ? ? ? (? ? ? ? )? ------------------------- `timescale1ns/1ns//? ? ? ? ? ? ? `include"./dbuff.v"//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? moduledbuff_test; regd_test,clk_test,en_test,rst_test; regclock; wireq_test; initial//initial? ? ? ? ? ? ? ? ? ? ? ? begin d_test=1'b0; clk_test=1'b0; en_test=1'b0; rst_test=1'b0; clock=0;//? ? ? ? ? ? ? ? end always#50clock=~clock;//? ? ? ? ? ? ? ? always@(posedgeclock) begin clk_test=~clk_test; #1d_test={$random}%2; end initial begin #100rst_test=1'b1; #100rst_test=1'b0; #200rst_test=1'b1; #1000en_test=1'b0; #1000en_test=1'b1; end//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? initial begin#100000$stop;end//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? dbuffm(.d(d_test),.clk(clk_test),.en(en_test),.rst(rst_test),.q(q_test));//? ? ? ? ? ? ? t.m endmodule 6.移位寄存器 (1)模块程序 moduleshift_buff(indata1,clk,rst,outdata8); inputindata1,clk,rst; output[7: 0]outdata8; reg[7: 0]outdata8; always@(posedgeclkornegedgerst) begin if(! rst) begin outdata8<=8'b0000_0000; end else begin outdata8=outdata8<<1; outdata8[0]=indata1; end end endmodule (2)测试程序 //----------? ? ? ? ? ? ? (? ? ? ? )? ------------------------- `timescale1ns/1ns//? ? ? ? ? ? ? `include"./shift_buff.v"//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? moduleshift_test; regindata1_test,clk_test,rst_test; regclock; wire[7: 0]outdata8_test; initial//initial? ? ? ? ? ? ? ? ? ? ? ? begin indata1_test=1'b0; clk_test=1'b0; rst_test=1'b0; clock=0;//? ? ? ? ? ? ? ? end always#50clock=~clock;//? ? ? ? ? ? ? ? always@(posedgeclock) begin clk_test=~clk_test; #1indata1_test={$random}%2; end initial begin #100rst_test=1'b1; #100rst_test=1'b0; #200rst_test=1'b1; end//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? initial begin#100000$stop;end//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? shift_buffm(.indata1(indata1_test),.clk(clk_test),.rst(rst_test),.outdata8(outdata8_test));//? ? ? ? ? ? ? t.m endmodule 7.计数器 (1)模块程序 modulecounter4(load_data,rst,clk,load,count_data,cin); inputclk,rst,load; input[3: 0]load_data; output[3: 0]count_data; outputcin; reg[3: 0]count_data; regcin; always@(posedgeclkornegedgerst) begin if(! rst) begin count_data<=0; cin<=0; end else begin if(load) begin count_data<=load_data; cin<=0; end else begin if(count_data==4'hf) begin cin<=1; count_data<=0; end else begin count_data<=count_data+1; cin<=0; end end end end endmodule (2)测试程序 `timescale1ns/1ns//? ? ? ? ? ? ? `include"./counter4.v"//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? modulecounter4_test; regclk_test,rst_test,load_test,clock; reg[3: 0]load_data_test; wire[3: 0]count_data_test; wirecin_test; initial//initial? ? ? ? ? ? ? ? ? ? ? ? begin load_data_test=4'b1101; load_test=1'b0; rst_test=0;//? ? ? ? ? ? ? ? clk_test=0; clock=0; end always#50clock=~clock;//? ? ? ? ? ? ? ? always@(posedgeclock) begin clk_test=~clk_test; end initial begin #100rst_test=1'b1; #100rst_test=1'b0; #200rst_test=1'b1; #100load_test=1'b0; #100load_test=1'b1; #200load_test=1'b0; end//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? initial begin#100000$stop;end//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? counter4m(.load_data(load_data_test),.rst(rst_test),.clk(clk_test),.load(load_test),.count_data(count_data_test),.cin(cin_test));//? ? ? ? ? ? ? t.m endmodule 8.分频器 (1)模块程序 moduleclk10_div(clk10,rst,clk1); inputclk10,rst; outputclk1; regclk1; reg[2: 0]count; always@(posedgeclk10ornegedgerst) begin if(! rst) begin clk1<=0; count<=0; end else begin if(count==3'd4) begin count<=0; clk1<=~clk1; end else begin count<=count+1; end end end endmodule (2)测试程序 `timescale1ns/1ns//? ? ? ? ? ? ? `include"./clk10_div.v"//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? moduleclk10_div_test; regclk10_test,rst_test; regclock; wireclk1_test; initial//initial? ? ? ? ? ? ? ? ? ? ? ? begin clk10_test=1'b0; rst_test=1'b0; clock=0;//? ? ? ? ? ? ? ? end always#50clock=~clock;//? ? ? ? ? ? ? ? always@(posedgeclock) begin clk10_test=~clk10_test; end initial begin #100rst_test=1'b1; #100rst_test=1'b0; #200rst_test=1'b1; end//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? initial begin#100000$stop;end//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? clk10_divm(.clk10(clk10_test),.rst(rst_test),.clk1(clk1_test));//? ? ? ? ? ? ? t.m endmodule 9.指令译码器 (1)模块程序 modulecode_cal(data_a,data_b,out_data,oprate); input[7: 0]data_a,data_b; input[2: 0]oprate; output[7: 0]out_data; reg[7: 0]out_data; reg[2: 0]outdata3; parameterplus=0,minus=1,band=2,bor=3,unegate=4; always@(oprate,data_a,data_b) begin case(oprate) plus: out_data=data_a+data_b; minus: out_data=data_a-data_b; band: out_data=data_a&data_b; bor: out_data=data_a|data_b; unegate: out_data=~data_a; default: out_data=3'd0; endcase end endmodule (2)测试程序 //------------------------------------------------------------- //----------? ? ? ? ? ? ? (? ? ? ? )? `timescale1ns/1ns//? ? ? ? ? ? ? `include"./code_cal.v"//? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? //? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? modulecode_cal_test; reg[7: 0]data_a_test,data_b_test; reg[2: 0]oprate_test

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- verilog 上机 练习 一二 参考 程序

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《Java程序设计》考试大纲及样题试行.docx

《Java程序设计》考试大纲及样题试行.docx