EDA课程设计EDA数字系统综合设计与实践.docx

EDA课程设计EDA数字系统综合设计与实践.docx

- 文档编号:8859647

- 上传时间:2023-02-02

- 格式:DOCX

- 页数:28

- 大小:1.48MB

EDA课程设计EDA数字系统综合设计与实践.docx

《EDA课程设计EDA数字系统综合设计与实践.docx》由会员分享,可在线阅读,更多相关《EDA课程设计EDA数字系统综合设计与实践.docx(28页珍藏版)》请在冰豆网上搜索。

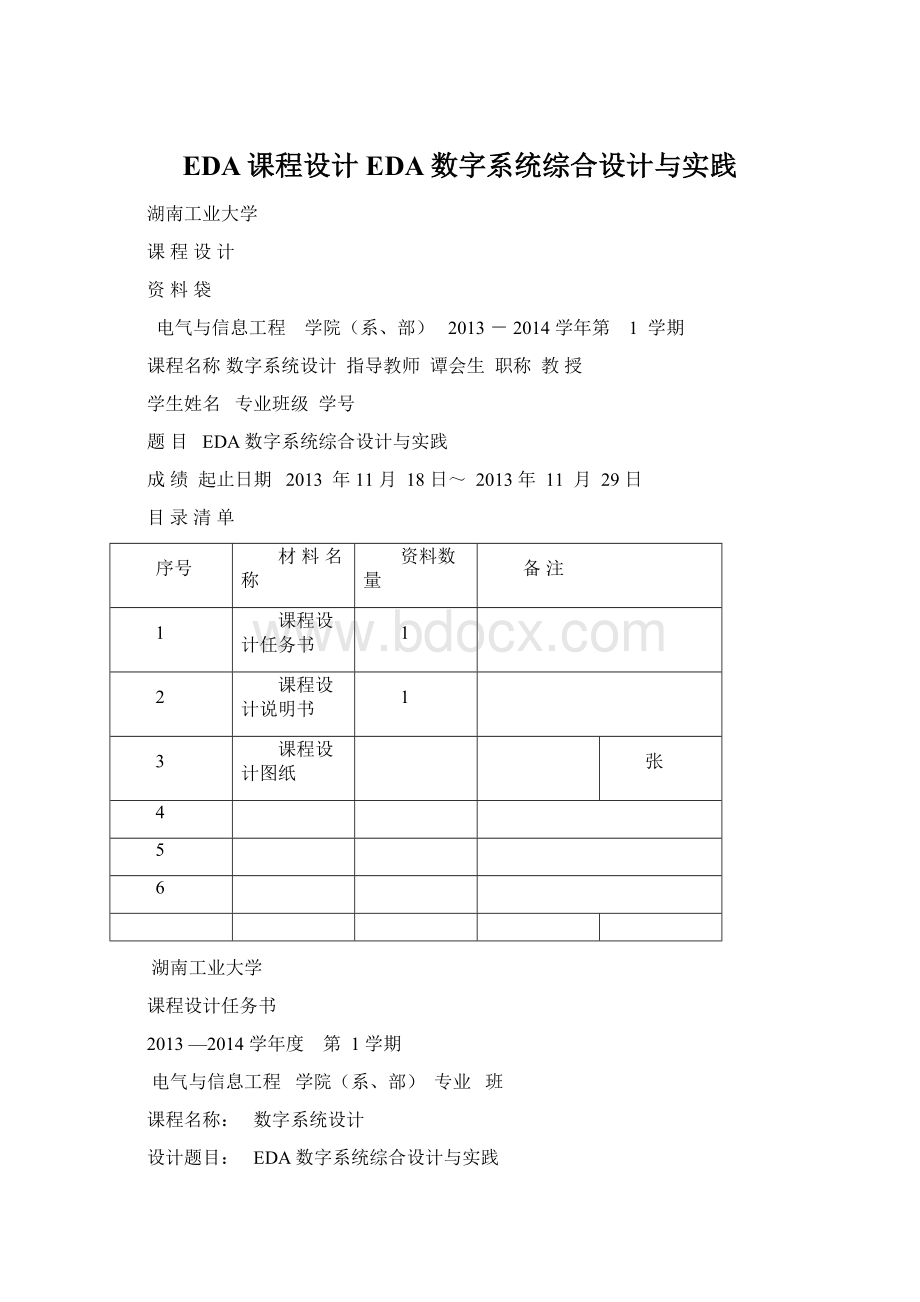

EDA课程设计EDA数字系统综合设计与实践

湖南工业大学

课程设计

资料袋

电气与信息工程学院(系、部)2013-2014学年第1学期

课程名称数字系统设计指导教师谭会生职称教授

学生姓名专业班级学号

题目EDA数字系统综合设计与实践

成绩起止日期2013年11月18日~2013年11月29日

目录清单

序号

材料名称

资料数量

备注

1

课程设计任务书

1

2

课程设计说明书

1

3

课程设计图纸

张

4

5

6

湖南工业大学

课程设计任务书

2013—2014学年度 第1学期

电气与信息工程学院(系、部)专业班

课程名称:

数字系统设计

设计题目:

EDA数字系统综合设计与实践

完成期限:

2013年11月18日~2013年11月29日共2周

内

容

及

任

务

数字系统设计,就是要求学生利用EDA技术进行综合性的数字电子系统设计,培养学生综合应用能力、独立设计与安装调试能力,并树立工程设计观念。

具体任务如下:

(1)综合计时系统的设计:

包括系统设计原理,VHDL等程序设计,时序仿真与分析,逻辑综合与分析、硬件验证等;

(2)SOBEL图像边缘检测器的设计:

包括系统设计思想原理,VHDL等程序设计,时序仿真与分析,逻辑综合与分析等;

各子课题的设计具体要求详见附件一。

进

度

安

排

起止日期

工作内容

第13周周一上午08:

00-12:

00

布置任务,讲解课题设计要求(电205)

第13周周一晚上18:

00-22:

00

综合计时系统的设计(电205)

第13周周二上午08:

00-12:

00

综合计时系统的设计(电205)

第13周周二晚上18:

00-22:

00

综合计时系统的设计(电205)

第13周周三晚上19:

00-22:

00

SOBEL图像边缘检测器的设计(电205)

第13周周四上午08:

00-12:

00

SOBEL图像边缘检测器的设计(电205)

第13周周四下午14:

00-18:

00

SOBEL图像边缘检测器的设计(电205)

其它时间

学生自行查找资料,自行进行实践,撰写报告

主

要

参

考

资

料

[1]谭会生,张昌凡.EDA技术及应用(第三版)[M].西安:

西安电子科技大学出版社,2011

[2]谭会生,瞿遂春.EDA技术综合应用实例与分析[M].西安:

西安电子科技大学出版社,2004

指导教师(签字):

谭会生2013年9月15日

系(教研室)主任(签字):

谭会生2013年9月15日

附件一:

各设计子课题的具体设计要求

1.综合计时系统的设计:

设计一个综合性的计时系统,要求能实现年、月、日、时、分、秒及星期的计数等综合计时功能,同时将计时结果通过15个七段数码管实现显示,并且可通过两个设置键,在计时过程中,对计时系统的有关参数进行调整。

具体系统功能面板如图1所示。

图1系统功能面板

2.SOBEL图像边缘检测器的设计

边缘可定义为图像中灰度发生急剧变化的区域边界,它是图像最基本的特征,是图像分析识别前必不可少的环节,是一种重要的图像预处理技术。

边缘检测主要就是(图像的)灰度变化的度量、检测和定位,它是图像分析和模式识别的主要特征提取手段,它在计算机视觉、图像分析等应用中起着重要的作用,是图像分析与处理中研究的热点问题。

在过去的20年里产生了许多边缘检测器,如Rorberts算子,Sobel算子,Prewitt算子,Laplacian算子等。

由于Sobel算法只涉及加法操作,但却可以得到很好的划分效果,因而是图像处理系统中最常用的边缘检测算法。

Sobel算法包括带4个3×3掩码的输入图像数据,即Sobel算子,它设置权重来检测水平、垂直、左对角、右对角各个不同方向上密度幅度的不同。

这个过程通常被称为过滤。

我们来看像素窗口(3×3),如图2所示。

水平、垂直、左对角、右对角各图像方向上密度幅度的变化可以用如下算子进行计算:

Q0

Q3

Q6

Q1

[i,j]

Q7

Q2

Q5

Q8

H=(Q0+2Q3+Q6)-(Q2+2Q5+Q8);V=(Q0+2Q1+Q2)-(Q6+2Q7+Q8);

DR=(Q1+2Q0+Q3)-(Q5+2Q8+Q7);DL=(Q1+2Q2+Q5)-(Q3+2Q6+Q7);

H,V,DL,DR这四个参数用于计算梯度大小和方向。

图2图像窗口像素的排列

对梯度大小的一个普遍估计值为:

Magnitude=Max(H,V,DR,DL)。

我们通过对图像灰度作直方图分析后,便可以给出区分度阀值

Threshold,区分度阀值往往要借助一定的经验并需要反复调整。

如果Magnitude大于Threshold,则该像素被声明为边界像素,否则为一般像素。

本课题就是要求使用LPM兆功能块设计和VHDL程序设计相结合的方式或全部采用VHDL程序设计方式,用FPGA/CPLD实现Sobel算法。

附件二:

课题设计报告要求

课程设计报告包括如下内容:

一、系统设计要求;二、系统设计原理;三、VHDL源程序;四、时序仿真与分析;五、逻辑综合与分析。

并要求按如下规定的格式打印好:

打印用纸A4,主标题宋体3号,节标题宋体4号,小标题宋体小4号,正文宋体5号每页39行39个汉字,页边距上、下均为2.5CM,左、右均为2CM,左右对称。

图、表要有标号及名称,如:

图1.1XXXX,表1.1XXXX;公式要有编号,如……(1.1)。

附件三

数字系统设计课程

设 计 说 明 书

EDA数字系统综合设计与实践

起止日期:

2013年11月18日~2013年11月29日共2周

学生姓名

班级

学号

成绩

指导教师(签字)

电气与信息工程学院

2013年月日

一、综合计时系统的设计

1.系统设计原理

设计一个综合性的计时系统,要求能实现年、月、日、时、分、秒及星期的计数等综合计时功能,同时将计时结果

通过15个七段数码管实现

显示,并且可通过两个设置

键,在计时过程中,对计时

系统的有关参数进行调整。

如图所示,该计时系统的设

计共分为三个主要模块:

综

合计时电路(ITC)、显示控制电路(DUC)及调整控制电路(ATCC)。

其具体模块功能在此不再详细描述。

综合计时电路(ITC)可分为计秒电路、计分电路、计时电路、计星期电路、计日电路、计月电路和计年电路,共七个子模块。

显示控制电路(DUC)使用的是十五个七段显示数码管。

它可分为两个子模块:

(1).显示控制电路:

负责完成数据选择扫描及数码管位选择信号的产生,数据扫描选择输出,对于选择的数据进行BCD码转换等功能。

(2).显示译码电路:

将用于显示的BCD码数据进行译码。

调整控制电路(ATCC)是通过模式和调

整两个外部键完成。

其中模式键负责切换正

常时间计数模式和时间调整模式,调整键负

责在时间调整模式下,对当前模式计时结果

进行调整。

在模式选择过程中,被选择到的

调整模式所对应的发光二极管会被点亮。

而

正常模式中,7个发光二极管都不会被点亮

。

模式调整的VHDL程序主要是通过一个状

态机来实现。

调整模式切换顺序(图)

2.VHDL程序设计

在这次课程设计中,我们运用学习过的VHDL语言编译本次课程设计相关功能的模块。

1.CNT7.VHD

--CNT7.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT7IS

PORT

(LD:

INSTD_LOGIC;

CLK:

INSTD_LOGIC;

DATA:

INSTD_LOGIC_VECTOR(2DOWNTO0);

NUM:

BUFFERSTD_LOGIC_VECTOR(2DOWNTO0));

ENDENTITYCNT7;

ARCHITECTUREARTOFCNT7IS

BEGIN

PROCESS(CLK,LD)IS

BEGIN

IF(LD='0')THEN

NUM<=DATA;

ELSIFCLK'EVENTANDCLK='1'THEN

IFNUM="111"THEN

NUM<="001";

ELSE

NUM<=NUM+1;

ENDIF;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREART;

CNT7.VHD在程序中是实现‘计星期’功能。

由下级进位信号作为该级输入信号。

并有可输入输出端口实现了在调整模式中的算法‘人机交互’。

实现调整功能。

由于CNT12.VHD、CNT24.VHD及CNT100.VHD在形式上与上述内容类似,分别以‘计月、计时、计年’的功能,且都能实现调整模式中的算法‘人机交互’。

因此不再赘谈。

2.DECODER3_8.VHD

--DECODER3_8.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDECODER3_8IS

PORT(

DIN:

INSTD_LOGIC_VECTOR(2DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDDECODER3_8;

ARCHITECTURERTLOFDECODER3_8IS

BEGIN

DOUT<="10000000"WHEN(DIN="111")ELSE

"01000000"WHEN(DIN="110")ELSE

"00100000"WHEN(DIN="101")ELSE

"00010000"WHEN(DIN="100")ELSE

"00001000"WHEN(DIN="011")ELSE

"00000100"WHEN(DIN="010")ELSE

"00000010"WHEN(DIN="001")ELSE

"00000001";

ENDRTL;

DECODER3_8.VHD实现的是显示调整模式的发光二极管亮灭逻辑,通过该源程序,我们能更为直观的选择、调整计时系统中相应的模式。

3.DECODER4_7.VHD

--DECODER4_7.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDECODER4_7IS

PORT

(BCD4:

INSTD_LOGIC_VECTOR(3DOWNTO0);

SEGOUT7:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDDECODER4_7;

ARCHITECTUREARTOFDECODER4_7IS

BEGIN

SEGOUT7<="0111111"WHEN(BCD4="0000")ELSE

"0000110"WHEN(BCD4="0001")ELSE

"1011011"WHEN(BCD4="0010")ELSE

"1001111"WHEN(BCD4="0011")ELSE

"1100110"WHEN(BCD4="0100")ELSE

"1101101"WHEN(BCD4="0101")ELSE

"1111101"WHEN(BCD4="0110")ELSE

"0000111"WHEN(BCD4="0111")ELSE

"1111111"WHEN(BCD4="1000")ELSE

"1100111"WHEN(BCD4="1001")ELSE

"0000000";

ENDARCHITECTUREART;

DECODER4_7.VHD将显示控制器(DUC)中输出的BCD码进行译码后作为七段共阴极发光二极管的输入信号,实现了最终的阿拉伯数字显示在系统功能面板上。

(注:

该显示部分由十五个共阴极发光二极管构成。

)

3.时序仿真与分析

CNT60.VHD模块仿真波形如下:

CNT60.VHD实现了从0到59的循环计数,每实现一次59到0的计数动作,计数模块输出一个进位信号。

当LD端有低电平输入时,说明置数信号(LD)有效,模块将预置数(DATA)56送入计数结果(NUM)中去,计数模块从56开始重新计数。

当计数结果(NUM)从零开始计数时,产生一个进位信号(CO)。

CNT30.VHD的仿真波形如下:

在正常计数过程中,模块实现了从0到最大天数(MAX_DAYS)的循环计数,每实现一次最大天数(MAX_DAYS)到0的计数动作,计数模块输出一个进位信号。

当LD端有低电平输入时,说明置数信号(LD)有效,模块将预置数(DAY)20送入计数结果(NUM)中去,计数模块从20开始重新计数。

.CNT7.VHD波形图如图:

该图实现的是计星期,NUM为输出端(设置为可输入输出端口),DATA为输入端,上级输出信号CO作为该级别CLK的输入信号,LD为置位信号。

如波形所示,该部分实现了周一到周日的循环。

完成预定要求。

CNT12.VHD波形图如图:

该图在功能上与上图是相应的计月份。

实现了从一月份到十二月份的循环。

完成预定要求。

.VHD24.VHD波形图如图:

该图在功能上是实现计小时。

实现了从1点(时刻)到24点(时刻)的循环。

完成预定要求。

DECODER3_8.VHD波形如图:

该图在功能上是通过译码后实现调整模式选择,即系统功能面板上的调整模式切换。

从输出波形上来说,输出波形有且只有一位为高电平,在共阴极二极管会显示该模式正在处理。

完成预定要求。

DECODER4_7.VDH波形如图:

该图在功能上是将BCD码译码到数码显示管上相应的要求数码。

由波形图可知,该图是正确的。

(如输出‘0111111’B显示的是‘0’D;‘0000110’B显示的是‘1’D等。

)完成预期要求。

4.逻辑综合与分析

综合逻辑组合图如图:

该图为调整控制电路(ATCC),通过KEY进行调整模式的选择;CLK_KEY进行具体调节相应的秒、分、时、日、月、年等模式。

下图为整个计时系统的运算部分。

整体由上一级进位信号作为下一级的是输入信号。

实现相关的关联。

由于界面过小,因此无法到完整的计数部分的原理图。

下图是整体电路图中的显示控制部分及译码器部分。

该部分实现的是相关的显示在系统功能面板上的一系列LED显示管。

最后就是控制显示面板上的模式选择发光二极管部分的连线。

该部分的输入线连接的是调整控制电路的相应SEC_EN、MIN_IN等端口。

表明控制调整模式的选择。

最后是整体波形的仿真图:

由于相关的波形的设置较为复杂,就简略的设置了一下相应的波形,确保了输出显示。

然而在模式选择的输出端却有所欠缺,由于时间较为紧迫,因此没有具体去优化该输入信号的给与。

在整体设计中,此次课程设计基本成功。

5.硬件验证及结果

此次课程设计,由于实验设备的有限,以及时间的欠缺。

并没有实现其下载到开发板上验证。

6.设计收获与体会

这次最大的收获就是学会了很系统地去解决一个实际问题,学会了巧妙运用模块化的思想。

在整个电路设计与实现中,最成功的地方就是有条理地将功能细化,分成一个一个小的功能来实现。

没做好一个小功能实现的电路,就将其集成为一块具有此功能的芯片,这样,在之后的电路连接中就只要将这块芯片接入即可,最后就这样一级一级地将电路集成,最后生成的电子钟电路就只是一块芯片,只要加一些其他外部控制开关与显示电路就能实现此多功能电子钟的各功能。

经过几天的辛苦调试,经过仿真终于能达到们所需的设计要求,虽然最终的设计还存在些小瑕疵.但毕竟是第一次做,我们还是比较满意的。

本次设计让我们那发现了自己很多的不足,对以前所学过的知识理解得不够深刻,掌握得不够牢固。

可以说这次设计的综合计时系统还是比较成功的,虽然这次设计的综合计时系统不是很完美,在设计中遇到了很多的难题,最后在老师的辛勤的指导下,终于迎刃而解.还是觉得不错的,终于觉得平时所学的知识有了实用的价值,达到了理论与实际相结合的目的,不仅学到了不少知识,而其锻炼了自己的能力,使自己对以后的路有了更加清楚的认识,同时,对未来有了更多的信心。

最后,对给过我帮助的所有同学和老师再次表示衷心的感谢!

二、SOBEL图像边缘检测器的设计

1.系统设计原理

该系统的主要设计原理是采用现代电子设计的最新技术——EDA技术,使用高速可编程逻辑器件PFGA/CPLD自行开发有关处理芯片成了一种全新的解决方案。

如下组成框图所示:

DSP+FPGA/CPLD图像主处理器

其中图像传感器CCD的功能是获取外界图像的各个像素点灰度值;图像主处理器采用数字信号处理器DSP,主要负责对图像传感器传送的灰度信息进行存储,并负责调用协处理器进行边界像素判别,找出我们感兴趣的目标对象,从而得到该对象的运动信息,以便控制执行装置进行位置跟踪;边缘检测协处理器为FPGA/CPLD,主要是完成主处理器传送过来的像素的边界判别,并把处理结果返回到主处理器中。

在本系统中,各项设计指标为:

数据吞吐量>10Mb/s;动态响应时间<100ms/frame。

主处理器初步选用德州公司的DSP芯片TMS320C5402,协处理器拟采用ALTERA公司的FLEX10K20。

图像处理系统接口关系如下图所示:

边缘可定义为图像中灰度发生急剧变化的区域边界,它是图像最基本的特征,是图像分析识别前必不可少的环节,是一种重要的图像预处理技术。

边缘检测主要就是(图像的)灰度变化的度量、检测和定位,它是图像分析和模式识别的主要特征提取手段,它在计算机视觉、图像分析等应用中起着重要的作用,是图像分析与处理中研究的热点问题。

在过去的20年里产生了许多边缘检测器,如Rorberts算子,Sobel算子,Prewitt算子,Laplacian算子等。

由于Sobel算法只涉及加法操作,但却可以得到很好的划分效果,因而是图像处理系统中最常用的边缘检测算法。

Q0

Q3

Q6

Q1

[i,j]

Q7

Q2

Q5

Q8

Sobel算法包括带4个3×3掩码的输入图像数据,即Sobel算子,它设置权重来检测水平、垂直、左对角、右对角各个不同方向上密度幅度的不同。

这个过程通常被称为过滤。

我们来看像素窗口(3×3),如图1所示。

水平、垂直、左对角、右对角各图像方向上密度幅度的变化可以用如下算子进行计算:

H=(Q0+2Q3+Q6)-(Q2+2Q5+Q8);V=(Q0+2Q1+Q2)-(Q6+2Q7+Q8);

DR=(Q1+2Q0+Q3)-(Q5+2Q8+Q7);DL=(Q1+2Q2+Q5)-(Q3+2Q6+Q7);

H,V,DL,DR这四个参数用于计算梯度大小和方向。

我们通过对图像灰度作直方图分析后,便可以给出区分度阀值像素框

Threshold,区分度阀值往往要借助一定的经验并需要反复调整。

如果Magnitude大于Threshold,则该像素被声明为边界像素,否则为一般像素。

本课题就是要求使用LPM兆功能块设计和VHDL程序设计相结合的方式或全部采用VHDL程序设计方式,用FPGA/CPLD实现Sobel算法。

运用CPLD/FPGA设计有关图像处理模块,对象系统速度改善是非常明显:

处理一帧图像的时间为800*600*80ns=38.4ms,结果处理速度比DSP高了约两个数量级。

2.VHDL程序或原理图设计

该课题主要涉及的是LPM兆功能模块的定制。

其VHDL程序有:

COUNTER.VHD,COMPARE.VHD,RESULT.VHD,REG.VHD及CNT3.VHD。

--COUNTER.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYCOUNTERIS

PORT(CLK:

INSTD_LOGIC;

CO:

OUTSTD_LOGIC);

ENDENTITYCOUNTER;

ARCHITECTUREARTOFCOUNTERIS

SIGNALCNT:

NATURALRANGE0TO2;

BEGIN

PROCESS(CLK)IS

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFCNT=1THEN

CNT<=0;

CO<='1';

ELSE

CNT<=CNT+1;

CO<='0';

ENDIF;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREART;

该程序实现的是产生一个二分频的波形作为输入信号。

--COMPARE.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCOMPAREIS

GENERIC(SIZE:

INTEGER:

=11);

PORT(DAT1,DAT2:

INSTD_LOGIC_VECTOR(SIZEDOWNTO1);

MAX:

OUTSTD_LOGIC_VECTOR(SIZEDOWNTO1));

ENDENTITYCOMPARE;

ARCHITECTUREARTOFCOMPAREIS

BEGIN

PROCESS(DAT1,DAT2)

BEGIN

IF(DAT1(SIZE-1DOWNTO1)>DAT2(SIZE-1DOWNTO1))THEN

MAX<=DAT1;

ELSEMAX<=DAT2;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREART;

该程序实现的是两个数据的比较。

--RESULT.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYRESULTIS

GENERIC(SIZE:

INTEGER:

=11);

PORT(CLK:

INSTD_LOGIC;

H,V,DR,DL:

INSTD_LOGIC_VECTOR(SIZEDOWNTO1);

THRESHOLD:

INSTD_LOGIC_VECTOR(8DOWNTO1);

MAX:

INSTD_LOGIC_VECTOR(SIZEDOWNTO1);

MAGOUT:

OUTSTD_LOGIC;

DIR:

OUTSTD_LOGIC_VECTOR(3DOWNTO1));

ENDENTITYRESULT;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 课程设计 数字 系统 综合 设计 实践

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx