QuartusII7使用安装剖析.docx

QuartusII7使用安装剖析.docx

- 文档编号:8677752

- 上传时间:2023-02-01

- 格式:DOCX

- 页数:15

- 大小:524.56KB

QuartusII7使用安装剖析.docx

《QuartusII7使用安装剖析.docx》由会员分享,可在线阅读,更多相关《QuartusII7使用安装剖析.docx(15页珍藏版)》请在冰豆网上搜索。

QuartusII7使用安装剖析

QuartusII7.2使用图解

一.QuartusII7.2启动

◆

方法一、直接双击桌面上的图标,可以打开QuartusII软件;

◆方法二、执行:

〖开始〗→〖程序〗→〖Altera〗→〖QuartusII7.2〗→〖QuartusII7.2TalkBackInstall〗菜单命令,可以打开软件。

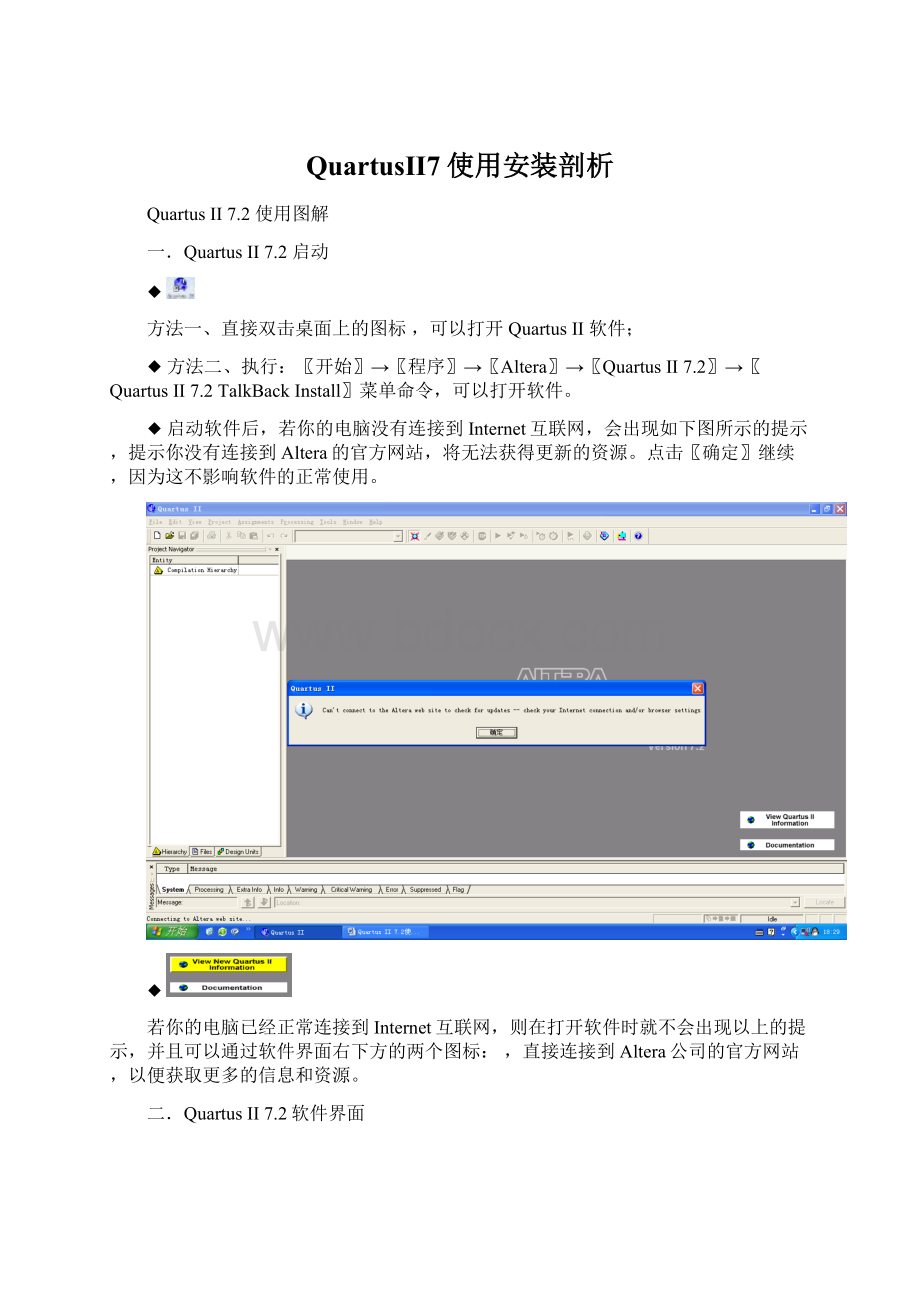

◆启动软件后,若你的电脑没有连接到Internet互联网,会出现如下图所示的提示,提示你没有连接到Altera的官方网站,将无法获得更新的资源。

点击〖确定〗继续,因为这不影响软件的正常使用。

◆

若你的电脑已经正常连接到Internet互联网,则在打开软件时就不会出现以上的提示,并且可以通过软件界面右下方的两个图标:

,直接连接到Altera公司的官方网站,以便获取更多的信息和资源。

二.QuartusII7.2软件界面

QuartusII7.2软件的默认启动界面如下图所示,由标题栏、菜单栏、常用工具栏、资源管理窗口、程序编译或仿真运行状态的显示窗口、程序编译或仿真的结果显示窗口和工程编辑工作区组成。

三.QuartusII7.2软件使用

1.新建项目工程

使用QuartusII7.2设计一个数字逻辑电路,并用时序波形图对电路的功能进行仿真,同时还可以将设计正确的电路下载到可编程的逻辑器件(CPLD、FPGA)中。

因软件在完成整个设计、编译、仿真和下载等这些工作过程中,会有很多相关的文件产生,为了很好的管理这些设计文件,我们在设计电路之前,先要建立一个项目工程,并设置好这个工程能正常工作的相关条件和环境。

建立工程的方法和步骤如下:

(1)先在电脑本地硬盘空间建一个用于保存项目

的文件夹,文件夹的命名及其保存的路径不能有中文字符。

(2)如右图点击:

File菜单,选择下拉列表中的

NewProjectWizard...命令,打开建立项目工程的对话框。

如下图,出现第一个对话框,让你选择项目工程保

存位置、定义项目名称以及设计文件顶层实体名称。

第一栏选择项目工程保存的位置,方法是点击按钮,指向刚才我们在第一步建立的文件夹。

如右图,第二栏(项目工程

名称)和第三栏(设计实体

名称)软件会默认为与之前

建立的文件夹名称一致。

没有特别需要,我们一般选择

软件的默认,不必特意去修改。

需要注意的是:

以上名称的命

名中不能出现中文字符,否则

软件的后续工作会出错。

完成以上命名工作后,点击

Next,进入下一步。

如下图对话框:

这一步的工作是让你将之前已经设计好的工程文件添加到本项目工程里来,我们之前没有设计好的文件,因此就跳过这一步,直接点Next,再进入下一步。

如下图对话框:

这一步的工作是让你选择好设计文件下载所需要的硬件器件型号,现在我们只做简单的电路设计和仿真,随便指定一个就可以了。

以后我们做课程设计或学习《可编程逻辑器件》这门课后,等熟悉了CPLD或FPGA器件以后再根据开发板的器件选择合适的器件型号。

点击Next,进入下一步。

如下图对话框:

这一步是让你选择第三方开发工具,我不需要,直接点击Next,进入下一步。

出现下图页面:

以上页面显示刚才我们所做的项目工程设置内容的“报告”。

点击Finish,完成新建项目工程的任务。

2.新建设计文件

建立好项目工程后,接下来可以开始建立设计文件了。

QuartusII7.2软件可以用两种方法来建立设计文件,一种是利用软件自带的元器件库,以编辑电路原理图的方式来设计一个数字逻辑电路,另一种方法是应用硬件描述语言(如VHDL或Verilog)以编写源程序的方法来设计一个数字系统电路。

作为初学者,我们先学会用编辑原理图的方法来设计一些简单的数字逻辑电路。

原理图设计方法和步骤如下:

(1)新建设计文件

如右图,从File菜单中选择New…命令,或直接

点击常用工具栏的第一个按钮,打开新建设计文件

对话框,如下图。

选择“BlockDiagram/SchematicFile”,点击OK,

即进入原理图编辑界面。

(2)编辑原理图

QuartusII7.2软件的数字逻辑电路原理图的设计是基于常用的数字集成电路的,要熟练掌握原理图设计,必须要认识和熟悉各种逻辑电路的符号、逻辑名称和集成电路型号。

因此努力学好《数字电子技术基础》是后续学习其他专业知识、掌握电路设计的基本条件。

下面我们举例用原理图设计方法设计一个“三输入表决器”电路。

电路的逻辑功能是:

三人表决,以少数服从多数为原则,多数人同意则议案通过,否则议案被否决。

这里,我们使用三个按键代表三个参与表决的人,置“0”表示该人不同意议案,置“1”表示该人同意议案;两个指示灯用来表示表决结果,LED1点亮表示议案通过,LED2点亮表示议案被否决。

真值表如下:

S1

S2

S3

LED1

LED2

0

0

0

0

1

0

0

1

0

1

0

1

0

0

1

0

1

1

1

0

1

0

0

0

1

1

0

1

1

0

1

1

0

1

0

1

1

1

1

0

设计方法和步骤如下:

1)双击原理图的任一空白的处,会弹出一个元件对话框。

在Name栏目中输入and2,我们就得到一个2输入的与门。

2)点击OK按钮,将其放到原理图的适当位置。

重复操作,放入另外两个2输入与门。

也可以通过右键菜单的Copy命令复制得到。

3)双击原理图的空白处,打开元件对话框。

在Name栏目中输入or3,我们将得到一个3输入的或门。

点击OK按钮,将其放入原理图。

4)双击原理图的空白处,打开元件对话框。

在Name栏目中输入not,我们会得到一个非门。

点击OK按钮,将其放入原理图。

5)把所用的元件都放好之后,开始连接电路。

将鼠标指到元件的引脚上,鼠标会变成“十”字形状。

按下左键,拖动鼠标,就会有导线引出。

根据我们要实现的逻辑,连好各元件的引脚。

6)双击原理图的空白处,打开元件对话框。

在Name栏目中输入Input,我们便得到一个输入引脚。

点击OK按钮,放入原理图。

重复操作,给我们的电路加上3个输入引脚。

7)双击输入引脚,会弹出一个属性对话框。

在这一对话框上,我们可更改引脚的名字。

我们分别给3个输入引脚取名in1、in2、in3。

8)双击原理图的空白处,打开元件对话框。

在Name栏目中输入output,我们会得到一个输出引脚。

点击OK按钮,放入原理图。

重复操作,给我们的电路加上两个输出引脚。

给两个输出引脚分别命名为led1、led2。

3.工程编译

设计好的电路若要让软件能认识并检查设计的电路是否有错误,需要进行工程编译,QuartusII7.2软件能自动对我们设计的电路进行编译和检查设计的正确性。

方法如下:

在【Processing】菜单下,点击【StartCompilation】命令,开始编译我们的项目。

编译成功后,点击确定按钮。

4.功能仿真

仿真是指利用QuartusII软件对我们设计的电路的逻辑功能进行验证,看看在电路的各输入端加上一组电平信号后,其输出端是否正确的电平信号输出。

因此在进行仿真之前,我们需要先建立一个输入信号波形文件。

方法和步骤如下:

1)在File菜单下,点击New命令。

在随后弹出的对话框中,切换到OtherFiles页。

选中VectorWaveformFile选项,点击OK按钮。

2)在Edit菜单下,点击InsertNodeorBus…命令。

3)点击NodeFinder…按钮,打开NodeFinder对话框。

点击List按钮,列出电路所有的端子。

点击>>按钮,全部加入。

点击OK按钮,确认。

回到InsertNodeorBus对话框,点击OK按钮,确认。

4)选中in1信号,在Edit菜单下,选择Value=>Clock…命令。

在随后弹出的对话框的Period栏目中设定参数为50ns,点击OK按钮。

5)In2、in3也用同样的方法进行设置,Period参数分别为100ns和200ns。

6)保存文件,在Processing菜单下,选择StartSimulation启动仿真工具。

仿真结束后,点击确认按钮。

观察仿真结果,对比输入与输出之间的逻辑关系是否符合电路的逻辑功能。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- QuartusII7 使用 安装 剖析

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx

人文关怀与和谐医患关系终稿优质PPT.ppt

人文关怀与和谐医患关系终稿优质PPT.ppt