FPGA实现双向IO口与时钟芯片的例子.docx

FPGA实现双向IO口与时钟芯片的例子.docx

- 文档编号:8600150

- 上传时间:2023-02-01

- 格式:DOCX

- 页数:16

- 大小:29.31KB

FPGA实现双向IO口与时钟芯片的例子.docx

《FPGA实现双向IO口与时钟芯片的例子.docx》由会员分享,可在线阅读,更多相关《FPGA实现双向IO口与时钟芯片的例子.docx(16页珍藏版)》请在冰豆网上搜索。

FPGA实现双向IO口与时钟芯片的例子

黑金开发板建模篇的实验十三。

这个例子包含了IO口的使用、状态机以及完成状态标志的巧妙用法,可以多参考一下其写法。

我认为这个例程包含了建模篇大部分的精华和常用方法。

下面将这个例子的全部内容拷贝下来,以备不时之需。

也可以提供给需要的网友来参考。

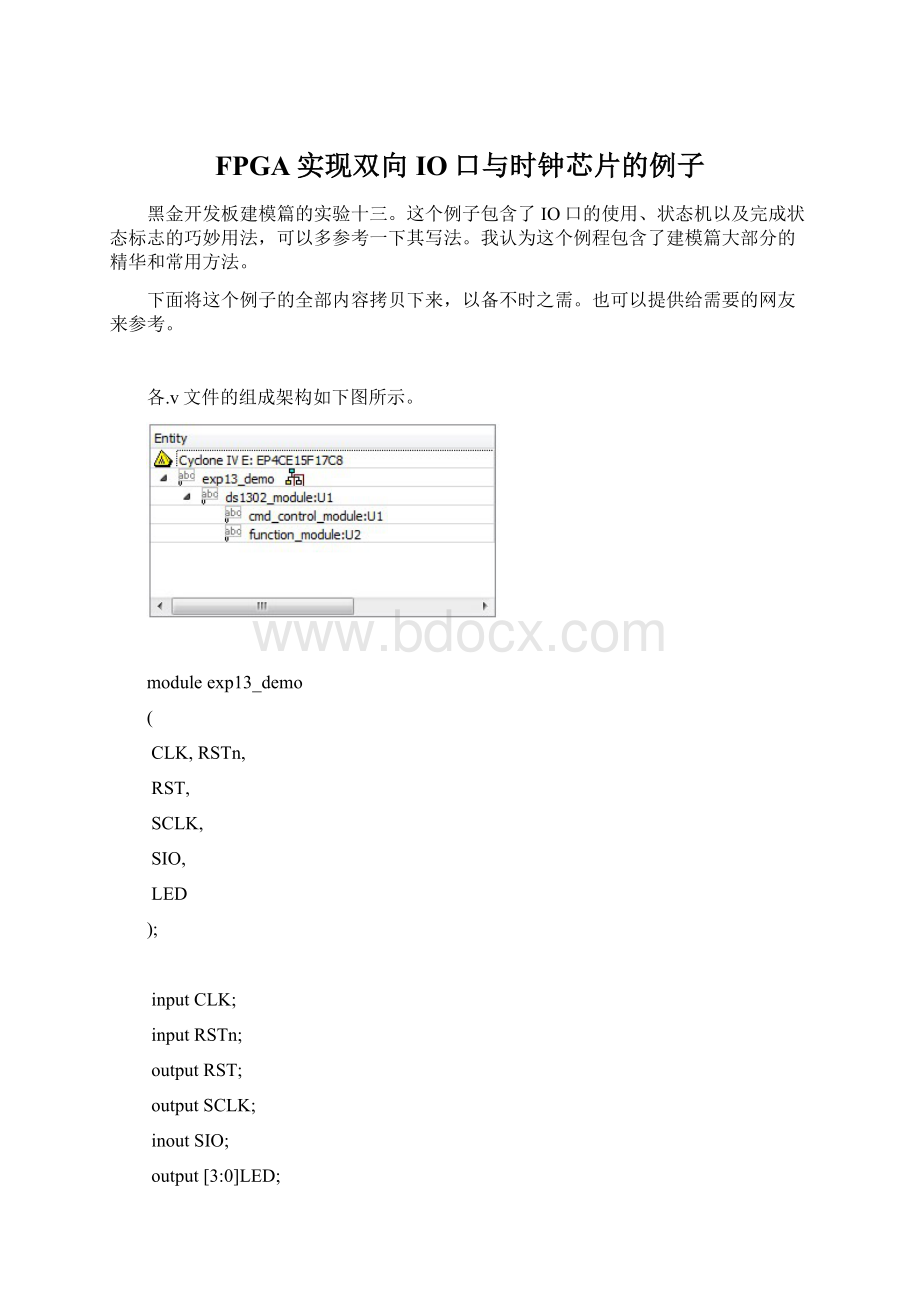

各.v文件的组成架构如下图所示。

moduleexp13_demo

(

CLK,RSTn,

RST,

SCLK,

SIO,

LED

);

inputCLK;

inputRSTn;

outputRST;

outputSCLK;

inoutSIO;

output[3:

0]LED;

reg[3:

0]i;

reg[7:

0]isStart;

reg[7:

0]rData;

reg[3:

0]rLED;

always@(posedgeCLKornegedgeRSTn)

if(!

RSTn)

begin

i<=4'd0;

isStart<=8'd0;

rData<=8'd0;

rLED<=4'd0;

end

else

case(i)

0:

if(Done_Sig)beginisStart<=8'd0;i<=i+1'b1;end

elsebeginisStart<=8'b1000_0000;rData<=8'h00;end

1:

if(Done_Sig)beginisStart<=8'd0;i<=i+1'b1;end

elsebeginisStart<=8'b0100_0000;rData<={4'd1,4'd2};end

2:

if(Done_Sig)beginisStart<=8'd0;i<=i+1'b1;end

elsebeginisStart<=8'b0010_0000;rData<={4'd2,4'd2};end

3:

if(Done_Sig)beginisStart<=8'd0;i<=i+1'b1;end

elsebeginisStart<=8'b0001_0000;rData<={4'd2,4'd2};end

4:

if(Done_Sig)beginrLED<=Time_Read_Data[3:

0];isStart<=8'd0;i<=4'd4;end

elsebeginisStart<=8'b0000_0010;end

endcase

wireDone_Sig;

wire[7:

0]Time_Read_Data;

ds1302_moduleU1

(

.CLK(CLK),

.RSTn(RSTn),

.Start_Sig(isStart),

.Done_Sig(Done_Sig),

.Time_Write_Data(rData),

.Time_Read_Data(Time_Read_Data),

.RST(RST),

.SCLK(SCLK),

.SIO(SIO)

);

assignLED=rLED;

Endmodule

moduleds1302_module

(

CLK,RSTn,

Start_Sig,

Done_Sig,

Time_Write_Data,

Time_Read_Data,

RST,

SCLK,

SIO

);

inputCLK;

inputRSTn;

input[7:

0]Start_Sig;

outputDone_Sig;

input[7:

0]Time_Write_Data;

output[7:

0]Time_Read_Data;

outputRST;

outputSCLK;

inoutSIO;

wire[7:

0]Words_Addr;

wire[7:

0]Write_Data;

wire[1:

0]Access_Start_Sig;

cmd_control_moduleU1

(

.CLK(CLK),

.RSTn(RSTn),

.Start_Sig(Start_Sig),//input-fromtop

.Done_Sig(Done_Sig),//output-totop

.Time_Write_Data(Time_Write_Data),//input-fromtop

.Time_Read_Data(Time_Read_Data),//output-totop

.Access_Done_Sig(Access_Done_Sig),//input-fromU2

.Access_Start_Sig(Access_Start_Sig),//output-toU2

.Read_Data(Read_Data),//input-fromU2

.Words_Addr(Words_Addr),//output-toU2

.Write_Data(Write_Data)//output-toU2

);

wire[7:

0]Read_Data;

wireAccess_Done_Sig;

function_moduleU2

(

.CLK(CLK),

.RSTn(RSTn),

.Start_Sig(Access_Start_Sig),//input-fromU1

.Words_Addr(Words_Addr),//input-fromU1

.Write_Data(Write_Data),//input-fromU1

.Read_Data(Read_Data),//output-toU1

.Done_Sig(Access_Done_Sig),//output-toU1

.RST(RST),//output-totop

.SCLK(SCLK),//output-totop

.SIO(SIO)//output-totop

);

Endmodule

modulecmd_control_module

(

CLK,RSTn,

Start_Sig,

Done_Sig,

Time_Write_Data,

Time_Read_Data,

Access_Done_Sig,

Access_Start_Sig,

Read_Data,

Words_Addr,

Write_Data

);

inputCLK;

inputRSTn;

input[7:

0]Start_Sig;

outputDone_Sig;

input[7:

0]Time_Write_Data;

output[7:

0]Time_Read_Data;

inputAccess_Done_Sig;

output[1:

0]Access_Start_Sig;

input[7:

0]Read_Data;

output[7:

0]Words_Addr;

output[7:

0]Write_Data;

reg[7:

0]rAddr;

reg[7:

0]rData;

always@(posedgeCLKornegedgeRSTn)

if(!

RSTn)

begin

rAddr<=8'd0;

rData<=8'd0;

end

else

case(Start_Sig[7:

0])

8'b1000_0000:

//Writeunprotect

beginrAddr<={2'b10,5'd7,1'b0};rData<=8'h00;end

8'b0100_0000:

//Writehour

beginrAddr<={2'b10,5'd2,1'b0};rData<=Time_Write_Data;end

8'b0010_0000:

//Writeminit

beginrAddr<={2'b10,5'd1,1'b0};rData<=Time_Write_Data;end

8'b0001_0000:

//Writesecond

beginrAddr<={2'b10,5'd0,1'b0};rData<=Time_Write_Data;end

8'b0000_1000:

//Writeprotect

beginrAddr<={2'b10,5'd7,1'b0};rData<=8'b1000_0000;end

8'b0000_0100:

//Readhour

beginrAddr<={2'b10,5'd2,1'b1};end

8'b0000_0010:

//Readminit

beginrAddr<={2'b10,5'd1,1'b1};end

8'b0000_0001:

//Readsecond

beginrAddr<={2'b10,5'd0,1'b1};end

endcase

reg[1:

0]i;

reg[7:

0]rRead;

reg[1:

0]isStart;

regisDone;

always@(posedgeCLKornegedgeRSTn)

if(!

RSTn)

begin

i<=2'd0;

rRead<=8'd0;

isStart<=2'b00;

isDone<=1'b0;

end

elseif(Start_Sig[7:

3])//Writeaction

case(i)

0:

if(Access_Done_Sig)beginisStart<=2'b00;i<=i+1'b1;end

elsebeginisStart<=2'b10;end

1:

beginisDone<=1'b1;i<=i+1'b1;end

2:

beginisDone<=1'b0;i<=2'd0;end

endcase

elseif(Start_Sig[2:

0])//Readaction

case(i)

0:

if(Access_Done_Sig)beginrRead<=Read_Data;isStart<=2'b00;i<=i+1'b1;end

elsebeginisStart<=2'b01;end

1:

beginisDone<=1'b1;i<=i+1'b1;end

2:

beginisDone<=1'b0;i<=2'd0;end

endcase

assignDone_Sig=isDone;

assignTime_Read_Data=rRead;

assignAccess_Start_Sig=isStart;

assignWords_Addr=rAddr;

assignWrite_Data=rData;

Endmodule

modulefunction_module

(

CLK,RSTn,

Start_Sig,

Words_Addr,

Write_Data,

Read_Data,

Done_Sig,

RST,

SCLK,

SIO

);

inputCLK;

inputRSTn;

input[1:

0]Start_Sig;

input[7:

0]Words_Addr;

input[7:

0]Write_Data;

output[7:

0]Read_Data;

outputDone_Sig;

outputRST;

outputSCLK;

inoutSIO;

parameterT0P5US=5'd24;//50M*(0.5e-6)-1=24

reg[4:

0]Count1;

always@(posedgeCLKornegedgeRSTn)

if(!

RSTn)

Count1<=5'd0;

elseif(Count1==T0P5US)

Count1<=5'd0;

elseif(Start_Sig[0]==1'b1||Start_Sig[1]==1'b1)

Count1<=Count1+1'b1;

else

Count1<=5'd0;

reg[5:

0]i;

reg[7:

0]rData;

regrSCLK;

regrRST;

regrSIO;

regisOut;

regisDone;

always@(posedgeCLKornegedgeRSTn)

if(!

RSTn)

begin

i<=6'd0;

rData<=8'd0;

rSCLK<=1'b0;

rRST<=1'b0;

rSIO<=1'b0;

isOut<=1'b0;

isDone<=1'b0;

end

elseif(Start_Sig[1])

case(i)

0:

beginrSCLK<=1'b0;rData<=Words_Addr;rRST<=1'b1;isOut<=1'b1;i<=i+1'b1;end

1,3,5,7,9,11,13,15:

if(Count1==T0P5US)i<=i+1'b1;

elsebeginrSIO<=rData[(i>>1)];rSCLK<=1'b0;end

2,4,6,8,10,12,14,16:

if(Count1==T0P5US)i<=i+1'b1;

elsebeginrSCLK<=1'b1;end

17:

beginrData<=Write_Data;i<=i+1'b1;end

18,20,22,24,26,28,30,32:

if(Count1==T0P5US)i<=i+1'b1;

elsebeginrSIO<=rData[(i>>1)-9];rSCLK<=1'b0;end

19,21,23,25,27,29,31,33:

if(Count1==T0P5US)i<=i+1'b1;

elsebeginrSCLK<=1'b1;end

34:

beginrRST<=1'b0;i<=i+1'b1;end

35:

beginisDone<=1'b1;i<=i+1'b1;end

36:

beginisDone<=1'b0;i<=6'd0;end

endcase

elseif(Start_Sig[0])

case(i)

0:

beginrSCLK<=1'b0;rData<=Words_Addr;rRST<=1'b1;isOut<=1'b1;i<=i+1'b1;end

1,3,5,7,9,11,13,15:

if(Count1==T0P5US)i<=i+1'b1;

elsebeginrSIO<=rData[(i>>1)];rSCLK<=1'b0;end

2,4,6,8,10,12,14,16:

if(Count1==T0P5US)i<=i+1'b1;

elsebeginrSCLK<=1'b1;end

17:

beginisOut<=1'b0;i<=i+1'b1;end

18,20,22,24,26,28,30,32:

if(Count1==T0P5US)i<=i+1'b1;

elsebeginrSCLK<=1'b1;end

19,21,23,25,27,29,31,33:

if(Count1==T0P5US)begini<=i+1'b1;end

elsebeginrSCLK<=1'b0;rData[(i>>1)-9]<=SIO;end

34:

beginrRST<=1'b0;isOut<=1'b1;i<=i+1'b1;end

35:

beginisDone<=1'b1;i<=i+1'b1;end

36:

beginisDone<=1'b0;i<=6'd0;end

endcase

assignRead_Data=rData;

assignDone_Sig=isDone;

assignRST=rRST;

assignSCLK=rSCLK;

assignSIO=isOut?

rSIO:

1'bz;

endmodule

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 实现 双向 IO 时钟 芯片 例子

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx