基于FPGA的模糊控制器的设计.docx

基于FPGA的模糊控制器的设计.docx

- 文档编号:8564653

- 上传时间:2023-01-31

- 格式:DOCX

- 页数:16

- 大小:173.71KB

基于FPGA的模糊控制器的设计.docx

《基于FPGA的模糊控制器的设计.docx》由会员分享,可在线阅读,更多相关《基于FPGA的模糊控制器的设计.docx(16页珍藏版)》请在冰豆网上搜索。

基于FPGA的模糊控制器的设计

现场可编程门阵列FPGA是近年来发展迅速的大规模可编程逻辑器件,它具有设计周期短,片内资源丰富,可无限次加载和现场可编程等特点。

在FPGA上实现模糊控制器是一种介于专用集成电路(ASIC)和通用处理器之间的方案,具有电子产品的高速度、高可靠性、小型化、集成化、低功耗、保密性能好、具有自主知识产权、产品上市快等优势。

模糊控制器不需要控制对象的精确数学模型,是一种基于规则的控制,依据操作人员的控制经验和专家的知识,通过查表得到控制量。

因此,模糊控制器具有响应快,超调量小,鲁棒性强等特点。

它能够克服系统中模型参数变化和非线性等不确定因素,在大滞后、非线性系统中得到广泛应用。

随着EDA技术的发展,FPGA在数字逻辑系统中发挥越来越重要的作用,采用硬件描述语言的硬件电路设计方法得到了广泛应用。

本文利用VHDL硬件描述语言在FPGA芯片上设计一种简化的模糊控制器。

一模糊控制器的结构及其FPGA实现流程

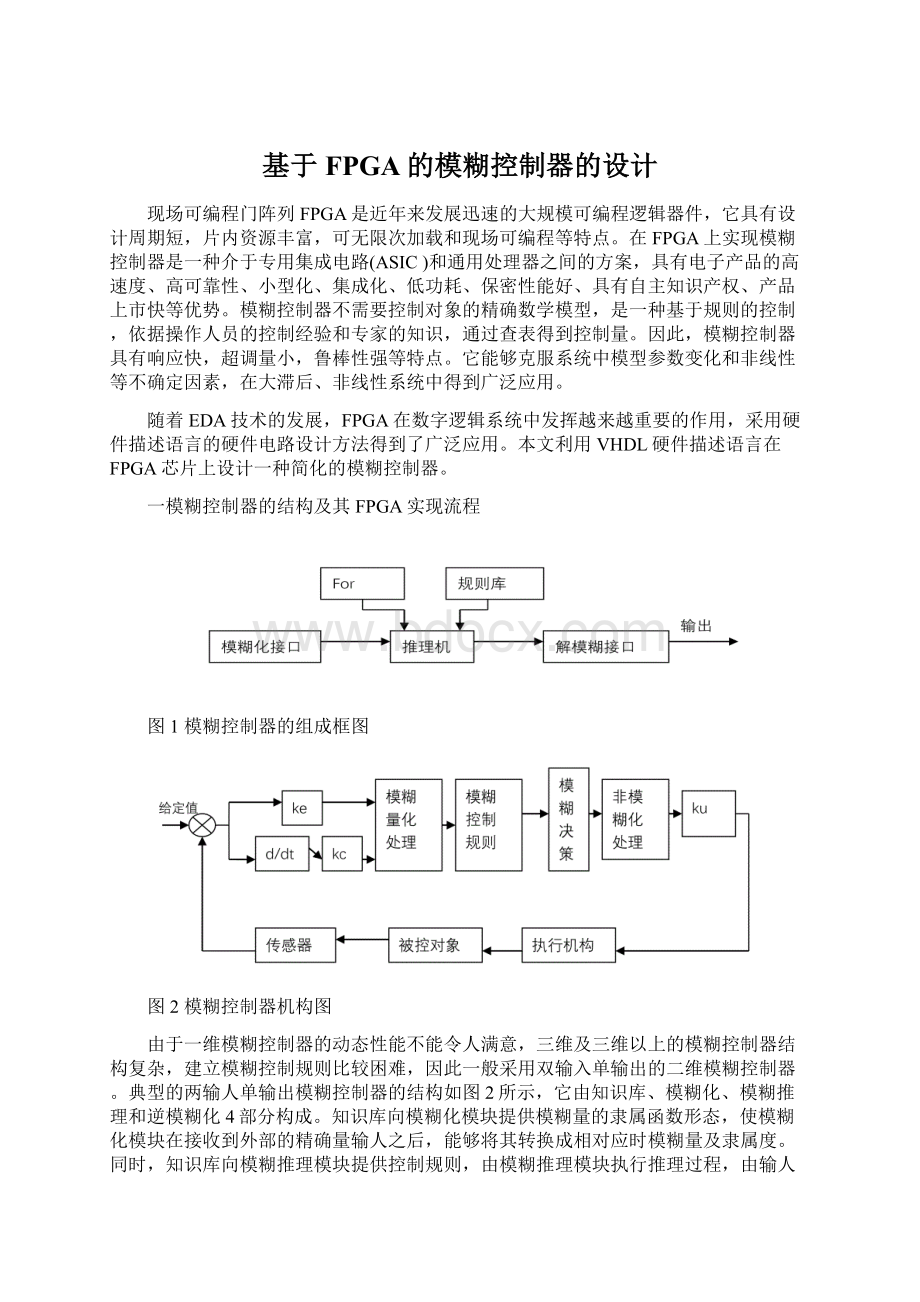

图1模糊控制器的组成框图

图2模糊控制器机构图

由于一维模糊控制器的动态性能不能令人满意,三维及三维以上的模糊控制器结构复杂,建立模糊控制规则比较困难,因此一般采用双输入单输出的二维模糊控制器。

典型的两输人单输出模糊控制器的结构如图2所示,它由知识库、模糊化、模糊推理和逆模糊化4部分构成。

知识库向模糊化模块提供模糊量的隶属函数形态,使模糊化模块在接收到外部的精确量输人之后,能够将其转换成相对应时模糊量及隶属度。

同时,知识库向模糊推理模块提供控制规则,由模糊推理模块执行推理过程,由输人的模糊量推出输出的模糊量。

知识库也向反模糊化模块提供模糊量的隶属函数形态,反模糊化接口则将输出的模糊量及隶属度转换成与之对应的精确量。

论域和模糊状态应根据问题的实际情况而定,现在假设e,ec和u的模糊子集均为{NB,NM,NS,ZO,PS,PM,PB},模糊论域均为[-4,-3,-2,-1,0,1,2,3,4],设e的基本论域为[-2,2],ec的基本论域为[-1,1],u的基本论域为[-5,5]。

则ke=2,kc=4,ku=1。

25。

模糊控制器的FPGA设计流程如图3所示

模糊控制器功能定义

模糊控制器算法设计

确定总体结构

划分功能模块

对个功能模块

进行vhdl语言描述

综合,仿真

Fpga配置下载

硬件测试

图3模糊控制器的fpga实现流程图

㈡模糊化模块

1.隶属函数的选取

模糊化过程需要用到隶属函数,隶属函数是模糊控制中的关键问题。

隶属函数大多依赖经验或处理方便而选取。

选取时至少要遵循3条原则:

表示隶属函数的模糊集合必须是凸模糊集合;变量所取隶属函数是对称和平衡的;隶属函数要遵从语意顺序和避免不恰当的重叠。

因此,此文确定的E和C的隶属函数形状如图4所示

图4E和EC的隶属函数形状

2.隶属函数的存储

将上述隶属函数存在2个RAM表中,则在模糊化处理时可进行并行处理,处理方便,且速度提高一倍。

表示方法如图4所示。

图5隶属函数的存储方式

在图4中,三角形是等腰三角形,梯形的下底是上底的2倍。

可见由底边宽度和底边中点就可以确定隶属函数的所有信息。

分别用一个字节表示每个语言变量的底边宽度(实际宽度的一半),用3个位(bit)表示底边中点位置。

这样,全部信息只需要8个字节,以及8个3位就可以表示了:

底边宽度表示为:

width0,widthl,……………,width7

底边中点表示为:

center0,centerl,……………,center7

这部分信息存于一个奇数表和一个偶数表中,分别表示标号为奇数和偶数的底边宽度和底边中点信息。

3.隶属度的计算

模糊化模块的功能主要包括2部分:

把输人的精确量进行尺度变换,变换到相应的论域范围;将己变换到论域范围的输入量进行模糊化处理,主要是计算各个输人量的隶属度。

为了简化处理,将输人值进行均匀量化。

由于A/D转换器采样后输人的值为8位,其范围是0一255,均匀量化后各个论域表示见表1。

这样模糊化模块的主要工作就是计算输人值的隶属度,如图5所示。

表1论域f化和表示方法

图6隶属度图

据图6,输人变量为1时,其隶属度

为

为实现上述计算,需要用到一个加法器,一个减法器和一个除法器。

由隶属度的性质可知,计算的结果肯定是小数。

为了实现方便,可将分子的计算结果左移8位,使分子变成16位,而分母是8位,因此,计算结果是8位。

加法器和减法器的实现比较容易,重点放在16位除以8位的除法器的实现上。

除法器采用普通的除法运算,并配合移位一减法方式来实现,可节省硬件制作成本。

除法运算的算法流程如图7所示,图中:

a为被除数;b为除数;q为商;r为余数;s为控制除法运算开始执行的控制信号;done表示运算完成;c为减法计数器的计数值。

图7除法运算的算法流程图

据上述算法编写VHDL程序,可实现除法器运算。

除法器是模糊化模块的关键部件,完成了除法器的设计,也就基本上完成了模糊化模块的数据处理

㈢模糊推理模块

模糊控制器的核心是模糊推理,模糊推理的基础是模糊控制规则。

模糊控制规则是用语言表示的模糊条件语句,存放在模糊控制器的知识库中,可以通过接口由控制专家输人或修改。

两输人单输出的模糊控制规则形式为

模糊推理常采用Mamdani推理,也称为Max-Min推理。

设两输人单输出模糊控制器的输人量是xISa’ANDyISb’,则根据模糊控制规则进行推理,可以得出输出模糊控制量:

(用模糊集合C’表示):

式中包括了3种主要的模糊逻辑运算:

and运算,通常采用求交(取小)的方法;蕴含运算“→”采用求交法;合成运算“。

”,采用Max-Min方法。

假设有如下2条模糊控制规则

则Mamdani推理的机理如图7所示。

图中,C1,C2:

通过最小化运算求出,最右边的模糊量图形C通过最大化运算求出,C就是最终的推理结果。

可见,模糊推理主要包括最小化运算模块和最大化运算模块。

图8Maindani推理的机理

此处知识库中的模糊控制规则,每一条可用一个字节来存储,具体存储格式为:

000000XX

000001XX

000010XX

000011XX

…

111100XX

111111XX

这样就可以把输人的语言值作为规则表的地址进行查找。

由隶属函数的特点可知,对于每个输人变量,最多可以并行输出2个语言值和2个隶属度。

对于两输人系统,最多输出4个语言值和4个隶属度。

这样,对于一个两输人系统,最多激活4条模糊规则,即

这样,最终模糊量C的推理过程与只有2条规则时完全类似,只需要最小化运算和最大化运算。

实现最小化运算的关键是设计出一个最小比较器。

由于每个前件最多激活2条模糊规则,所以设μx1和μx2是第1个前件的隶属度,μy1和μy2是第2个前件的隶属度,,μc1和μc2分别是对应于4条模糊控制规则的输出量的隶属度。

比较器的行为可以描述如下

最小化运算的结果,μc1和μc4再输人到最大化模块中,用于完成模糊规则合并的过程。

最大化模块与最小化模块的实现方法类似。

㈣逆模糊化模块

反模糊化通常采用加权平均法,对于论域为离散的情况有

由于隶属函数采用8位二进制表示,而所涉及的模糊规则最多为4条,所以分子运算需要4个8位x2位的乘法器,3个10位加法器,分母需要3个8位加法器。

此外,还需要一个12位/10位的除法器。

除法器的设计方法与模糊化模块中的设计方法相同。

而乘法器的设计方法有多种,可以利用工具软件自带的参数可设置兆功能块LPM一multiplier进行定制。

由上所述,反模糊化模块需要乘法器和除法器,因此它是最浪费芯片资源,也是最耗时的一个模块。

㈤设计模糊控制器

根据模糊控制器的特点及上述描述原理,采用模块化设计方法,本文将模糊控制模块分为四块分别进行设计,如图9所示。

clk为全局时钟,g和f为输入给定和反馈,u为输出控制量,设g,f,和u的位数为八位。

模糊控制模块内部架构分为四个模糊:

减法器模块,离散化模块,建表模块和处理模块。

用VHDL硬件描述语言在altera公司的quartusii50进行描述,形成四个模块并进行综合,见图9所示。

图9模糊控制器

各个模块的作用分别如下描述:

减法器模块(jianfaqi)主要是利用给定值g和反馈值f计算误差e和误差变化率ec。

进行减法运算时,总是数值大的减去数值小的,正负号分别由eo和co标识,不需要考虑溢出和借位等问题。

离散化模块(lisanhua)的作用时把减法器模块得到的误差e和误差变化率ec在各自的论域范围内进行离散处理。

离散时把量化因子ke和kc乘入。

建表模块(jianbiao)的作用是把控制总表用vhdl语言的形式描述,此控制表是模糊控制表乘上比例因子ku后的实际值。

由于控制表中的数是当前控制变化量,还不能直接作用于被控对象,处理模块的作用是根据当前控制变化量,在前一次控制量的基础上进行运算得到此次控制量。

同时规定控制量的上下限,上限根据具体情况而定,下限是零。

㈥仿真

仿真波形如下图,从仿真图可以看出,在给定值g不变的情况下,控制量u随着反馈值f的变化而变化,变化规律与理论上的模糊控制系统的输出规律基本一致.

图10仿真波形图

㈦结束语

本文采用VHDL硬件描述语言在altera公司的quartusii50实现了模糊控制器,并且进行了仿真,仿真发现该模糊控制器基本符合模糊控制器的性能要求。

㈧附表:

模糊控制器各个模块vhdl语言描述:

减法器模块的vhdl语言的程序如下:

LIBRARYIEEE;

uSEIEEE。

STD_LOGIC_1164。

ALL;

uSEIEEE。

STD_LOGIC_ARITH。

ALL;

eNTITYmhuIS

pORT(g:

INSTD_LOGIC_VECTOR(7DOWNTO0);

f:

INSTD_LOGIC_VECTOR(7DOWNTO0);

clk:

INSTD_LOGIC;

e:

OUTSTD_LOGIC_VECTOR(7DOWNTO0);

ec:

OUTSTD_LOGIC_VECTOR(7DOWNTO0);

eo:

OUTSTD_LOGIC;

co:

OUTSTD_LOGIC

);

eNDmhu;

aRCHITECTURErtlOFmhuIS

SIGNALa,b:

STD_LOGIC_VECTOR(7DOWNTO0);

signalm,n:

STD_LOGIC;

begin

process(clk)

begin

ifclk'eventandclk='1'then

iff>=gthen

a<=f-g;

m<='1';

elsiff then a<=g-f; m<='0'; endif; b<=a; n<=m; endif; endprocess; process(clk) begin ifclk'eventandclk='1'then ifm='0'andn='0'then ifa>=bthen ec<=b-a; co<='0'; elsifa ec<=b-a; co<='1'; elsifm='0'andn='1'then ec<=a+b; co<='0'; elsifm='1'andn='0'then ec<=a+b; co<='1'; elsifm='1'andn='1'then ifa>=bthen ec<=a+b; co<='1'; elsifa ec<=b-a; co<='0'; endif; endif; endprocess; endrtl; 离散化模块的vhdl语言的程序如下: LIBRARYIEEE; USEIEEE。 STD_LOGIC_1164。 ALL; USEIEEE。 STD_LOGIC_ARITH。 ALL; ENTITYlisanhuaIS PORT(e: INSTD_LOGIC_VECTOR(7DOWNTO0); ec: INSTD_LOGIC_VECTOR(7DOWNTO0); eo: INSTD_LOGIC; co: INSTD_LOGIC; clk: INSTD_LOGIC; elunyu: OUTSTD_LOGIC_VECTOR(3DOWNTO0); eclunyu: OUTSTD_LOGIC_VECTOR(3DOWNTO0)); ENDlisanhua; ARCHITECTUREcOFlisanhuaisSIGNALb: STD_LOGIC_VECTOR(7DOWNTO0); begin process(clk) begin ifclk'eventandclk='1'then ifeo='0'then ife<="0000001"then elunyu<="0000"; elsif"00000001" elunyu<="0001"; elsif"00000011" elunyu<="0010"; elsif"00000101" elunyu<="0011"; elsif"00000111" elunyu<="0100"; elsifeo='1'then ife<="00000001"then elunyu<="0000"; elsif"00000001" elunyu<="1001"; elsif"00000011" elunyu<="1010"; elsif"00000101" elunyu<="1011"; elsif"00000111" elunyu<="1100"; endif; endif; endprocess; process(clk)begin ifclk'eventandclk='1'then ifco='0'then ifec<="0000001"then eclunyu<="0000"; elseif"00000001" eclunyu<="0001"; elseif"00000011" eclunyu<="0010"; elseif"00000101" eclunyu<="0011"; elseif"00000111" eclunyu<="0100"; ife<="00000001"then eclunyu<="0000"; elseif"00000001" eclunyu<="1001"; elseif"00000011"andec<="00000111"then eclunyu<="1010"; elseif"00000101" eclunyu<="1011"; elseif"00000111" eclunyu<="1100"; endif; endif; endprocess; endc; 建表模块的vhdl语言的程序如下: LIBRARYIEEE; USEIEEE。 STD_LOGIC_1164。 ALL; USEIEEE。 STD_LOGIC_ARITH。 ALL; ENTITYjianbiaoIS PORT(elunyu: INSTD_LOGIC_VECTOR(7DOWNTO0); eclunyu: INSTD_LOGIC_VECTOR(7DOWNTO0); result: OUTSTD_LOGIC_VECTOR(7DOWNTO0); co: OUTSTD_LOGIC); ENDjianbiao; ARCHITECTUREaOFjianbiaoisSIGNALtmp: STD_LOGIC_VECTOR(7DOWNTO0); begin process(elunyu) variabletmp: std_logic_vector(7downto0); begin tmp: =elunyu&eclunyu; casetmpis when""=> result<="00000101"; co<='1'; when""=> result<="00000010"; co<='1'; whenothers=> result<="00000000"; co<='0'; endcase; endprocess; enda; 处理模块的vhdl语言的程序如下: LIBRARYIEEE; USEIEEE。 STD_LOGIC_1164。 ALL; USEIEEE。 STD_LOGIC_ARITH。 ALL; ENTITYchuliIS PORT(a: INSTD_LOGIC_VECTOR(7DOWNTO0); ci: INSTD_LOGIC; clk: INSTD_LOGIC; u: OUTSTD_LOGIC_VECTOR(7DOWNTO0)); ENDchuli; ARCHITECTUREbOFchuliisSIGNALb: STD_LOGIC_VECTOR(7DOWNTO0); begin process(clk) begin ifclk'eventandclk='1'then ifci='0'then ifb>="01010000"then b<="01010000"; elseifb<="01010000"then b<=a; endif; endif; elseifci='1' then ifb>=aandb<="01010000"then b<=a; elseifb>"01010000"then b<="00000000"; endif; endif; ifb>="01001101"then u<="01010000"; else u<=b; endif; endprocess; endb; 大规模专用集成电路实验报告 设计题目基于FPGA的模糊控制器的设计 学院机电工程学院 专业控制工程与控制理论 姓名牛年增 班级研0406班 学号09 仅供个人用于学习、研究;不得用于商业用途。 Forpersonaluseonlyinstudyandresearch;notforcommercialuse. NurfürdenpersönlichenfürStudien,Forschung,zukommerziellenZweckenverwendetwerden. Pourl'étudeetlarechercheuniquementàdesfinspersonnelles;pasàdesfinscommerciales. толькодлялюдей,которыеиспользуютсядляобучения,исследованийинедолжныиспользоватьсявкоммерческихцелях. 以下无正文

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 基于 FPGA 模糊 控制器 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx