QuartusII四位全加器.docx

QuartusII四位全加器.docx

- 文档编号:8133807

- 上传时间:2023-01-29

- 格式:DOCX

- 页数:14

- 大小:1.94MB

QuartusII四位全加器.docx

《QuartusII四位全加器.docx》由会员分享,可在线阅读,更多相关《QuartusII四位全加器.docx(14页珍藏版)》请在冰豆网上搜索。

QuartusII四位全加器

1.系统电路架构

2.练习使用试验箱

3.VHDL语言入门

EDA软件开发平台161

——QuartusII

1.设计一个四位的全加器falladder

考虑到低位过来的进位(半加器halfadder不需要考虑低位的进位)

半加器:

S=A⊕BC=AB

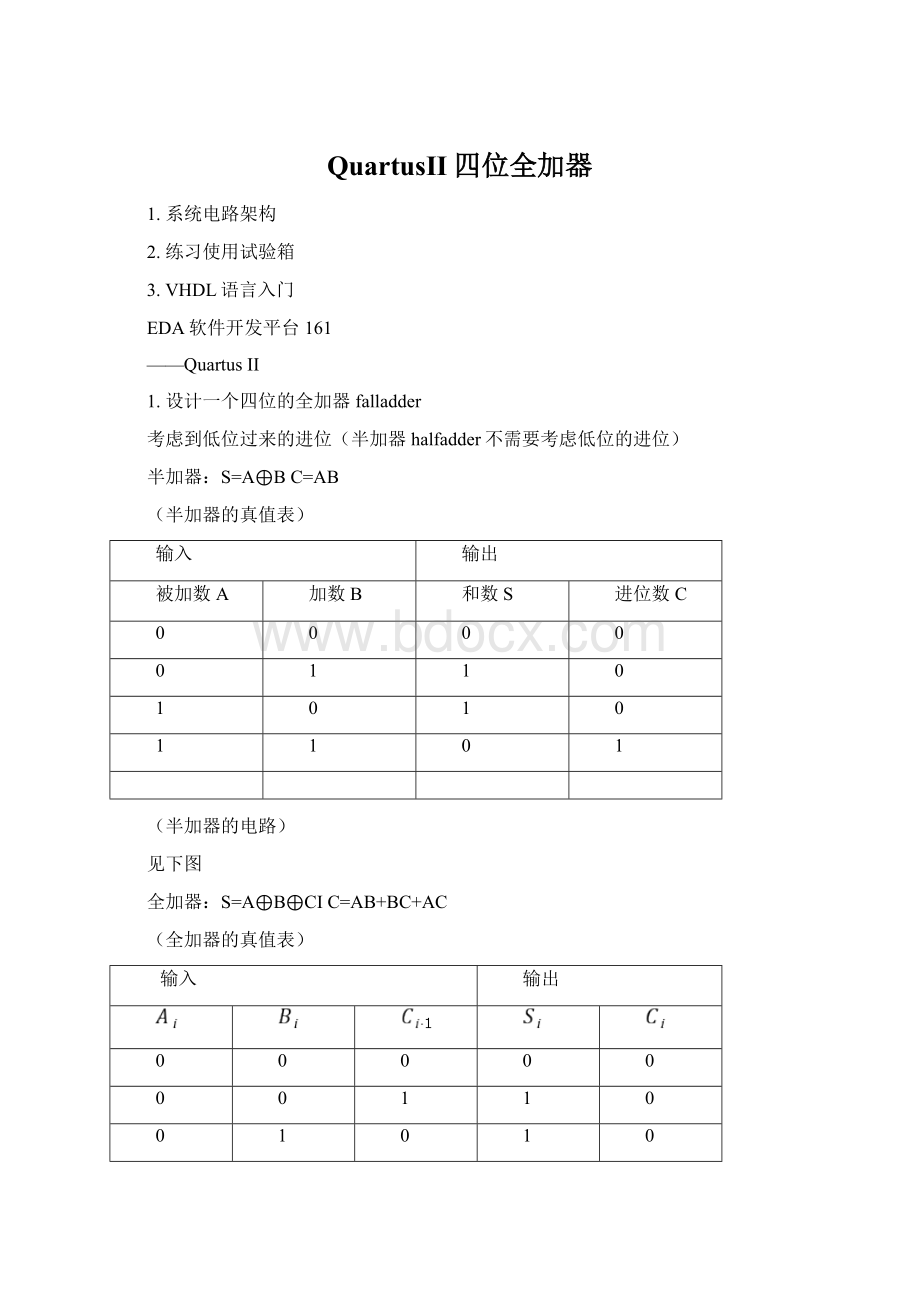

(半加器的真值表)

输入

输出

被加数A

加数B

和数S

进位数C

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

(半加器的电路)

见下图

全加器:

S=A⊕B⊕CIC=AB+BC+AC

(全加器的真值表)

输入

输出

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

(全加器的电路)

见下图

注意工程文件名不能以数字开头且不能以下划线结尾

将底层文件生成为顶层文件

将半加器创造为符号图元

由此可以添加所设置的符合元作为库文件

添置原件(半加器作为独立元件在DeviceDesignFiles里添加)

此时半加器可以作为独立的原件作为下一层的电路设计的独立元。

将一位全加器设置为单元,为下面的四位全加器做准备

调用四个一位全加器,作为四位全加器的原件来设计四位全加器

完成四位全加器的制作

也可将输入输出端口改为总线形式:

输入端口a[3..0]、b[3..0]相对应的节点分别为a0a1a2a3;

输出端口sum[3..0]sum0sum1sum2sum3;

连接好电路图,现在开始进行仿真

首先将四位全加器置顶

进行仿真

总结:

Project:

add4bit.qpf

半加器halfadder.bdf→全加器fallfadder.bdf→四位全加器add4bit.bdf→完成设计

在编译的过程中要将其设置为顶层文件

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- QuartusII 全加器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx