数字电子.docx

数字电子.docx

- 文档编号:7976231

- 上传时间:2023-01-27

- 格式:DOCX

- 页数:65

- 大小:1.29MB

数字电子.docx

《数字电子.docx》由会员分享,可在线阅读,更多相关《数字电子.docx(65页珍藏版)》请在冰豆网上搜索。

数字电子数字电子单选题0000020005、两个开关控制一盏灯,只有两个开关都闭合时灯才不亮,则该电路的逻辑关系是。

(a)与非(b)或非(c)同或(d)异或答案:

a(难)0000020006、已知F,选出下列可以肯定使F=0的取值。

(a)ABC=011(b)BC=11(c)CD=10(d)BCD=111答案:

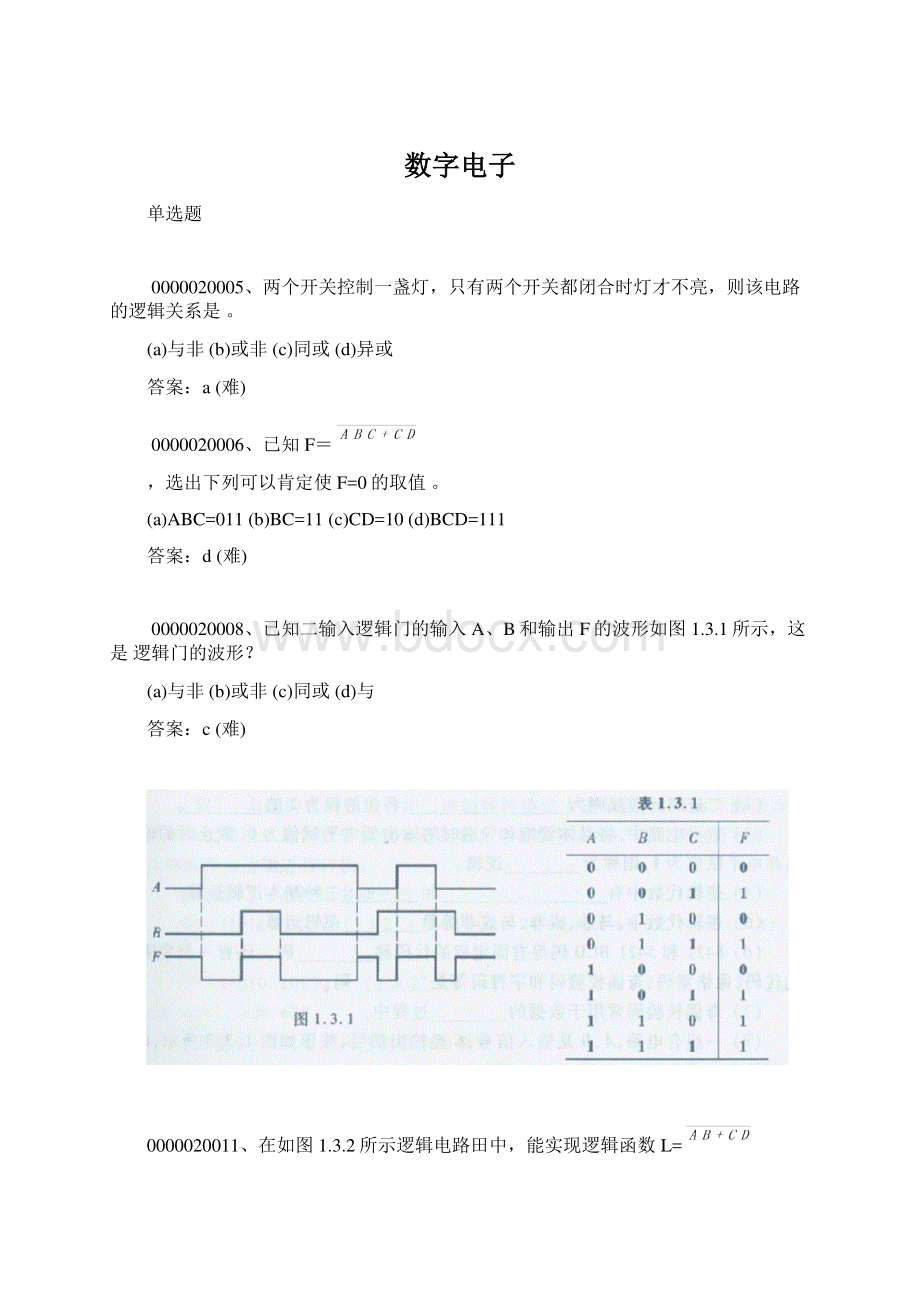

d(难)0000020008、已知二输入逻辑门的输入A、B和输出F的波形如图1.3.1所示,这是逻辑门的波形?

(a)与非(b)或非(c)同或(d)与答案:

c(难)0000020011、在如图1.3.2所示逻辑电路田中,能实现逻辑函数L=的是。

答案:

c(难)0000010024、TTL与非门输出低电平的参数规范值是。

(a)UOL0.3V(b)UOL0.3V(c)UOL0.4V(d)UOL0.8V答案:

c(难)0000010030、某集成电路封装内集成有4个与非门,它们输出全为高电平时,测得5V电源端的电流为8mA,输出全为0时,测得5v电源端的电流为16mA,该TTL与非门的功耗为mW。

(a)30(b)20(c)15(d)10答案:

c(难)0000010034、门电路输人端对地所接电阻RROF时相当于此端。

(a)接逻辑“1”b接逻辑“0”(c)接2.4V电压(d)逻辑不定答案:

b(难)0000010035、门电路输人端对地所接电阻RRON时相当于此端。

(a)接逻辑“1”b接逻辑“0”(c)接2.4V电压(d)逻辑不定答案:

a(难)0000010036、数字系统中,降低尖峰电流影响,所采取的措施是。

(a)接入关门电阻(b)接入开门电阻(c)接入滤波电容(d)降低供电电压答案:

c(难)0000030046、利用2个74LSl38和1个非门,可以扩展得到1个线译码器。

(a)24(b)38(c)416(d)无法确定。

答案:

c(难)0000030047、用原码输出的译码器实现多辅出逻辑函数,需要增加若于个。

(a)非门(b)与非门(c)或门(d)或非门答案:

c(难)0000030048、七段译码器74LS47的输入是4位,输出是七段反码。

(x)二进制码(b)七段码(c)七段反码(d)BCD码答案:

d(难)0000030049、多路数据选择器MUX的输入信号可以是。

(a)数字信号(b)模拟信号(c)数模混合信号(d)数字和模拟信号答案:

a(难)0000040056、如果把D触发器的输出Q反馈连接到输入D,则输出Q的脉冲波形的频率为CP脉冲频率f的,(a)二倍频(b)不变(c)四分频(d)二分频答案:

d(难)0000040057、某触发器的2个输入X1、X2和输出Q的波形如图5.3.1所示,试判断它是触发器。

(a)基本RS(b)JK(c)RS(d)D答案:

b(难)0000060078、在环形振荡器中,为了降低振荡频率,通常在环形通道中串入。

(a)更多非门(b)电感L(c)RC环节(d)大容量电容答案:

c(难)0000060084、改变值,不会改变555构成的多谐振荡器电路的振荡频率。

(a)电源VCCb电阻R1(c)电阻R2(d)电容C答案:

a(难)0000060085、555构成的多谐振荡器中,还可通过改变端电压值使振荡周期改变。

(a)VCC(b)RD(c)CU(d)GND答案:

c(难)0000060086、在端加可变电压,可使555多谐振蔼器输出调频波。

(a)OUT(b)RD(c)CU(d)GND答案:

c(难)0000060087、555构成的多谐振荡器电路中、当R1=R2时,欲使输出占空比约为50,最简单的办法是。

(a)电容C减半(b)R2两端并接二极管(c)CU端接地(d)VCC减半答案:

b(难)0000050092、欲把36kHz的脉冲信号变为1Hz的脉冲信号,若采用十进制集成计数器,则各级的分频系数为。

(a)(3,6,10,10,10)(b)(4,9,10,10,10)(c)(3,12,10,10,10)(d)(6,3,10,10,10)答案:

b(难)0000050093、用集成计数器设计n进制计数器时,不宜采用方法。

(a)置最小数(b)反馈复位(c)反馈预置(d)时钟禁止答案:

d(难)0000050097、两模数分别为M1和M2的计数器串接而构成的计数器,其总模数为。

(a)M1M2(b)M1M2(c)M1M2(d)M1M2答案:

b(难)0000080102、在系统可编是指:

对位于的可编程逻辑器件进行编程。

(a)用户电路板(b)特制的电路板(c)编程器(d)专用编程器答案:

a(难)0000080104、HDPLD比较适合用在以的数字系统。

(a)复杂(b)控制为主(c)时序为主(d)较简单答案:

b(难)0000080105、FPGA比较适合用在以的数字系统。

(a)复杂(b)控制为主(c)时序为主(d)较简单答案:

c(难)0000080106、高密度可编程逻辑器件中具有硬件加密功能的器件是。

(a)HDPLD和FPGA(b)GAL(c)HDPLD(d)FPGA答案:

c(难)0000080107、要对用户电路板上的3片在系统可编程芯片编程,你认为最好的方法是。

(a)在专用编程器上逐片编程(b)在专用编程器L同时编程(c)通过编程线对板上的HDPLD逐片编程(d)通过编程线对板上的所有HDPLD次编程答案:

d(难)0000070110、n位DAC最大的输出电压uOmax为UA。

(a)(2n1)(b)2n(c)2n+1(d)(2n+1)答案:

a(难)0000070114、集成DA转换器不可以用来构成。

(d)加法器(b)程控放大器(c)数模转换(d)波形发生电路答案:

a(难)0000070115、如要将一个最大幅度为5.1V的模拟信号转换为数字信号,要求输入每变化20mV,输出信号的最低位(LSB)发生变化,应选用位ADC(a)6(b)8(c)10(d)12答案:

b(难)0000020126、函数F(A,B,C,D)m(1,3,5,7,8,9,10,11,14,15)的最简与非实现是。

(a)(b)(c)(d)答案:

b(难)0000020127、函数的或与式是。

(a)(b)(c)(d)答案:

b(难)0000020128、函数的简化与或表达式是。

(a)(b)(c)(d)答案:

a(难)0000020131、能使逻辑函数为0的变量(顺序为ABC)组合是。

(a)011,110,101(b)010,001,100(c)110,101,011(d)110,101,111答案:

b(难)0000020135、在下列表达式中,只能用或非逻辑实现的是。

(a)(b)(c)(d)答案:

c(难)0000020136、能使逻辑函数均为1的输入变量的组合是。

(a)1101,0001,0100,1000(b)1100,1110,1010,1011(c)1110,0110,0111,1111(d)1111,1001,1010,0000答案:

a(5)0000010145、如右图所示的反相器电路中,欲加深二极管T的饱和深度,在其他条什不变的情况下,可采取的措施。

(a)增大R2:

(b减少RC(c)减少VCE(d)增大T的答案:

d(难)0000010154、扇山系数No是指逻辑门电路。

(a)输出电压与输入电压之间的关系数(b)输iU电压与输入电流之间的关系数(c)输出端能带同类门的今个数(d)输入端数答案:

c(难)0000010153、为实现,下列电路接法正确的是。

答案:

d(难)0000010162、TTL与非门的关门电平0.7V,开门电平为1.9V,当其输入低电平为0.4V,输入高电平为3.2V时,其低电平噪声容限为。

(a)1.2V(b)2.1V(c)0.3V(d)1.5V答案:

c(难)0000010166、两输入变量A、B的辑门的输出、输入如图3.11所示,根据输出波形F应该属于。

(a)与非门(b)或非门(c)同或门(d)与门答案:

c(难)0000040190、下列电路中,只有()不能实现Qn1n。

答案:

d难0000040192、如下各触发器电路中,能实现Qn1nA功能的电路是()。

答案:

b难0000050203、在设计同步时序电路时,检查到不能自行启动时,则()。

(a)只能用反馈复位法清零(b)只能用修改驱动方程的方法(c)必须用反馈复位法清零并修改驱动方程(d)可以采用反馈复位法(置位法),也可以采用修改驱动方程的方法保证电路能白行启动。

答案:

b难0000050204、已知Q3Q2Q1Q0是同步十进制计数器的触发器输出,若以Q3作进位,则其周期和脉冲宽度是()。

(a)10个CP脉冲,正脉冲宽度为1个CP周期(b)10个CP脉冲,正脉冲宽度为2个CP周期(c)10个CP脉冲,正脉冲宽度为4个CP周期(d)10个CP脉冲,正脉冲宽度为8个CP周期答案:

b难0000050206、若4位同步二进制加法计数器正常工作时,由0000状态开始计数,则经过43个输入计数脉冲后,计数器的状态应是()。

(a)0011(b)1011(c)110l(d)1110答案:

b难0000050217、用反馈复位法来改变由8位十进制加法计数器的模值,可以实现()模值范围的计数器。

(a)l10(b)116(c)199(d)1100答案:

d难0000050218、异步计数器设计时,比同步计数器设计多增加的设计步骤是()。

(a)画原始状态转换图(b)进行状态编码(c)求时钟方程(d)求驱动方程答案:

c难0000060228、利用门电路的传输时间,可以把()个与非门首尾相接,组成多谐振荡器。

(a)8(b)7(c)6(d)4答案:

b难0000060229、如图78所示的由555定时器组成的电路是()电路。

(a)施密特触发器(b)单稳态触发器(c)双稳态触发器(d)多谐振荡器答案:

d难0000060230、在图79所示的4个电路中,不能产生振荡的是()。

答案:

a难0000060232、图7.1.1所示电路是一种()电路。

(a)多谐振荡器(b)双稳态触发器(c)单稳态触发器(d)施密特触发器答案:

c难0000070240、衡量AD和DA转换器性能优劣主要指标是()。

,(a)分解度(b)线性度(c)功率消耗(d)转换精度和转换速度答案:

d难0000070241、在构成DA转换器的电路中,不属于DA转换器组成部分的是()。

(a)数码锁存器(b)电子开关(c)电阻网络(d)译码器答案:

d难0000070250、已知一个8位二进制DA转换器的输出阶梯电压Vo=0.02V,则它的最大输出电压为()V。

(a)5.12(b)20.48(c)20.46(d)5.1答案:

d难0000070251、已知一个3位十进制(DCB编码)DA转换器的输出阶梯电压Vo=0.02V,则它的最大输出电压为()V。

(a)10.0(b)9.99(c)8.0(d)7.0答案:

b难0000080264、ispLSI器件中的GLB是指()。

(a)全局布线区(b)通用逻辑块(c)输出布线区(d)输出控制单元答案:

b难0000030285、下列表达式中不存在竞争冒险的是()。

(a)(b)(c)(d)答案:

b难0000030287、下列哪一项不是组合逻辑电路消除竞争冒险的方法()。

(a)后级加缓冲电路(b)接入滤波电容(c)修改逻辑设计增加冗余项(d)引入封锁脉冲答案:

a难0000040298、边沿式D触发器是一种()稳态电路。

(a)无(b)单(c)双(d)多答案:

c难0000050307、用二进制异步计数器从0做加法,计到十进制数178,则最少需要()个触发器。

(a)1(b)6(c)8(d)10答案:

d难0000050308、某电视机水平垂直扫描发生器需要一个分频器将31500HZ的脉冲转换为60HZ的脉冲,欲构成此分频器至少需要()个触发器。

(a)10(b)60(c)525(d)31500答案:

a难0000050309、N个触发器可以构成最大计数长度(进制数)为()的计数器。

(a)N(b)2N(c)N2(d)2N答案:

d难0000010335、如右图所示,TTL与非门带同类门的个数为N,其低电平输入电流为1.5mA,高电平输入电流为10uA,最大灌电流为15mA,最大拉电流为400uA,选择正确答案()。

(a)N5(b)N10(c)N20(d)N40答案:

b难0000010339、在下面四图中,能实现给定逻辑功能的是()。

(a)(b)(c)(d)答案:

d难0000010340、右图实现的逻辑功能为()。

(a)与门(b)与非门(c)或非门(d)异或门答案:

d难0000010342、下列器件不属于TTL集成电路的是()(a)74LS373(b)74LS00(c)74LS02(d)CD4511答案:

d难0000010344、如右图的表达式为()。

(a)(b)(c)(d)答案:

b难0000010345、已知波形如右图,L与A、B、C、的关系为()。

(a)(b)(c)(d)答案:

d难0000020352、(a)(b)(c)(d)答案:

a难0000020353、(a)(b)(c)(d)答案:

b难0000040369、主从J-K触发器由主触发器和从触发器组成,从触发器在何时工作()。

(a)CP0(b)CP1(c)CP上升沿(d)CP下降沿答案:

a难0000040370、下列哪类触发器用来构成移位寄存器()。

(a)D触发器(b)R-S触发器(c)T触发器(d)JK触发器答案:

a难0000040371、时序逻辑电路设计成败的关键在于()。

(a)状态的编码(b)状态转换表的建立(c)未用状态检验(d)是否具有自启动功能答案:

b难0000050373、判断图示电路为何种计数器()。

(a)异步二进制减法(b)同步二进制减法(c)异步二进制加法(d)异步二进制加法答案:

a难0000060387、在555定时器组成的三种电路中,能自动产生周期为T0.69(R1+2R2)C的脉冲信号的电路是()(a)施密特触发器(b)单稳态触发器(c)多谐振荡器(d)555定时器答案:

c难0000010439、若干个三态逻辑门的输出端连接在一起,能实现的逻辑功能是()。

(a)线与(b)无法确定(c)数据驱动(d)分时传输数据答案:

d难0000010440、晶体管的饱和深度变浅时,TTL门的传输延迟时间tpd()。

(a)增大(b)减小(c)不变(d)无法确定答案:

b难0000010441、逻辑电路的输入端对地接20k电阻,对于TTL电路,相当于接逻辑()(a)1(b)0(c)高(d)无法确定答案:

b难0000010442、逻辑电路的输入端对地接20k电阻,对于CMOS电路,相当于接逻辑()(a)1(b)0(c)负(d)无法确定答案:

a难0000040448、既克服了空翻现象,又无一次变化问题的集成触发器是()。

(a)边沿JK触发器(b)同步D触发器(c)同步(d)基本RS触发器答案:

a难0000030472、8421BCD编码器的输入变量为()个。

(a)8(b)4(c)10(d)7答案:

c难0000030474、半导体数码管通常是由()个发光二极管排列而成。

(a)5(b)6(c)7(d)8答案:

c难0000030475、七段显示译码器要显示数“2”则共阴极数码显示器的ag引脚的电平为()。

(a)1101101(b)1011011(c)1111011(d)1110000答案:

a难0000030476、一个16选1的数据选择器,其数据地址输入端有()个。

(a)1(b)2(c)4(d)8答案:

c难0000030478、一个8路数据分配器,其数据地址输入端有()个。

(a)1(b)2(c)3(d)4答案:

c难多选题0000010507、三极管作为开关使用时,要提高开关速度,可()。

(a)降低饱和深度(b)增加饱和深度(c)采用有源泄放回路(d)采用抗饱和三极管答案:

a、c、d难0000010524、图中TTL集成门电路的输入端1、2、3为多余输入端,接法正确的是()(a)(b)(c)(d)答案:

a、b、d难0000010537、双极性集成电路包括。

()(a)TTL(b)ECL(c)HTL(d)I2L答案:

a、b、c、难00000202559、等于()。

(a)(b)(c)(d)答案:

a、c难0000020580、求一个逻辑函数F的对偶式,可将F中的().(a).“”换成“+”,“+”换成“”(b)原变量换成反变量,反变量换成原变量(c)变量不变(d)常数中“0”换成“1”,“1”换成“0”答案:

a、c、d难0000020584、下列表达式正确的是()。

(a)(b)(c)(d)答案:

b、c难0000020585、最小项的逻辑相邻项是()。

(a)(b)(c)(d)答案:

a、c、d难0000020587、逻辑函数F1、F2、F3的卡诺图如图所示,它们之间的逻辑关系是()。

(a)F3F1F2(b)F3F1F2(c)F1F3F2(d)F1,F3互为对偶式答案:

b、d难0000020588、逻辑函数F1=与F2=之间的关系是()。

(a)F1F2(b)F12(c)1F2(d)F1,F2互为对偶式答案:

a、d难0000030589、A1,A2,A3,A4,A5为5个开关,它们闭合时为逻辑1,断开时为逻辑0,电灯F=1表示灯亮,F=0表示灯灭,若在5个不同的地方控制同一盏灯的亮灭,则函数F=().(a)A1A2A3A4A5(b)A1+A2+A3+A4+A5(c)A1A2A3A4A5(d)A1A2A3A4A5答案:

c、d难0000030590、八路数据选择器如图所示,该电路实现的逻辑函数是F=()。

(a)(b)(c)(d)答案:

a、d难0000030594、如图所示的组合逻辑电路,其函数表达式为()。

(a)(b)(c)(d)答案:

a、d难0000030595、八路数据选择器如图所示,该电路实现的逻辑函数是()。

(a)(b)(c)(d)答案:

a、c难0000030596、下列表达式中不存在竞争冒险的有()。

(a)(b)(c)(d)答案:

c、d难0000030597、函数,当变量的取值为()时,将出现冒险现象。

(a)B=C=1(b)B=C=0(c)A=1,C=0(d)A=0,B=0答案:

a、c、d难0000030599、用三线-八线译码器74LS138实现原码输出的8路数据分配器,应()。

(a).(b)(c)(d)答案:

a、b、c难0000040633、基本RS触发器可用于()。

(a)键盘输入(b)开关消噪(c)防抖动(d)数据运算答案:

a、b、c难0000040651、电路如图所示,经CP脉冲后,欲使Qn+1Qn,则A、B输入应为()。

(a)AB=00(b)AB=01(c)AB=10(d)AB=11答案:

a、d难0000040652、下列电路中能完成Qn+1Qn的逻辑功能的电路是()(a)(b)(c)(d)答案:

a、c、d难0000040656、下列电路中能完成Qn+1n逻辑功能的电路是()(a)(b)(c)(d)答案:

a、c、d难0000060701、逻辑电路如图所示,下列Q2Q1Q0状态属于电路的有效状态()。

(a)000(b)010(c)110(d)100答案:

a、b、c难0000060706、计数器电路及其各级输出波形如图所示,下面对该计数器的分析正确的是()。

(a)触发方式是上升沿触发(b)同步计数器(c)异步计数器(d)两位二进制加法计数器答案:

a、c、d难0000070724、一个无符号10位数字输入的DAC,其输出电平的级数为()。

(a)4(b)10(c)1024(d)210答案:

c、d难0000070725、逐次逼近型A/D转换器由()和时钟信号等几部分组成。

(a)电压比较器(b)A/D转换器(c)控制逻辑电路(d)逐次逼近寄存器答案:

a、b、c、d难0000070729、DAC0832根据其6个控制信号的不同连接方式,有()三种工作方式。

(a)单级缓冲工作方式(b)双级缓冲工作方式(c)多级缓冲工作方式(d)直通工作方式答案:

a、b、d难0000070735、下列对双积分型ADC特点的描述,正确的是()。

(a)抗交流干扰能力强(b)工作性能稳定(c)工作速度高(d)工作速度低答案:

a、b、d难0000070736、下列常用的集成ADC属于双积分型的有()(a)ICL7107(b)AD574A(c)ICL7106(d)ADC0809答案:

a、c难0000080739、PLD的设计方法主要有()。

(a)积木式(b)模块式(c)自下而上式(d)自上而下式答案:

a、b、c、d难0000080740、一个完整的PLD设计流程有哪几个步骤和两种验证过程。

()(a)设计准备(b)设计输入(c)设计处理(d)器件编程答案:

a、b、c、d难0000080741、一个完整的PLD设计流程有设计准备、设计输入等四个步骤和()两验证过程。

(a)设计校验(功能仿真和时序仿真)(b)器件加密(c)器件老化(d)器件测试答案:

a、d难0000080748、可檫除的可编程逻辑器件EPLD的基本逻辑单位是宏单元,它由()三部分组成。

(a)可编程的与或阵列(b)可编程寄存器(c)可编程I/O(d)可编程的与非阵列答案:

a、b、c、难0000080749、复杂可编程逻辑器件CPLD是EPLD的改进型器件,一般情况下,CPLD器件至少包含三种结构()。

(a)可编程逻辑宏单元(b)可编程I/O单元(c)可编程寄存器(d)可编程内部连线答案:

a、b、d难0000080751、PLD中阵列交叉点上有()三种连接方式。

(a)交叉连接(b)接通连接(c)硬线连接(d)断开连接答案:

b、c、d难0000080754、PROM和PAL的结构是()。

(a)PROM的与阵列固定,不可编程(b)PROM与阵列、或阵列均不可编程(c)PAL与阵列、或阵列均可编程(d)PAL的与阵列可编程答案:

a、d难0000080758、PLD开发系统需要有()。

(a)计算机(b)编程器(c)开发软件(d)操作系统答案:

a、b、c、d难0000080761、ISP-PLD器件开发系统的组成有()。

(a)计算机(b)编程器(c)开发软件(d)编程电缆答案:

a、c、d难0000070768、D/A转换器的转换误差包括()。

(a)偏移误差(b)增益误差(c)线性误差(d)非线性误差答案:

a、b、d难0000070769、A/D转换器的转换误差包括()。

(a)线性误差(b)增益误差(c)偏移误差(d)非线性误差答案:

b、c、d难0000070770、在构成D/A转换器的电路种,属于D/A转换器的组成部分的是()(a)数码锁存器(b)电子开关(c)电阻网络(d)译码器答案:

a、b、c难000007

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 电子

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx