数字频率计电路.docx

数字频率计电路.docx

- 文档编号:7967778

- 上传时间:2023-01-27

- 格式:DOCX

- 页数:47

- 大小:399.92KB

数字频率计电路.docx

《数字频率计电路.docx》由会员分享,可在线阅读,更多相关《数字频率计电路.docx(47页珍藏版)》请在冰豆网上搜索。

数字频率计电路

第二章电路的总体设计方案

2.1方案论证与选择

2.1.1方案的提出

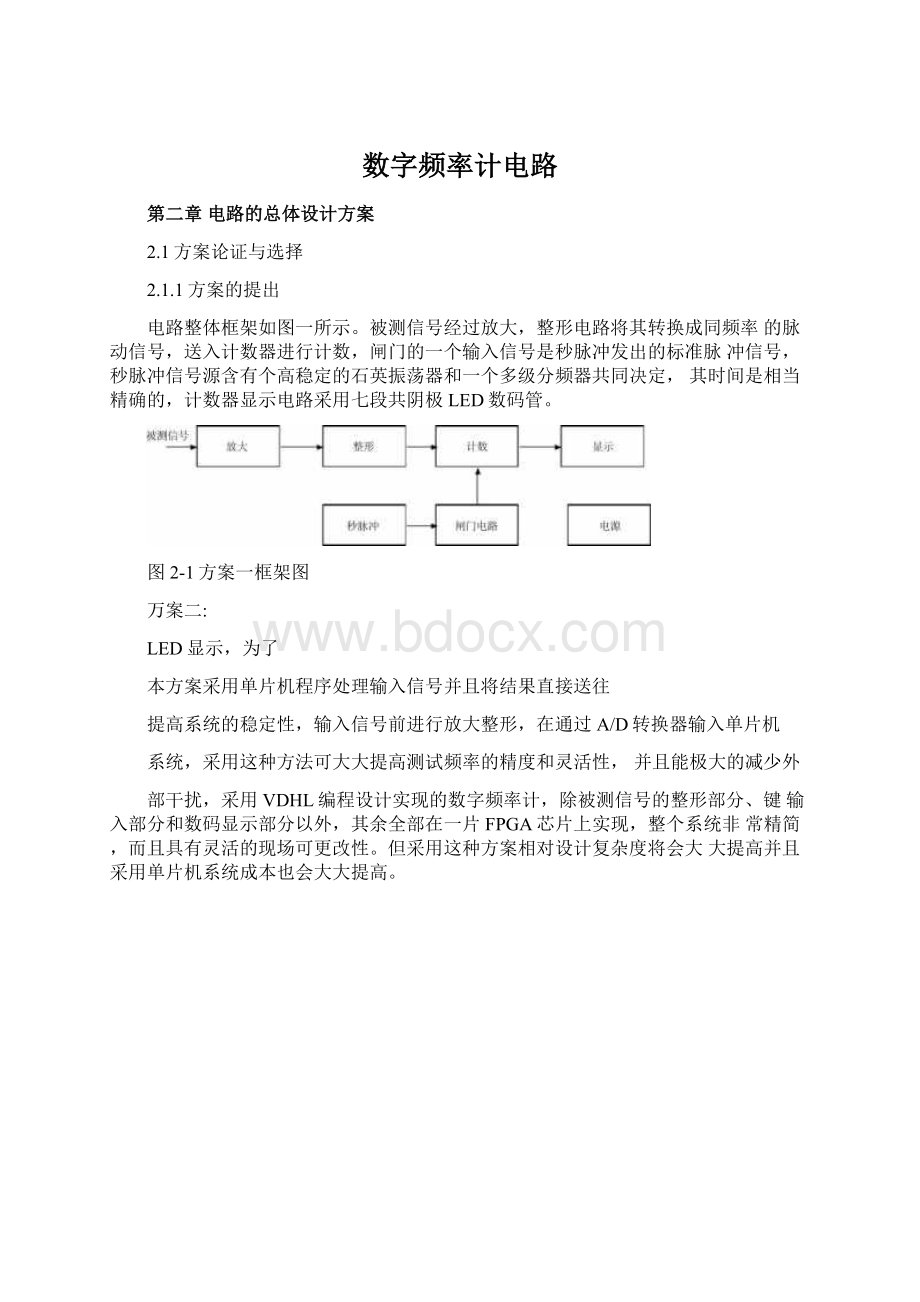

电路整体框架如图一所示。

被测信号经过放大,整形电路将其转换成同频率的脉动信号,送入计数器进行计数,闸门的一个输入信号是秒脉冲发出的标准脉冲信号,秒脉冲信号源含有个高稳定的石英振荡器和一个多级分频器共同决定,其时间是相当精确的,计数器显示电路采用七段共阴极LED数码管。

图2-1方案一框架图

万案二:

LED显示,为了

本方案采用单片机程序处理输入信号并且将结果直接送往

提高系统的稳定性,输入信号前进行放大整形,在通过A/D转换器输入单片机

系统,采用这种方法可大大提高测试频率的精度和灵活性,并且能极大的减少外

部干扰,采用VDHL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分以外,其余全部在一片FPGA芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。

但采用这种方案相对设计复杂度将会大大提高并且采用单片机系统成本也会大大提高。

Vin

图2-2方案二框架图

采用频率计专用模块,即大规模集成电路将计数器、锁存器、译码、位和段驱动,量程及小数点选择等电路集成在一块芯片中,该方案在技术上是可行的,可以简化电路的设计,当对于设计要求中的某些指标,采用专用模块来完成比较困难,即扩展极为不便。

图2-3方案三框架图

2.1.2方案的的比较

方案一:

具有设计复杂度小、电路简洁、功能实用且成本低廉等特点,其稳定性较好基本能满足设计要求。

方案二:

采用单片机处理能较高要求,但成本提高且设计复杂,虽然可以达到很高的精度要求,但是,VHDL编程语言是我们在学习过程中没有接触过的,短期内也很难掌握并且熟练运用。

方案三:

用专用频率计设计模块固然设计简单且稳定但系统可扩展性能较差。

2.1.3方案的选择

综合三种方案比较:

我感觉方案一和我以前学的专业知识更接加近些,电路原理容易理解,所设计的数字频率计稳定性好,基本上能够满足设计要求,所以我采用第一种设计方案。

图2—5数字频率计组成框图

在我的毕业设计中,数字频率计由信号输入电路、分频电路、放大整形电路、闸门电路、时基电路、逻辑控制电路、计数电路、锁存电路、译码显示电路,小

数点移位电路,量程选择开关等组成

所谓频率,就是周期性信号的在单位时间(1s)内变化的次数,若在一定时间间隔T内测得这个周期性信号的重复变化次数为N,则其频率可表示为:

f二nt(2—1)

上图是数字频率计的结构框图。

被测信号经放大整形电路变成计数器所要求的脉冲信号I,其频率与被测信号的频率fx相同。

时基电路提供标准时间基准信号U,其高电平持续的时间ti=1s,当1s信号来到时,闸门开通,被测脉冲信号通过闸门,计数器开始计数,直到is信号结束时闸门关闭,停止计数。

若在闸门时间is内计数器计得的脉冲个数为N,则被测信号频率fx=NHz。

逻辑控制电路的作用有两个:

一是产生锁存脉冲,使显示器上的数字稳定;二是产生清“0”脉冲V,使计数器每次测量从零开始计数。

频率计中各信号波形如图2—6所示:

IJWWW1TL.JUL...JUL

nIti比|

计数

□rLTwinmrururLTL

4——亠-——

锁存

」消5

图2—6频率计中各信号波形

说明:

1、脉冲信号I为被测信号经放大整形电路后变成的计数器所要求的脉冲信号,其频率与被测信号的频率fx相同,或与被测信号的频率呈一定的比例关系。

2、信号U为时基电路提供的标准时间基准信号,其高电平持续时间为1S,当此信号来到,闸门开通,被测脉冲信号通过闸门,使计数器开始计数;此信号

结束,则闸门关闭,计数器停止计数。

U脉冲信号又可称为闸门时间脉冲,用T

表示。

3、脉冲信号川为闸门时间脉冲控制下闸门所输出的脉冲,因为要将它送入计数器进行计数,所以又将闸门所输出的川信号称为计数脉冲信号。

若在闸门时间1S内计数器计得的脉冲个数为N,则被测信号频率fx=NHz。

4、脉冲信号W即为锁存信号,是逻辑控制电路产生的,控制锁存器锁存计数结果的控制信号,它由时基信号U结束时产生的负跳变来产生。

5、脉冲信号V是计数器的清零信号,也是逻辑控制电路所产生,用于控制计数器进行清零,使计数器每次测量从零开始计数。

它是由锁存信号W结束产生的负跳变来产生。

在这个总的电路设计中包含有几个不同功能的分电路,每个电路在本设计中都有着自己特有的功能,也只有这几个分电路组合在一起才使得整个的电路实现其所要达到的功能。

所以还是先介绍一下每一个分电路的功能特点。

第三章硬件电路设计

3.1时基电路和闸门电路

3.1.1时基电路

时基电路的作用是产生一个标准时间信号,其高电平持续时间为1s,由555定时器构成的多谐荡器产生。

a.555定时器内部结构

555定时器是一种模拟电路和数字电路相结合的中规模集成电路,其内部逻辑电路结构如图3—1(a)所示及管脚图如图3—1(b)所示:

5toj

6frjT

2k

So0

'OUT

ID

7

5KQ

1CND

图3—1(a)555定时器内部逻辑电路结构

Ucc

DTH

co

76

5

3

NE555

i

23

4

LJ

LIL

鈕?

脈4局

图3—1(b)555定时器管脚图

它由分压器、比较器、基本R--S触发器和放电三极管等部分组成。

分压器由三个5K"的等值电阻串联而成。

分压器为比较器A,、A提供参考电压,比较

2

器A的参考电压为一V,加在同相输入端,比较器A的参考电压为■Vc,加在

3

反相输入端。

比较器由两个结构相同的集成运放A,、A一组成。

高电平触发信号

加在A的反相输入端,与同相输入端的参考电压比较后,其结果作为基本R--S

触发器Rd端的输入信号;低电平触发信号加在A2的同相输入端,与反相输入端的参考电压比较后,其结果作为基本R—S触发器Sd端的输入信号。

基本R--S

触发器的输出状态受比较器A,、A2的输出端控制。

b.多谐振荡器工作原理

由555定时器组成的多谐振荡器如图3—2(a)所示,其中R1、R2和电容C

为外接元件。

其工作波如图3—2(b)所示:

图3—2(a)由555定时器构成的多谐谢振荡器

°》

图3—2(b)由555定时器构成的多谐谢振荡器工作波形

设电容的初始电压Uc=0,t=0时接通电源,由于电容电压不能突变,所以咼、低触发端VTH=VTL=0v・Vcc,比较器A1输出为咼电平,A2输出为低电平,即RD=1,Sd=0(1表示高电位,0表示低电位),R-S触发器置1,定时器输出Uo=1此时6=0,定时器内部放电三极管截止,电源Vcc经R,R2向

1

电容C充电,U逐渐升高。

当u上升到-Vcc时,A2输出由0翻转为1,这时

3

Rd=Sd=1,R-S触发顺保持状态不变。

所以0 电平1。 2_ t=ti时刻,u上升到-Vcc,比较器A的输出由1变为0,这时Rd=0, 3 SD=1,R-S触发器复0,定时器输出5=0。 ti: : t: : t2期间,Q=1,放电三极管T导通,电容C通过R2放电。 u按指数 2 规律下降,当Uc: : : 2Voc时比较器A输出由0变为1,R—S触发器的 3 Rd=1,Q的状态不变,U0的状态仍为低电平。 t凯2时刻,u下降到■Vcc,比较器A2输出由1变为0,R---S触发器的 Rd“,Sd=0,触发器处于1,定时器输出Uo=1。 此时电源再次向电容C放电,重复上述过程。 表3—1555集成定时器的功能表 R Vjh Vtr % td 0 X X 0 —导通 1 大于2/3抵 大于1/3Vg 0 导通 1 丿卜于2/3Vco 小于1/3Vcc 1 截止 1 小于2/3Vcc 夫于1/3屁v 保持 保持 本设计需要的时基信号波形如图3-3所示 Vo ▲ t2 0.25S 图3-3本设计要求的时基波形 振荡器的输出波形如图3-3所示,其中t^1s,t2二0.25s。 由公式 t^0.7R1R2C和t2=0.7R2C,可计算出电阻R1,R2及电容C的值.若取电容 )=35.7KO取R2=36K0 Ri二t107c—R2JO7.1K「取Ri=107K「 可得到本设计的时基电路,如图3—4所示: +5 555 R1107K Fd Ct THOUT R2 36K 5 lOuF 1 0.01uF TR To GND 图3-4时基电路 3.1.2闸门电路 测量控制电路(闸门电路): 用于控制输入脉冲是否送给计数器计数。 由一 C 个数字逻辑元件与非门来独立完成,其一端输入高电平持续时间为1s(0.25s) 的时基信号,另一端输入经过放大整形后的未知频率的待测信号,与非门的输出端接低位计数器的信号输入端。 如图3-5所示: 图3-5闸门电路 闸门电路部分的与非门选用74LS00,74LS00是四2输入与非门。 其管脚图如图3-6所示。 表3-274LS00真值表 输入 输出 A B Y 0 0 1 0 1 0 1 0 0 1 1 0 3.2放大和整形电路 为了能测量不同电平值与波形的周期信号的频率,必须对被测信号进行放大与整形处理,使之成为能被计数器有效识别的脉冲信号。 信号放大与波形整形电路的作用即在于此。 3.2.1放大电设计 低频放大电路采用由3DG100构成带电流串联负反馈的分压式单管共射放大电路比较合适,工作点稳定,工作频率范围较宽,放大器输入阻抗比较大。 电路结构如图3-7所示: El 在图3-7所示低频信号放大电路中,三极管3DG100起电流放大作用,是组成放大器电路的关键元件。 直流电源Vcc提供整个放大电路的能源,并且与电阻R1,R2,Rp确定三极管合适的静态工作状态,即保证三极管的发射结正向偏置,集电结反向偏置,使三极管处于正常放大的状态。 集电极通过一个电阻Re接地,通过该电阻的反馈来自动调节Ube的大小,使Ube基本保持不变。 为了增大放大倍数,减少输入阻抗,在Re的两端并联一 个较大的旁路电容Ce,若Ce两端的交流压降可以忽略,则电压放大倍数将不会因此而下降。 电容C的作用是隔直流。 高频放大电路采用的是ucp1651芯片对高频信号进行放大,放大电路如图 3-8所示: 3.2.2整形电路设计 Title 整形电路的作用是将输入的周期性信号,如正弦波、三角波或其他呈周期性变化的波形变换成脉冲波,其周期不变。 将其他波形变换成脉冲波的电路有多种,如施密特触发器、单稳态触发器、比较器等,本设计用到是过零比较器,如图3-9 所示: 在整形电路中比较放大电路采用OP37将输入得非方波信号(如正弦波,三角波等)转换为方波加以限幅,消波,在利用7404整形使其转换成TTL电平输出。 输出波形如图3-10所示: 图3-10脉冲形成电路波形图 本电路由放大电路与整形电路两部分组成。 对于输入幅度比较小的正弦波, 三角波,方波信号,要测量其频率大小,首先要进行放大整形,变成同频率的方A 波信号,实现此功能的电路如图3-11所示: SzeNumber B Date: 9-Jun-2010 Revision Sheetof DrawnBy: Fle: J\pbj123DDB +5V 7404 3.3逻辑控制电路 控制电路是通用电子计数器完成逻辑控制的指挥系统,控制着主闸门的开启和关闭。 在控制电路的协调指挥下,全机各部分电路协调动作,完成各项测量工作。 通用电子计数器的测量程序是计数一显示一复零。 也就是说,在主门开启的时间内进行计数,然后由显示电路将计数结果显示出来,接着发出复零信号使仪器又恢复到测量前的初始工作状态。 逻辑控制电路用来产生两种控制信号,一种是控制锁存器锁存的脉冲信号,另一种是产生计数器的清零信号,这两种信号都需要由信号负跳变触发,其中控制锁存的信号是由时基信号负跳变触发,清零信号则是由锁存信号的负跳变触发产生,这里就需要用到单稳态触发器,两种信号各由一单稳态触发器负责产生。 经选择采用双单稳态触发器74LS123,手动复位开关S按下时,计数器清“0”其电路如图3-12所示: 图3-12逻辑控制电路图 CEMTCE1T_ Vqq1101Q3CLR29? A? J 1$\1S(14 13 13|l1 10 9 尸" J J— CLH 一□ Z O 123 4 F-k 厂 AlBlCLRQ1Q2CextRemT; 1=CfeXf 2 图3-1374LS123管脚图 表3-474LS123功能表 输 A 输 岀 CLR A B Q Q 0 X X 0 i X 1 X 0 i X X 0 0 1 1 t 正脉冲 负脉冲 1 1 正脉冲 负脉冲 t 0 1 正脉冲 负脉冲 设锁存信号和清零信号的脉冲宽度t..相同,如果要求t.=0.02s则得 t.=0.45RextCext=0.02s 若取Rext=10K则Cext」2545隘=4.4丹取标称值4.7円 3.4锁存器 3.4.1电路的选择 锁存器是构成各种时序电路的存储单元,具有0和1两种状态,一旦状态确 定就能自行保持,即长期保持一位二进制码,直到有外部信号作用时才有可能改变。 锁存器是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电 平作用下改变状态。 锁存器的作用是将计数器在1s结束时所计得的数进行锁存,使显示器上获 得稳定的测量值。 因为在1s内要计成千上万个输入脉冲,若不加锁存器,显示器上的数字将随计数器的输出而变化,不便于读数。 1s计数结束时,逻辑控制 电路发出锁存信号,将计数器此时的值送译码显示器,因此显示器的数字是稳定的。 选用8D锁存器74LS273可以完成上述功能.当时钟脉冲CP的正跳变来到时,锁存器的输出等于输入,即Q=D。 从而将计数器的输出值送到锁存器的输出端。 正脉冲结束后,无论D为何值,输出端Q的状态仍保持原来的状态Qn不变•所以在计数期间内,计数器的输出不会送到译码显示器。 锁存器连接如图 3-14所示: 2 5 6 9u 2 5 6 9 II 5 Q 6 1Q 1 1 23QQ )Q U? 74ALS273 U? 74ALS273 2569 U? 74ALS273 klc 1D 2d 3d 4d 5d 6d 7d 8d rlc klc 1D 2d 3d 4d 5d 6d 7d 8d rlc klc 1D 2d 3d 4d 5d 6d 7d 8d rlc 控制锁存器信号输入 图3-14锁存器连接电路图 选用三个8位锁存器74L273可以完成上述功能。 当时锁存信号CP的正跳变来到时,锁存器的输出等于输入。 从而将计数器的输出值送到锁存器的输出端。 高电平结束后,无论D为何值,输出端的状态仍保持原来的状态不变。 所以,在 计数期间内,计数器的输出不会送到译码显示器。 D触发状态转换真值表如图所示: Title CP D B Date: 说明 9-Jin-2010 t 0 0 Q5 Fie: _J\pbj123.DDB f 0 1 0 0 t 1 0 I 1 1 1 I 1 表3-5D触发状态转换真值表 SzeNumber Shee Draw 3428位数据/地址锁存器74LS273 74LS273是带清除端的八D触发器,只有清除端为高电平时才具有锁存功能,锁存控制端为11脚CLK,在上升沿锁存。 74LS273的1脚是复位CLR,低电平有效,当1脚是低电平时,输出脚2(Q0)、 5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部输出0,即全部复位;当1脚为高电平时,11(CLK)脚是锁存控制端,并且是上升沿触发锁存,当11脚有一个上升沿,立即锁存输入脚3、4、7、8、13、14、17、18的电平状态,并且立即呈现在在输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)上。 74LS273的逻辑功能是,当时钟脉冲CP的正跳变来到时,锁存器的输出等于输入,既Q=D。 正脉冲结束后,无论D为何值,输出端Q的状态仍保持原来的状态Qn不变。 74LS237的引脚图如图3-15所示 图3-1574LS273管脚图 当脉冲CLK的正跳变到达,锁存器的输出等于输入,即Q=D。 从而将 从而将六个十进制计数器即个位、十位、百位、千位、万位、十万位的输出值送到锁存器的输出端,正脉冲结束后,无论D为何值,输出端Q的状态仍保持原 来的状态不变,所以在计数期间计数器的输出不会送到译码显示器。 3.5译码显示电路设计 3.5.1七段数字显示器 在数字测量仪表和各种数字系统中,都需要将数字量直观地显示出来,一方 面供人们直接读取测量和运算的结果;另一方面用于监视数字系统的工作情况。 因此,数字显示电路是许多的数字设备不可缺少的部分。 数字显示电路通常由译 码器,驱动器和显示器等几个部分组成,如图3-16所示: 脉沖信哥 图3-16数字显示框图 下面对显示器和译码器驱动器分别进行介绍。 电子显示技术的应用与研究涉及的范围很广,包括各种发光材料的发光机理的研究、实验;各种显示方式的基本原理及其结构形式,显示用的材料与器件的 选择和制作工艺;显示信息的输入、变换、处理和控制,等等。 随着科学技术的发展,随着经济、军事、社会与人们生活的发展,信息的种类和数量不断增加。 人们生活在信息计会中,每时每刻都在获得某种信息。 数码显示器是用来显示数字,文字或符号的器件,现在已有很多种不同类型的产品,广泛应用与各种数字设备中,目前数码显示器件正朝着小型,低功耗,平面化方向发展。 数码显示方式一般有三中: 第一种是字形重叠式,它是将不同字符的电极重叠起来,要显示字符,只需要使相应的电极发光即可,如辉光放电管,边光显示管等。 第二种是分端式,数码是由分布在同一平面上若干端发光的笔划组成,如 荧光数码管等。 第三种是点阵式,它由一些按一定规律排列的可发光的点阵组成,利用光点的不同的组合便以显示不同的数码,如场发光记分牌。 近年来,由于半导体的制作和加工工艺逐步成熟和完善,发光二极管(LED: LightEmittingDiode)已日趋在固体显示中占主导地位。 LED之所以受到广泛 重视而得到迅速发展,是与它本身所具有的优点分不开的。 这些优点概括起来是: 亮度高、工作电压低、功耗小、小型化而易与集成电路匹配、驱动简单、寿命长、耐冲击和性能稳定。 LED的发展前景极为广阔,目前正朝着更高亮度、更高耐气候性、更高的发光密度、更高的发光均匀性、可靠性、全色化方向发展。 由 组成半导体的材料不同而可以得到能发出不同色彩的LED晶点。 近几年,随着 微电子技术、自动化技术、计算机技术的迅速发展,半导体制作工艺日趋成熟,导致LED显示点尺寸越来越小,解析度越来越高,而可将显示光的三基色(红、绿、蓝)复原成全彩色效果,使得发光二极管(LED)作为显示器件的应用范围日益扩大。 为了使数码管能将数码所代表的数显示出来,必须将数码经译码器译出,然 后经驱动器点亮对应的段 计数显示电路采用十进制计数/七段译码器和七段LED数码管组成8位十进制计数显示器。 内部包含十进制计数和七段译码器两部分,译码输出可以直接驱动LED数码管。 R为清零端,当R=1时计数器全部清零。 INH端接闸门控制信号,当INH=0时,计数器计数;当INH=1时,停止计数,但显示的数字被保留。 电路中的RBI与RBO端多级级联,作用是自动消隐无效零。 例如,计数状态为“000680”电路自动消隐左边三位无效零,显示为“680”以符合习惯。 LED显示 LED(Light-EmittingDiode,发光二极管)有七段和八段之分,也有共阴和共阳两种。 LED数码显示管显示原理和结构 单个LED是由7段发光二极管构成的显示单元,有10个引脚,对应于7个段、一个小数点和两个公共端。 LED数码管结构简单,价格便宜。 图2.7.1是八段LED数码管的结构和原理图: 图3—16(a)为八段共阴数码管结构图。 八段数码管由八只发光二极管组成,编号是a、b、c、d、e、f、g和dp,分别与同名管脚相连。 dpba Q^=-dpH—dp-—=―H— 何并阴LED结构⑼共阴LED©共阳LED 图3-17八段LED数码管原理和结构 八段LED数码显示管原理很简单,是通过同名管脚上所加电平的高低来控 制发光二极管是否点亮从而显示不同字形的。 例如,若在共阴LED管的dp、g、f、e、d、c、b、a管脚上分别家上7FH控制电平(即dp上为0伏,不亮;其余为TTL高电平,全亮),贝ULED显示管显示字形“8”。 7FH是按dp、g、f、e、d、c、b、a顺序排列后的十六进制编码(0为TTL低电平,1为TTL高电平),常称为字形码。 因此,LED上所显示的字形不同,相应的字形码也不一样。 八段共阴能显示的字形及相应字形码如表1所列。 该表常放在内存中,SGTB为表的起始地址,个地址偏移量为相应字形码对表起始地址的项数。 由于“B”和“8”、 “D”和“0”字形相同,故“B”和“D”均以小写字母“b”和“d”显示。 图3—16(b)为共阳八段LED管的原理图。 图中,所有发光二极管阴极共连后接到引脚G,G脚为控制端,用于控制LED是否点亮。 若G脚接地、则LED被点亮;若G脚接TTL高电平,则它被熄灭。 图3—16(c)为共阳八段LED数码显示管原理图。 图中,所有发光二极管 阳极共连后接到G脚。 正常显示时G脚接+5V,各发光二极管是否点亮取决于a〜dp各引脚上是否低电平0伏。 因此,共阴和共阳所需字形码恰好相反,如表3—6所列。 表3-6八段LED数码显示管字形码表 地址偏移量 共阴字形码 共阳字形码 所显字符 SGTB+0H 3FH C0H 0 +1H 06H F9H 1 +2H &BH A4H 2 +3H 4FH B0H 3 +4H 66H 99H 4 +5H 6DH

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字频率计 电路

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx