电子设计自动化实验讲义B5.docx

电子设计自动化实验讲义B5.docx

- 文档编号:7964347

- 上传时间:2023-01-27

- 格式:DOCX

- 页数:13

- 大小:215.32KB

电子设计自动化实验讲义B5.docx

《电子设计自动化实验讲义B5.docx》由会员分享,可在线阅读,更多相关《电子设计自动化实验讲义B5.docx(13页珍藏版)》请在冰豆网上搜索。

电子设计自动化实验讲义B5

电子设计自动化实验指导书

信息与自动化学院

实验1EDA实验环境的熟悉

一、实验目的和要求:

1.熟悉EDA实验开发环境以及进行硬件测试所用开发板的使用方法

2.掌握使用VHDL输入法的基本流程。

二、实验设备

1.电脑,quartusii集成开发环境

2.GX_SOPC_EP3C10_EDK系统

三、实验内容

1.了解和熟悉QuartusII软件的菜单界面和命令功能

2.EDA开发软件QuartusII的基本使用方法

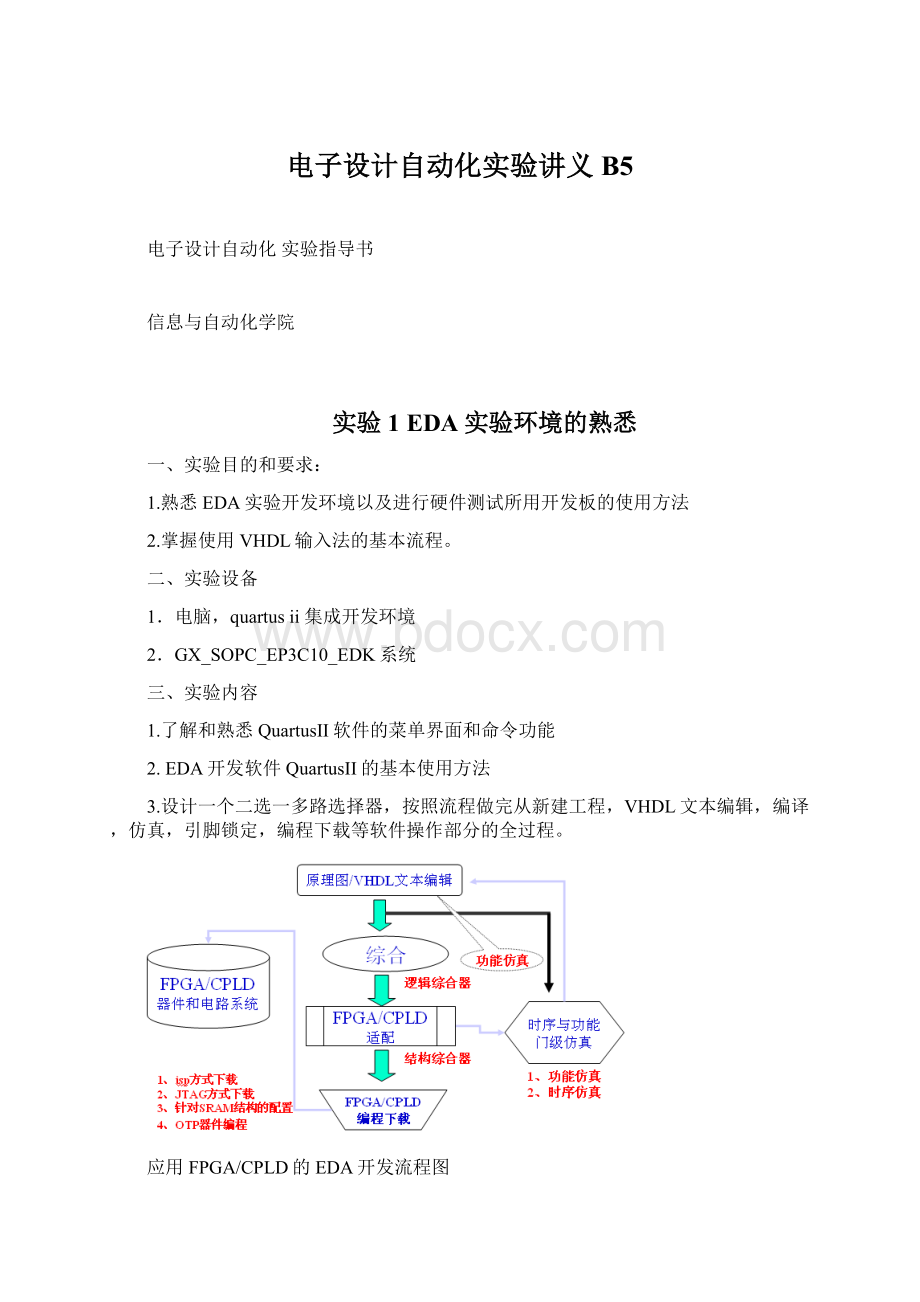

3.设计一个二选一多路选择器,按照流程做完从新建工程,VHDL文本编辑,编译,仿真,引脚锁定,编程下载等软件操作部分的全过程。

应用FPGA/CPLD的EDA开发流程图

程序:

LIBRARYieee;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmulti_2IS

PORT(s,d0,d1:

INSTD_LOGIC;

y:

OUTSTD_LOGIC);

ENDmulti_2;

ARCHITECTUREaa1OFmulti_2IS

BEGIN

PROCESS(s,d0,d1)

BEGIN

IF(s=’0’)THEN

y<=d0;

ELSE

y<=d1;

ENDIF;

ENDPROCESS;

ENDaa1;

画出仿真图

4.学习开发板的说明书以及使用开发板进行硬件测试的基本流程,最终对二选一多路选择器进行硬件测试。

将引脚按照如下模式分配。

设计端口芯片引脚开发板模块

SPIN_91SW1A

d0PIN_90SW2A

d1PIN_88SW4A

YPIN_72LED1

这样在S为不同的状态时,2个输入端d0,d1的状态可分别确定为可调,即可观察对应Y的输出结果。

记录观察到的结果。

实验24选1多路选择器的设计

一、实验目的

1、熟悉利用QuartusII开发数字电路的基本流程和QuartusII软件的相关操作。

2、熟悉QuartusII的VHDL文本设计流程、组合电路的设计仿真和测试。

二、实验原理

本实验主要设计一个简单的4选1多路选择器。

选择器有两个控制端,4个输入端,1个输出端。

其真值表如下:

控制端输出

S0S1Y

00A

01B

10C

11D

要求使用两到三种不同的程序方法(ifelse语句,whenelse语句,case语句)实现这个功能。

三、实验内容

1.自己编写程序:

根据4.1节的流程,利用QuanuslI完成4选1多路选择器(第3章习题3-2)的文本编辑输入和仿真测试等步骤,给出仿真波形。

2.硬件测试:

在实验系统上硬件测试,验证此设计的功能。

对于引脚锁定以及硬件下载测试。

四、设计原理图

从图中可见,共有6个输入状态,将引脚按照如下模式分配。

设计端口芯片引脚开发板模块

S0PIN_90SW2A

S1PIN_91SW1A

APIN_89SW3A

BPIN_88SW4A

YPIN_72LED1

C、D在编译时在芯片内部分别定义为1和0。

这样在S0S1为不同的状态时,4个输入端A、B、C、D的状态可分别确定为可调(A、B),0(C),1(D),即可观察对应的输出结果。

实验3计数器的设计

一、实验前的准备

把USB数据线一端接计算机USB接口,另一端接GX-SOPC-EP3C10-EDK开发板的USB_BLASTER接口。

开发板接上5V电源。

二、实验目的

1、熟悉利用QuartusII开发数字电路的基本流程和QuartusII软件的相关操作,

2、掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,利用JTAG进行下载等基本操作。

3、学习计数器的设计、仿真和硬件测试。

4、掌握原理图与文本混合设计方法。

三、实验设备

1.电脑,quartusii集成开发环境

2.GX_SOPC_EP3C10_EDK系统

四、实验原理

参考3.4节。

实验程序为例3-20,设计流程参考本章。

四、实验内容

根据4.1节在QuartusII上对例3-20进行编辑、编译、综合、适配、仿真。

说明例中各语句的作用。

给出其所有信号的时序仿真波形,根据波形详细描述此设计的功能特点,包括RST、EN、LOAD、DATA、CLK等信号的异步和同步特性。

查阅编译后的计数器的时序特点,从时序仿真图和编译报告中了解计数时钟输入至计数数据输出的延时情况,包括设定不同优化约束后的改善情况,以及当选择不同FPGA目标器件后的延时差距及毛刺情况,给出分析报告。

用本章介绍的不同方式锁定引脚并硬件下载测试。

引脚锁定后进行编译、下载和硬件测试实验。

将实验过程和实验结果写进实验报告。

硬件实验中,注意测试所有控制信号和显示信号,包括RST、EN、LOAD、DATA等的同步、异步特性,以及进位信号等。

五、设计原理图

从图中可见,首先判断使能端口EN状态,当起满足高电平时,判断三个输入端口A2、A1、A0的状态来决定八个输出的状态。

输入EN和A需要独立可变的输入激励,所以最好选择开关,独立可变,易于控制;译码输出为8位数据,根据真值表可看出使用独立显示各个数据位的设备较好,故选用8个LED指示灯来表示。

因此选用带有4个电平开关,8个LED的第二种组合较好,具体引脚分配见下。

六、引脚分配情况

下表为GX-SOPC-EDA-EP3C5/EP3C10-STARTER-EDK开发板引脚分配表:

设计端口芯片引脚开发板模块

CLKPIN_89SW4A

RSTPIN_91SW1A

ENPIN_90SW2A

LOADPIN_88SW3A

DOUT[0]PIN_72LED1

DOUT[1]PIN_73LED2

DOUT[2]PIN_74LED3

DOUT[3]PIN_75LED4

COUTPIN_76LED5

空闲PIN_77LED6

空闲PIN_79LED7

空闲PIN_80LED8

CLK.RST.LOAD和en都接到拨码开关输入作为译码输入引脚和使能输入引脚,DOUT和COUT接到LED指示灯作为译码输出引脚,共有8个LED指示灯输出引脚,使用了其中的5个。

实验步骤:

1、4个跳线器连接在F1_SW1_JP1(1-2),F1_SW1_JP2(1-2),F1_SW1_JP3(1-2),F1_SW1_JP4(1-2)状态,这样可以使用SW1A,SW2A,SW3A,SW4A。

如果4个跳线器连接在F1_SW1_JP1(2-3),F1_SW1_JP2(2-3),F1_SW1_JP3(2-3),F1_SW1_JP4(2-3)状态,则使用按键键盘F1_KEY,F2_KEY,F3_KEY,F4_KEY进行输入。

2、EN、RST、LOAD均拨到‘1’,然后改变CLK,产生时钟,则发现计数器按照十进制功能正常计数。

3、分别改变EN、RST、LOAD的状态,依次观察计数输出结果的变化。

七、结果分析

用QuartusII自带的仿真器进行仿真,仿真结果如下图所示,符合预定设计的真值表:

实验4基于原理图输入法的三人表决电路设计

一、实验前的准备

把USB数据线一端接计算机USB接口,另一端接GX-SOPC-EP3C10-EDK开发板的USB_BLASTER接口。

开发板接上5V电源。

二、实验目的:

1.掌握输入、编译、仿真原理图文件的方法

2.掌握硬件测试的方法

三、实验设备

1.电脑,quartusii集成开发环境

2.GX_SOPC_EP3C10_EDK系统

四、实验内容与步骤:

1.三人表决电路原理

1)当表决某个提案时,共三个人进行表决,多数人同意(即两个或两个以上同意),提案通过。

三人表决电路的真值表

输入

输出

a

b

c

y

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

2)求出y的表达式

3)根据y的表达式画出三人表决器的逻辑图

2.实验步骤

1)利用QuartusII软件进行三人表决器原理图的输入、编译、仿真,直至实现其功能,并记录仿真波形

2)引脚锁定

3)编程下载并进行硬件按测试,观察并记录结果

五、实验报告

1.详细写出实验内容及步骤

2.实验心得

实验5基于原理图输入法的8位全加器的设计

一、实验目的

1、熟悉利用QuartusII的原理图输入方法设计简单组合电路。

2、掌握层次化设计的方法,并通过一个8位全加器的设计把握文本和原理图输入方式设计的详细流程。

二.实验设备:

1.电脑,quartusii集成开发环境

2.GX_SOPC_EP3C10_EDK系统

三.实验实训要求

1.使用quartusii集成开发环境分频器的设计

2.利用GX_SOPC_EP3C10_EDK系统和电脑完成实验并观察波形

三、实验原理

实验原理参考4.5节。

先设计完成一个半加器,在此基础上实现1位全加器。

一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相接。

五、实验内容

l.按照451节完成半加器和l位全加器的设计,包括用文本或原理图输入,编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设置成一个元件符号入库。

2.建立一个更高层次的原理图或文本设计,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真和硬件测试。

附图1:

半加器原理图

附图2:

将半加器、全加器电路设置成一个元件符号入库,以便在更高层次设计中调用

附图3:

建立一个更高层次的原理图设计,构成8位全加器

实验6十六进制7段数码显示译码器设计

一、实验目的

1、熟悉利用QuartusII的原理图输入方法设计简单组合电路。

2、学习7段数码显示译码器的VHDL设计和硬件验证。

二.实验设备:

1.电脑,quartusii集成开发环境

2.GX_SOPC_EP3C10_EDK系统

三.实验实训要求

1.使用quartusii集成开发环境分频器的设计

2.利用GX_SOPC_EP3C10_EDK系统和电脑完成实验并观察波形

三、实验原理

7段数码是纯组合电路。

通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的。

为了满足十六进制数的译码显示,最方便的方法就是利用VHDL译码程序在FPGA/CPLD中来实现。

首先要设计一段程序。

该程序可按照课本上例3-5的CASE语句表述方法,再根据表4-2的真值表写出程序。

设输入的4位码为A[3:

0],输出控制7段共阴数码管(图4-74)的7位数据为LED7S[6:

0]。

输出信号LED7S的7位分别接图4-74的共阴数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段g、f、e、d、c、b、a分别接1、l、0、1、1、O、1;接有高电平的段发亮,于是数码管显示“5”。

这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。

五、实验内容

l.将设计好的VHDL译码器程序在QuanusII上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

提示:

设仿真激励信号是用输入总线的方式给出输入信号仿真数据,仿真波形图如图4-73所示。

2.引脚锁定及硬件测试。

附图1:

十六进制译码器原理图

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDECL7SIS

PORT(A:

INSTD_LOGIC_VECTOR(3DOWNTO0);

LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

END;

ARCHITECTUREoneOFDECL7SIS

BEGIN

PROCESS(A)

BEGIN

CASEAIS

WHEN"0000"=>LED7S<="0111111";

WHEN"0001"=>LED7S<="0000110";

WHEN"0010"=>LED7S<="1011011";

WHEN"0011"=>LED7S<="1001111";

WHEN"0100"=>LED7S<="1100110";

WHEN"0101"=>LED7S<="1101101";

WHEN"0110"=>LED7S<="1111101";

WHEN"0111"=>LED7S<="0000111";

WHEN"1000"=>LED7S<="1111111";

WHEN"1001"=>LED7S<="1101111";

WHEN"1010"=>LED7S<="1110111";

WHEN"1011"=>LED7S<="1111100";

WHEN"1100"=>LED7S<="0111001";

WHEN"1101"=>LED7S<="1011110";

WHEN"1110"=>LED7S<="1111001";

WHEN"1111"=>LED7S<="1110001";

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

END;

实验7移位寄存器的设计

一、实验前的准备

电脑及其QuartusII8.0集成开发环境。

二、实验目的

学习利用VHDL完成实用程序的设计。

三、实验原理

实验原理参考5.6节。

四、实验内容

用VHDL设计包含串进/并出、串进/串出型的移位寄存器。

给出仿真波形和功能说明,然后硬件测试。

附:

移位寄存器VHDL程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_unsigned.ALL;

ENTITYsipoIS

PORT(CLK,d_in:

INSTD_LOGIC;--时钟和进位输入

D_OUT:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));--移位数据输出

ENDsipo;

ARCHITECTUREBEHAVOFsipoIS

SIGNALq:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'THEN

q(0)<=d_in;

foriin1to3loop

q(i)<=q(i-1);

endloop;

ENDIF;

ENDPROCESS;

d_out<=q;

ENDBEHAV;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYsisoIS

PORT(CLK,d_in:

INSTD_LOGIC;--时钟和进位输入

D_OUT:

OUTSTD_LOGIC);--移位数据输出

ENDsiso;

ARCHITECTUREBEHAVOFsisoIS

SIGNALq:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'THEN

q(0)<=d_in;

foriin1to3loop

q(i)<=q(i-1);

endloop;

ENDIF;

ENDPROCESS;

d_out<=q(3);

ENDBEHAV;

实验8交通灯的设计

一、实验目的:

掌握交通灯的设计方法

锻炼学生的查阅资料和解决问题的能力

二、实验设备:

1.电脑,quartusii集成开发环境

2.GX_SOPC_EP3C10_EDK系统

三、预习要求

查阅资料,编程实现交通灯的控制

四、实验内容与步骤:

通过查阅资料,学生用自己编写的VHDL程序设计交通灯控制器,输入、编译、仿真、编程下载、硬件测试并分析结果。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 电子设计 自动化 实验 讲义 B5

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx