FPGA交通灯实验报告.docx

FPGA交通灯实验报告.docx

- 文档编号:7760813

- 上传时间:2023-01-26

- 格式:DOCX

- 页数:17

- 大小:441.01KB

FPGA交通灯实验报告.docx

《FPGA交通灯实验报告.docx》由会员分享,可在线阅读,更多相关《FPGA交通灯实验报告.docx(17页珍藏版)》请在冰豆网上搜索。

FPGA交通灯实验报告

交通灯实验报告

一,实验目的

实现两路信号灯交替亮起,并利用两组数码管分别对两路信号进行倒计时。

两路信号时间分别为:

V:

绿灯(30S)H:

红灯(35S)

黄灯(5s)绿灯(30S)

红灯(35S)黄灯(5S)

二,实验步骤

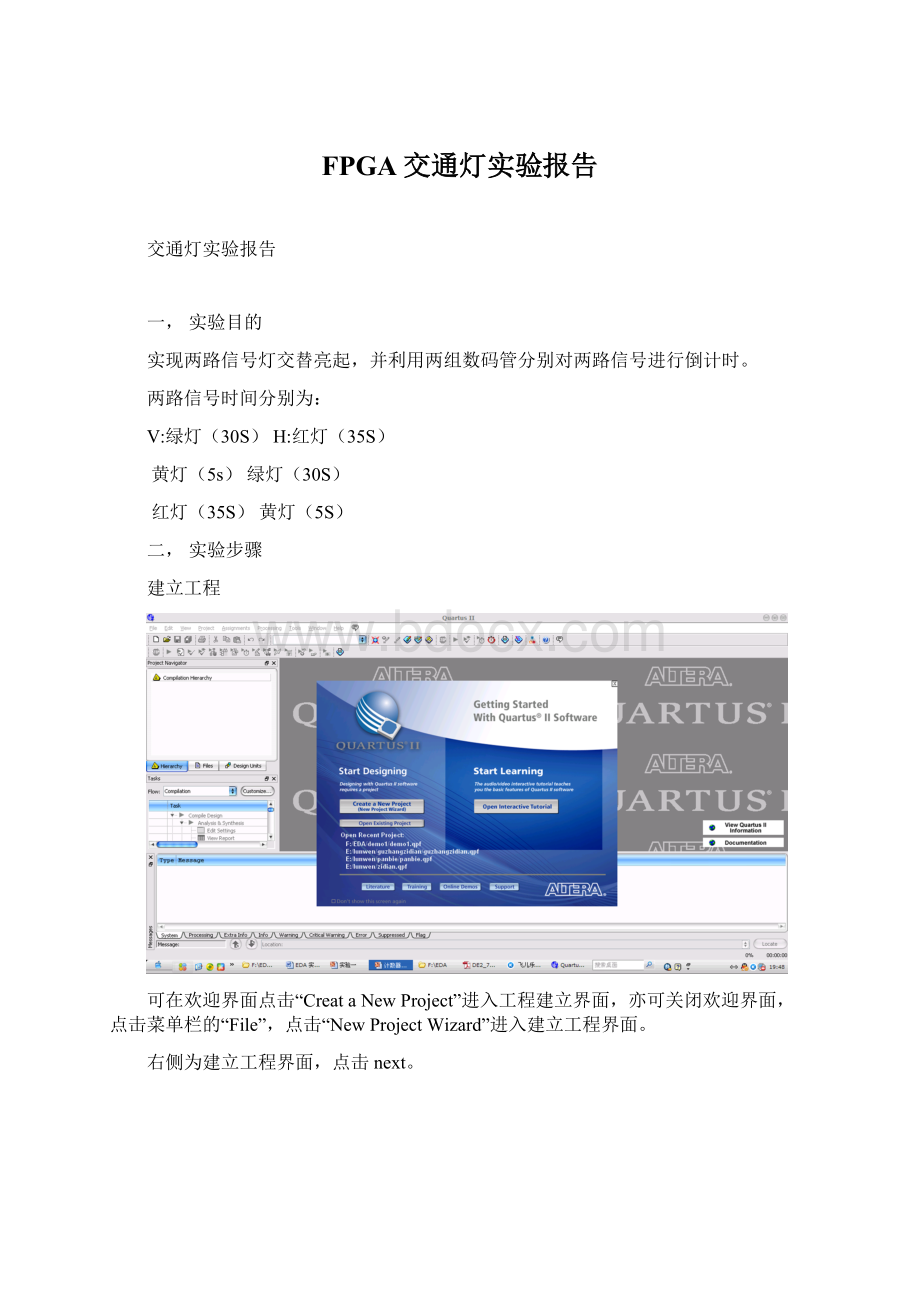

建立工程

可在欢迎界面点击“CreataNewProject”进入工程建立界面,亦可关闭欢迎界面,点击菜单栏的“File”,点击“NewProjectWizard”进入建立工程界面。

右侧为建立工程界面,点击next。

在此界面选定工程路径,取好工程名,点击“Next”。

注意:

路径中不能有中文,工程名也不能有中文。

一直点击“Next”进入器件设置界面,DE2-70开发工具采用的CycloneII系列的EP2C70F896C6N。

点击“Finish”,完成工程建立

1、点击“File”,点击“New”选择“VerilogHDL”

2,点击主界面工具栏中的选择“VerilogHDL”

3、写入verilog代码。

代码如下:

moduletraffic(Clk_50M,Rst,LedR_H,LedG_H,LedY_H,LedR_V,LedG_V,LedY_V,Seg7_VH,Seg7_VL,Seg7_HH,Seg7_HL,led15);

parameterS1=2'b00;

parameterS2=2'b01;

parameterS3=2'b10;

parameterS4=2'b11;

inputClk_50M,Rst;

outputLedR_H,LedG_H,LedY_H,LedR_V,LedG_V,LedY_V;

output[6:

0]Seg7_VH,Seg7_VL,Seg7_HH,Seg7_HL;

outputled15;

//-------------divfor1Hz-------start----

regClk_1Hz;

reg[31:

0]Cnt_1Hz;

always(posedgeClk_50MornegedgeRst)

begin

if(!

Rst)

begin

Cnt_1Hz<=1;

Clk_1Hz<=1;

end

else

begin

if(Cnt_1Hz>=25000000)

begin

Cnt_1Hz<=1;

Clk_1Hz<=~Clk_1Hz;

end

else

Cnt_1Hz<=Cnt_1Hz+1;

end

end

//-----------divfor1Hz------end-----

reg[7:

0]Cnt30,CntH,CntV,CntHH,CntVV;

reg[7:

0]CntDis,CntDiss;

//-----------30counterandseg7---start---

regLedR_H,LedG_H,LedY_H,LedR_V,LedG_V,LedY_V;

always(posedgeClk_1Hz)

begin

case(state)

S1:

begin

if(Cnt30>=30)

Cnt30<=1;

else

Cnt30<=Cnt30+1;

end

S2:

begin

if(Cnt30>=5)

Cnt30<=1;

else

Cnt30<=Cnt30+1;

end

S3:

begin

if(Cnt30>=30)

Cnt30<=1;

else

Cnt30<=Cnt30+1;

end

S4:

begin

if(Cnt30>=5)

Cnt30<=1;

else

Cnt30<=Cnt30+1;

end

endcase

end

always(posedgeClk_1Hz)

begin

case(stateV)

S1:

begin

if(CntV>=30)

CntV<=1;

else

CntV<=CntV+1;

end

S2:

begin

if(CntV>=5)

CntV<=1;

else

CntV<=CntV+1;

end

S3:

begin

if(CntV>=35)

CntV<=1;

else

CntV<=CntV+1;

end

endcase

end

always(posedgeClk_1Hz)

begin

case(stateH)

S1:

begin

if(CntH>=35)

CntH<=1;

else

CntH<=CntH+1;

end

S2:

begin

if(CntH>=30)

CntH<=1;

else

CntH<=CntH+1;

end

S3:

begin

if(CntH>=5)

CntH<=1;

else

CntH<=CntH+1;

end

endcase

end

always(negedgeClk_50MornegedgeRst)

begin

case(state)

S1:

CntVV=30-CntV;

S2:

CntVV=5-CntV;

S3:

CntVV=35-CntV;

S4:

CntVV=35-CntV;

endcase

end

always(negedgeClk_50MornegedgeRst)

begin

case(state)

S1:

CntHH=35-CntH;

S2:

CntHH=35-CntH;

S3:

CntHH=30-CntH;

S4:

CntHH=5-CntH;

endcase

end

//16进制计数器转换为用于显示的10进制计数器

always(posedgeClk_50M)

begin

if(CntVV>29)

begin

CntDis[7:

4]<=3;

CntDis[3:

0]<=CntVV-30;

end

elseif(CntVV>19)

begin

CntDis[7:

4]<=2;

CntDis[3:

0]<=CntVV-20;

end

elseif(CntVV>9)

begin

CntDis[7:

4]<=1;

CntDis[3:

0]<=CntVV-10;

end

else

CntDis<=CntVV;

end

SEG7_LUThex4(Seg7_VL,CntDis[3:

0]);

SEG7_LUThex5(Seg7_VH,CntDis[7:

4]);

always(posedgeClk_50M)

begin

if(CntHH>29)

begin

CntDiss[7:

4]<=3;

CntDiss[3:

0]<=CntHH-30;

end

elseif(CntHH>19)

begin

CntDiss[7:

4]<=2;

CntDiss[3:

0]<=CntHH-20;

end

elseif(CntHH>9)

begin

CntDiss[7:

4]<=1;

CntDiss[3:

0]<=CntHH-10;

end

else

CntDiss<=CntHH;

end

SEG7_LUThex1(Seg7_HL,CntDiss[3:

0]);

SEG7_LUThex2(Seg7_HH,CntDiss[7:

4]);

//-----------30counterandseg7----end----

reg[1:

0]state,stateH,stateV;

always(posedgeClk_1Hz)

begin

case(state)

S1:

if(Cnt30>=30)

begin

state<=S2;

end

S2:

if(Cnt30>=5)

begin

state<=S3;

end

S3:

if(Cnt30>=30)

begin

state<=S4;

end

S4:

if(Cnt30>=5)

begin

state<=S1;

end

default:

begin

state<=S1;

end

endcase

end

always(posedgeClk_1Hz)

begin

case(state)

S1:

begin

stateH<=S1;

stateV<=S1;

end

S2:

begin

stateH<=S1;

stateV<=S2;

end

S3:

begin

stateH<=S2;

stateV<=S3;

end

S4:

begin

stateH<=S3;

stateV<=S3;

end

endcase

end

always(posedgeClk_50MornegedgeRst)

begin

if(!

Rst)

begin

LedR_H<=0;

LedG_H<=0;

LedY_H<=0;

LedR_V<=0;

LedG_V<=0;

LedY_V<=0;

end

else

begin

case(state)

S1:

begin

LedR_H<=1;

LedG_H<=0;

LedY_H<=0;

LedR_V<=0;

LedG_V<=1;

LedY_V<=0;

end

S2:

begin

LedR_H<=1;

LedG_H<=0;

LedY_H<=0;

LedR_V<=0;

LedG_V<=0;

LedY_V<=1;

end

S3:

begin

LedR_H<=0;

LedG_H<=1;

LedY_H<=0;

LedR_V<=1;

LedG_V<=0;

LedY_V<=0;

end

S4:

begin

LedR_H<=0;

LedG_H<=0;

LedY_H<=1;

LedR_V<=1;

LedG_V<=0;

LedY_V<=0;

end

default:

begin

LedR_H<=0;

LedG_H<=0;

LedY_H<=0;

LedR_V<=0;

LedG_V<=0;

LedY_V<=0;

end

endcase

end

end

assignled15=state;

endmodule

moduleSEG7_LUT(oSEG,iDIG);

input[3:

0]iDIG;

output[6:

0]oSEG;

reg[6:

0]oSEG;

always(iDIG)

begin

case(iDIG)

4'h1:

oSEG=7'b1111001;//---t----

4'h2:

oSEG=7'b0100100;//||

4'h3:

oSEG=7'b0110000;//ltrt

4'h4:

oSEG=7'b0011001;//||

4'h5:

oSEG=7'b0010010;//---m----

4'h6:

oSEG=7'b0000010;//||

4'h7:

oSEG=7'b1111000;//lbrb

4'h8:

oSEG=7'b0000000;//||

4'h9:

oSEG=7'b0011000;//---b----

4'ha:

oSEG=7'b0001000;

4'hb:

oSEG=7'b0000011;

4'hc:

oSEG=7'b1000110;

4'hd:

oSEG=7'b0100001;

4'he:

oSEG=7'b0000110;

4'hf:

oSEG=7'b0001110;

4'h0:

oSEG=7'b1000000;

endcase

end

endmodule

编译工程

保存文件,将文件放在所建工程所在路径下

点击主界面工具栏中的

图标

也可点击菜单栏中“Processing”,点击“StartCompilation”

分配关键如下:

Clk_50MInputPIN_AD15

LedG_HOutputPIN_AD9

LedG_VOutputPIN_AJ6

LedR_HOutputPIN_AJ7)

LedR_VOutputPIN_AJ5)

LedY_HOutputPIN_AD8

LedY_VOutputPIN_AK5

RstInputPIN_AA23

Seg7_HH[6]OutputPIN_G1

Seg7_HH[5]OutputPIN_H3

Seg7_HH[4]OutputPIN_H2

Seg7_HH[3]OutputPIN_H1

Seg7_HH[2]OutputPIN_J2

Seg7_HH[1]OutputPIN_J1

Seg7_HH[0]OutputPIN_K3

Seg7_HL[6]OutputPIN_E4

Seg7_HL[5]OutputPIN_F4

Seg7_HL[4]OutputPIN_G4

Seg7_HL[3]OutputPIN_H8

Seg7_HL[2]OutputPIN_H7

Seg7_HL[1]OutputPIN_H4

Seg7_HL[0]OutputPIN_H6

Seg7_VH[6]OutputPIN_AD17

Seg7_VH[5]OutputPIN_AF177

Seg7_VH[4]OutputPIN_AE177

Seg7_VH[3]OutputPIN_AG16

Seg7_VH[2]OutputPIN_AF167

Seg7_VH[1]OutputPIN_AE167

Seg7_VH[0]OutputPIN_AG13

Seg7_VL[6]OutputPIN_AD12

Seg7_VL[5]OutputPIN_AD11

Seg7_VL[4]OutputPIN_AF108

Seg7_VL[3]OutputPIN_AD10

Seg7_VL[2]OutputPIN_AH98

Seg7_VL[1]OutputPIN_AF98

Seg7_VL[0]OutputPIN_AE88

烧写代码

在管脚配置完成后,还需将工程再编译一次,成功后,点击主界面工具栏中的

亦可点击主界面菜单栏中“Tools”,点击“Programmer”

进入代码烧写界面后,点击“Start”,当“Progress”为100%时,表示烧写完成,这是可观察DE2-70板现象

获得预期的效果,两组的信号红黄绿灯交替切换,计数器记为零时信号灯切换状态,红灯35s,黄灯5s,绿灯30s。

三,心得体会

通过本次实验初步了解了EDA技术,熟悉了FPGA开发板的开发流程,锻炼了动手能力。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 交通灯 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx