CD4094位移位存储总线寄存器DOC.docx

CD4094位移位存储总线寄存器DOC.docx

- 文档编号:7537808

- 上传时间:2023-01-24

- 格式:DOCX

- 页数:13

- 大小:146.36KB

CD4094位移位存储总线寄存器DOC.docx

《CD4094位移位存储总线寄存器DOC.docx》由会员分享,可在线阅读,更多相关《CD4094位移位存储总线寄存器DOC.docx(13页珍藏版)》请在冰豆网上搜索。

CD4094位移位存储总线寄存器DOC

CD4094位移位存储总线寄存器:

CD4094是带输出锁存和三态控制的串入/并出高速转换器,具有使用简单、功耗低、驱动能力强和控制灵活等优点。

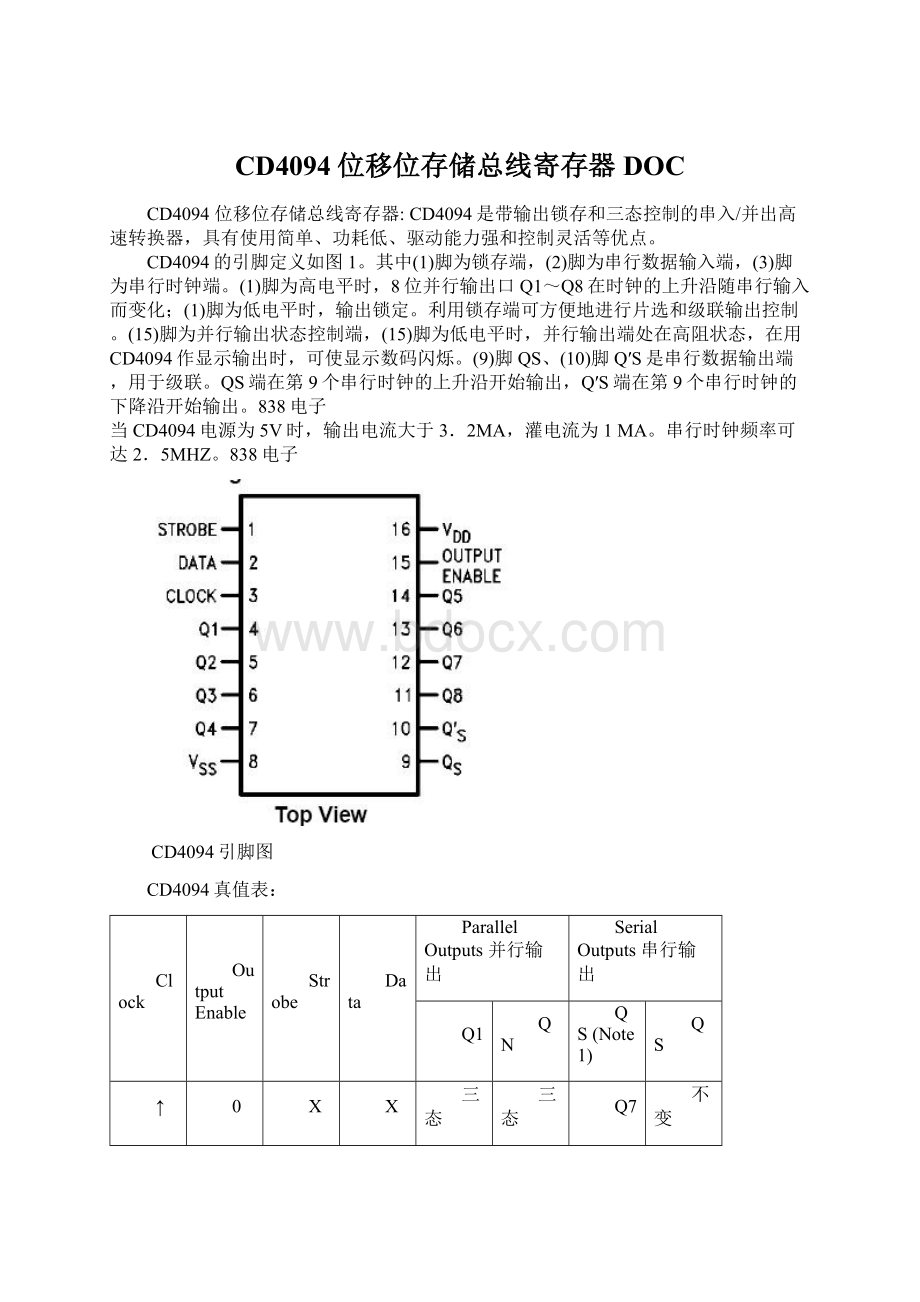

CD4094的引脚定义如图1。

其中

(1)脚为锁存端,

(2)脚为串行数据输入端,(3)脚为串行时钟端。

(1)脚为高电平时,8位并行输出口Q1~Q8在时钟的上升沿随串行输入而变化;

(1)脚为低电平时,输出锁定。

利用锁存端可方便地进行片选和级联输出控制。

(15)脚为并行输出状态控制端,(15)脚为低电平时,并行输出端处在高阻状态,在用CD4094作显示输出时,可使显示数码闪烁。

(9)脚QS、(10)脚Q′S是串行数据输出端,用于级联。

QS端在第9个串行时钟的上升沿开始输出,Q′S端在第9个串行时钟的下降沿开始输出。

838电子

当CD4094电源为5V时,输出电流大于3.2MA,灌电流为1MA。

串行时钟频率可达2.5MHZ。

838电子

CD4094引脚图

CD4094真值表:

Clock

OutputEnable

Strobe

Data

ParallelOutputs并行输出

SerialOutputs串行输出

Q1

QN

QS(Note1)

QS

↑

0

X

X

三态

三态

Q7

不变

↓

0

X

X

三态

三态

不变

Q7

↑

1

0

X

不变

不变

Q7

不变

↑

1

1

0

0

QN-1

Q7

不变

↑

1

1

1

1

QN-1

Q7

不变

↓

1

1

1

不变

不变

不变

Q7

CD4094内部电路方框图

AbsoluteMaximumRatings绝对最大额定值:

SupplyVoltage电源电压(VDD)

-0.5to+18VDC

InputVoltage输入电压(VIN)838电子

-0.5toVDD+0.5VDC

StorageTemperatureRange储存温度范围(TS)

-65℃to+150℃

PowerDissipation功耗(PD)

Dual-In-Line普通双列封装新艺图库

700mW

SmallOutline小外形封装

500mW

LeadTemperature焊接温度(TL)

Soldering,10seconds)(焊接10秒)

260℃

RecommendedOperatingConditions建议操作条件:

DCSupplyVoltage直流供电电压(VDD)

+3.0to+15VDC

InputVoltage输入电压(VIN)838电子

0toVDDVDC

OperatingTemperatureRange工作温度范围(TA)

-40℃to+85℃

DCElectricalCharacteristics直流电气特性:

Symbol符号

Parameter参数

Conditions条件

-40°C

+25°C

+85°C

Units单位

最小

最大

最小

典型

最大

最小

最大

IDD

QuiescentDeviceCurrent静态电流

VDD=5.0V

20

20

150

μA

VDD=10V

40

40

300

VDD=15V

80

80

600

VOL

LOWLevelOutputVoltage输出低电平电压

VDD=5.0V

|IO|≤1.μA

0.05

0

0.05

0.05

V

VDD=10V

0.05

0

0.05

0.05

VDD=15V

0.05

0

0.05

0.05

VOH

HIGHLevelOutputVoltage输出高电平电压

VDD=5.0V

|IO|≤1μA

4.95

4.95

5.0

4.95

V

VDD=10V

9.95

9.95

10.0

9.95

VDD=15V

14.95

14.95

15.0

14.95

VIL

LOWLevelInputVoltage输入低电平电压

VDD=5.0V,VO=0.5Vor4.5V

1.5

1.5

1.5

V

VDD=10V,VO=1.0Vor9.0V

3.0

3.0

3.0

VDD=15V,VO=1.5Vor13.5V

838电子

4.0

4.0

4.0

VIH

HIGHLevelInputVoltage输入高电平电压

VDD=5.0V,VO=0.5Vor4.5V

3.5

3.5

3.5

V

VDD=10V,VO=1.0Vor9.0V

7.0

7.0

7.0

VDD=15V,VO=1.5Vor13.5V

11.0

11.0

11.0

IOL

LOWLevelOutputCurrent输出低电平电流(Note4)

VDD=5.0V,VO=0.4V

0.52

0.44

0.88

0.36

mA

VDD=10V,VO=0.5V

1.3

1.1

2.25

0.9

VDD=15V,VO=1.5V

3.6

3.0

8.8

2.4

IOH

HIGHLevelOutputCurrent输出高电平电流(Note4)

VDD=5.0V,VO=4.6V

-0.52

-0.44

0.88

-0.36

mA

VDD=10V,VO=9.5V

-1.3

-1.1

2.25

-0.9

VDD=15V,VO=13.5V

-3.6

-3.0

8.8

-2.4

IIN

InputCurrent输入电流

VDD=15V,VIN=0V

-0.3

-0.3

-1.0

μA

VDD=15V,VIN=15V

0.3

0.3

1.0

IOZ

3-STATEOutputLeakageCurrent3态输出漏电流

VDD=15V,VIN=0Vor15V

1

1

10

μA

ACElectricalCharacteristics交流电气特性:

Symbol符号

Parameter参数838电子

Conditions条件

最小

典型

最大

Units单位

tPHL,tPLH

PropagationDelayClocktoQS

VDD=5.0V

300

600

ns

VDD=10V

125

250

VDD=15V

95

190

tPHL,tPLH

PropagationDelayClocktoQ¢S

VDD=5.0V

230

460

ns

VDD=10V

110

220

VDD=15V

75

150

ns

tPHL,tPLH

PropagationDelayClocktoParallelOut

VDD=5.0V

420

840

ns

VDD=10V

195

390

VDD=15V

135

270

tPHL,tPLH

PropagationDelayStrobetoParallelOut

VDD=5.0V

290

580

ns

VDD=10V

145

290

VDD=15V

100

200

tPHZ

PropagationDelayHIGHLeveltoHIGHImpedance

VDD=5.0V

140

280

ns

VDD=10V

75

150

VDD=15V

55

110

tPLZ

PropagationDelayLOWLeveltoHIGHImpedance

VDD=5.0V

140

280

ns

VDD=10V

75

150

VDD=15V

55

110

tPZH

PropagationDelayHIGHImpedancetoHIGHLevel

VDD=5.0V

140

280

ns

VDD=10V

75

150

VDD=15V

55

110

tPZL

PropagationDelayHIGHImpedancetoLOWLevel

VDD=5.0V

140

280

ns

VDD=10V

75

150

VDD=15V

55

110

tTHL,tTLH

TransitionTime过渡时间

VDD=5.0V

100

200

ns

VDD=10V

50

100

VDD=15V

40

80

tSU

Set-UpTimeDatatoClock建立时间数据时钟

VDD=5.0V

80

40

ns

VDD=10V

40

20

VDD=15V

20

10

tr,tf

MaximumClockRiseandFallTime最大时钟上升和下降时间

VDD=5.0V

1

ms

VDD=10V

1

VDD=15V

1

tPC

MinimumClockPulseWidth最小时钟脉冲宽度

VDD=5.0V

200

100

ns

VDD=10V

100

50

VDD=15V

83

40

tPS

MinimumStrobePulseWidth

VDD=5.0V

200

100

ns

VDD=10V

80

40

VDD=15V

70

35

fmax

MaximumClockFrequency最大时钟频率

VDD=5.0V

1.5

3.0

MHz

VDD=10V

3.0

6.0

VDD=15V

4.0

8.0

CIN

InputCapacitance输入电容

AnyInput

5.0

7.5

pF

测试电路和3态时序图

时序图

3.串入/并入-串出移位寄存器CD4014、CD4021CD4014是8位移位寄存器。

图4是其逻辑图和引脚功能图。

CD4014有一公共的时钟输入端CP、一个并入/串入控制端P/S、一个串行数据输入端DS和8个并行数据输入端P1~P8、另外还有3个输出端Q6、Q7、Q8。

表3

CP

DS

Cr

Q0

Q1

Q2

Q3

1

0

0

0

0

保持

0

0

0

Q0n

Q1n

Q2n

1

0

1

Q0n

Q1n

Q2n

表4

CP

P/S

DS

P1

Pn

Q1

Qn

1

0

0

0

0

1

1

0

1

0

1

0

1

0

1

1

1

1

1

1

0

0

0

Qn-1

0

1

1

Qn-1

Q1

Qn

表5

CP

P/S

DS

P1

Pn

Q1

Qn

1

0

0

0

0

1

0

1

0

1

1

1

0

1

0

1

1

1

1

1

0

0

0

Qn-1

0

1

1

Qn-1

0

Q1

Qn

表4是CD4014的真值表。

并行或串行输入数据,是在P/S端控制下,随时钟的上升沿同步地输入寄存器。

当P/S为“0”时,串行输入数据随时钟的上升沿同步地送入寄存器中;当P/S为“1”时,加在并行输入P1~P3的数据与时钟的上升沿同步地送入寄存器。

CD4014可以很方便地扩展位数,因此使用N个CD4014,就可将寄存器位数扩展为8×N位。

54/7402

四2输入或非门(OC)

简要说明

02为四组2输入端或非门(正逻辑),共有54/7402、54/74S02、54/74LS02三种线路结构型式,其主要电特性的典型值如下:

型号

tPLH

tphl

PD

54/7402

12ns

8ns

85mW

54/74S02

3.6ns

3.5ns

108mW

54/74LS02

10ns

10ns

11mW

引出端符号

1A-4A输入端

1B-4B输入端

1Y-4Y输出端

(注:

素材和资料部分来自网络,供参考。

请预览后才下载,期待你的好评与关注!

)

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- CD4094 位移 存储 总线 寄存器 DOC

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx