EDA程序题.docx

EDA程序题.docx

- 文档编号:7446537

- 上传时间:2023-01-24

- 格式:DOCX

- 页数:52

- 大小:198.26KB

EDA程序题.docx

《EDA程序题.docx》由会员分享,可在线阅读,更多相关《EDA程序题.docx(52页珍藏版)》请在冰豆网上搜索。

EDA程序题

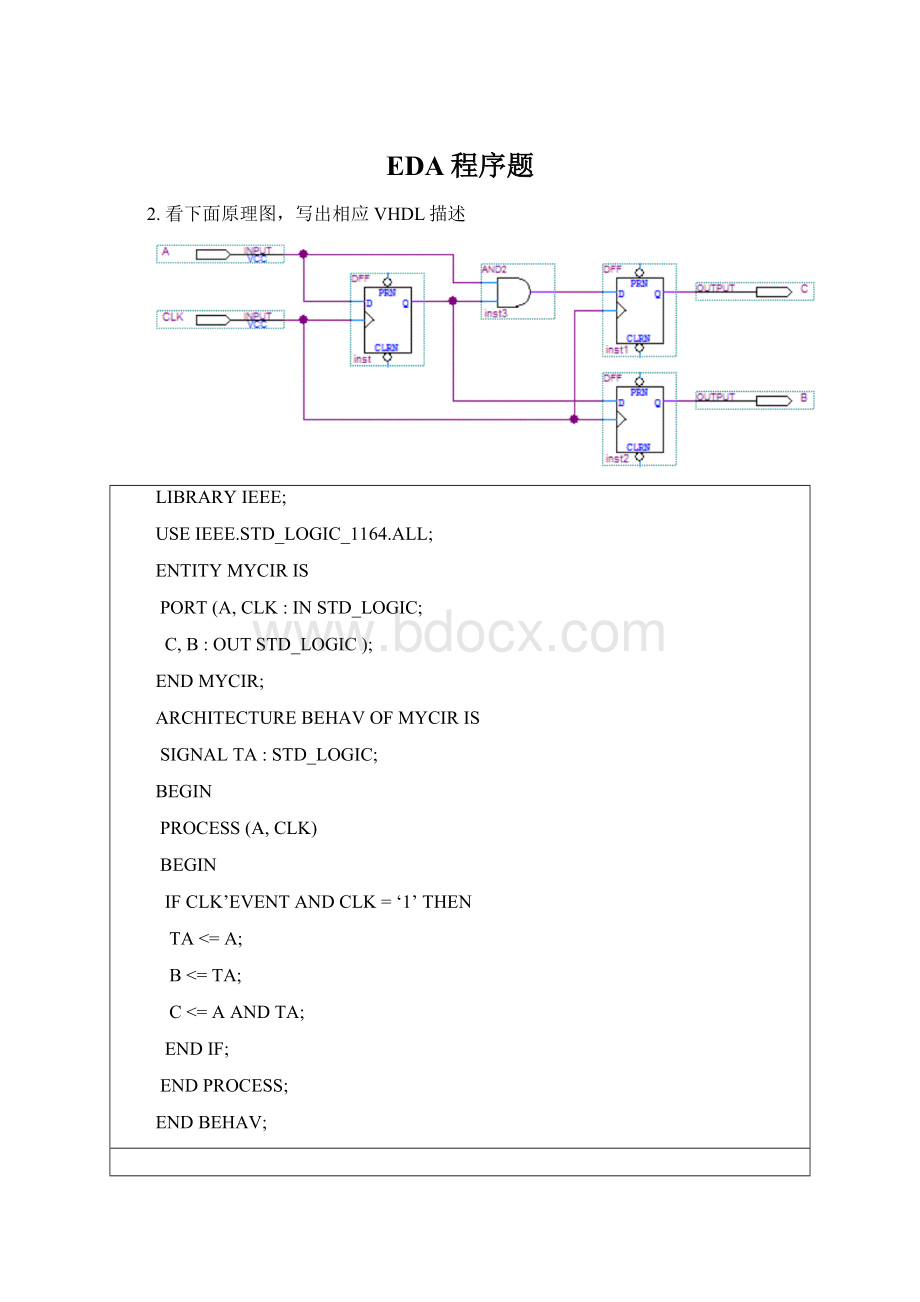

2.看下面原理图,写出相应VHDL描述

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYMYCIRIS

PORT(A,CLK:

INSTD_LOGIC;

C,B:

OUTSTD_LOGIC);

ENDMYCIR;

ARCHITECTUREBEHAVOFMYCIRIS

SIGNALTA:

STD_LOGIC;

BEGIN

PROCESS(A,CLK)

BEGIN

IFCLK’EVENTANDCLK=‘1’THEN

TA<=A;

B<=TA;

C<=AANDTA;

ENDIF;

ENDPROCESS;

ENDBEHAV;

2.看下面原理图,写出相应VHDL描述

Libraryieee;

Useieee.std_logic_1164.all;

Entitymyciris

Port(ain,bin,clk:

instd_logic;

Cout:

outstd_logic);

Endmycir;

Architectureoneofmyciris

Signaltb,tc;

begin

Process(clk)begin

Ifclk’eventandclk=‘1’then

tb<=bin;

endif;

Endprocess;

Process(clk,tc)begin

Ifclk=‘1’thencout<=tc;endif;

Endprocess;

Tc<=ainxortb;

Endone;

1.设计一个3-8译码器

输入端口:

din输入端,位宽为3位

EN译码器输出使能,高电平有效

输出端口:

xout译码器输出,低电平有效

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDECODE3_8IS

PORT(DIN:

INSTD_LOGIC_VECTOR(2DOWNTO0);

EN:

INSTD_LOGIC;

XOUT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDDECODE3_8;

ARCHITECTUREONEOFDECODE3_8IS

BEGIN

PROCESS(DIN,EN)

BEGIN

IFEN=‘1’THEN

IFDIN=“111”THENXOUT<=“11111110”;

ELSIFDIN=“110”THENXOUT<=“11111101”;

ELSIFDIN=“101”THENXOUT<=“11111011”;

ELSIFDIN=“100”THENXOUT<=“11110111”;

ELSIFDIN=“011”THENXOUT<=“11101111”;

ELSIFDIN=“010”THENXOUT<=“11011111”;

ELSIFDIN=“001”THENXOUT<=“10111111”;

ELSEXOUT<=“11111011”;

ENDIF;

ENDPROCESS;

ENDONE;

2.看下面原理图,写出相应VHDL描述

LIBARRYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYMYCIRIS

PORT(XIN,CLK:

INSTD_LOGIC;

YOUT:

OUTSTD_LOGIC);

ENDMYCIR;

ARCHITECTUREONEOFMYCIRIS

SIGNALA,B,C;

BEGIN

B<=XINORA;

PROCESS(CLK)

BEGIN

IFCLK’EVENTANDCLK=‘1’THEN

A<=C;

C<=B;

ENDIF;

ENDPROCESS;

YOUT<=C;

ENDONE;

根据原理图写出相应的VHDL程序:

(10分)

Libraryieee;

Useieee.std_logic_1164.all;

Entitymyciris

Port(A,B,clk:

instd_logic;

Qout:

outstd_logic);

Endmycir;

Architecturebehaveofmyciris

Signalta,tb,tc:

std_logic;

Begin

tc<=tanandtb;

Process(clk)

Begin

Ifclk’eventandclk=‘1’then

Ta<=A;

Tb<=B;

Endif;

Endprocess;

Process(clk,tc)

Begin

Ifclk=‘1’then

Qout<=c;

Endif;

Endprocess;

Endbehave;

已知一个简单的波形发生器的数字部分系统框图如下图所示:

图中DOWNCNT、MYROM都是在QuartusII中使用MegaWizard调用的LPM模块,其VHDL描述中Entity部分分别如下:

ENTITYDOWNCNTIS

PORT

(

clock:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(5DOWNTO0)

);

ENDDOWNCNT;

ENTITYmyromIS

PORT

(

address:

INSTD_LOGIC_VECTOR(5DOWNTO0);

q:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDmyrom;

试用VHDL描述该系统的顶层设计(使用例化语句)。

Libraryieee;

Useieee.std_logic_1164.all;

Entitymysgis

Port(clk:

instd_logic;

To_da:

outstd_logic_vector(7downto0));

Endmysq;

Architectureoneofmysqis

Signaladdr:

std_logic_vector(5downto0);

Componentlcnt

Port(clock:

instd_logic;

Q:

outstd_logic_vector(5downto0));

Endcomponent;

Componentlrom

Port(address:

instd_logic_vector(5downto0);

Q:

outstd_logic_vector(7downto0));

Endcomponent;

Begin

U1:

lcntportmap(clock=>clk,q=>addr);

U2:

lromportmap(address=>addr,q=>to_da);

Endone;

根据原理图写出相应的VHDL程序:

(15分)

Libraryieee;

Useieee.std_logic_1164.all;

Entitymyciris

Port(din,clk:

instd_logic;

Qout:

outstd_logic);

Endmycir;

Architecturebehaveofmyciris

Signala,b,c;

Begin

Qout<=cnand(axorb);

Process(clk)

Begin

Ifclk’eventandclk=‘1’then

A<=din;

B<=A;

C<=B;

Endif;

Endprocess;

Endbehave;

四、VHDL程序改错:

(10分)

仔细阅读下列程序,回答问题

1LIBRARYIEEE;

2USEIEEE.STD_LOGIC_1164.ALL;

3

4ENTITYCNT4IS

5PORT(CLK:

INSTD_LOGIC;

6Q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

7ENDCNT4;

8ARCHITECTUREbhvOFCNT4IS

9SIGNALQ1:

STD_LOGIC_VECTOR(3DOWNTO0);

10BEGIN

11PROCESS(CLK)BEGIN

12IFRISING_EDGE(CLK)begin

13IFQ1<15THEN

14Q1<=Q1+1;

15ELSE

16Q1<=(OTHERS=>'0');

17ENDIF;

18ENDIF;

19ENDPROCESS;

20Q<=Q1;

21ENDbhv;

22

1.在程序中存在两处错误,试指出,并说明理由:

12行,IF语句对应的关键字是then而非begin

14行,Q1是矢量,不能直接和整数1相加,需要使用重载函数

2.修改相应行的程序(如果是缺少语句请指出大致的行数):

错误1行号:

12程序改为:

BEGIN改为THEN

错误2行号:

3程序改为:

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

01LIBRARYIEEE;

02USEIEEE.STD_LOGIC_1164.ALL;

03USEIEEE.STD_LOGIC_UNSIGNED.ALL;

04ENTITYLED7CNTIS

05PORT(CLR:

INSTD_LOGIC;

06CLK:

INSTD_LOGIC;

07LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

08ENDLED7CNT;

09ARCHITECTUREoneOFLED7CNTIS

10SIGNALTMP:

STD_LOGIC_VECTOR(3DOWNTO0);

11BEGIN

12CNT:

PROCESS(CLR,CLK)

13BEGIN

14IFCLR='1'THEN

15TMP<=0;

16ELSEIFCLK'EVENTANDCLK='1'THEN

17TMP<=TMP+1;

18ENDIF;

19ENDPROCESS;

20OUTLED:

PROCESS(TMP)

21BEGIN

22CASETMPIS

23WHEN"0000"=>LED7S<="0111111";

24WHEN"0001"=>LED7S<="0000110";

25WHEN"0010"=>LED7S<="1011011";

26WHEN"0011"=>LED7S<="1001111";

27WHEN"0100"=>LED7S<="1100110";

28WHEN"0101"=>LED7S<="1101101";

29WHEN"0110"=>LED7S<="1111101";

30WHEN"0111"=>LED7S<="0000111";

31WHEN"1000"=>LED7S<="1111111";

32WHEN"1001"=>LED7S<="1101111";

33WHENOTHERS=>LED7S<=(OTHERS=>'0');

34ENDCASE;

35ENDPROCESS;

36ENDone;

在程序中存在两处错误,试指出,并说明理由:

第15行,错误:

整数0不能直接赋值给TMP矢量;改正:

TMP<=(OTHERS=>‘0’);

第16行,错误:

ELSEIF缺少一条对应的ENDIF语句;改正:

将ELSEIF改为关键字ELSIF

1LIBRARYIEEE;

2USEIEEE.STD_LOGIC_1164.ALL;

3

4ENTITYCNT10IS

5PORT(CLK:

INSTD_LOGIC;

6Q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

7ENDCNT10;

8ARCHITECTUREbhvOFCNT10IS

9SIGNALQ1:

STD_LOGIC_VECTOR(3DOWNTO0);

10BEGIN

11PROCESS(CLK)BEGIN

12IFRISING_EDGE(CLK)begin

13IFQ1<9THEN

14Q1<=Q1+1;

15ELSE

16Q1<=(OTHERS=>'0');

17ENDIF;

18ENDIF;

19ENDPROCESS;

20Q<=Q1;

21ENDbhv;

指出并修改相应行的程序(如果是缺少语句请指出大致的行数):

错误1行号:

12程序改为:

IFRISING_EDGE(CLK)THEN

错误2行号:

3程序改为:

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

12行if语句配套关键字是then而非begin

3行程序中使用了+号重载函数,应包含使用对应程序包ieee.std_logic_unsigned.all

2.若编译时出现如下错误,请分析原因。

当前编译的程序文件没有放在指定文件夹内,所以系统找不到WORK工作库。

下面程序是一个10线-4线优先编码器的VHDL描述,试补充完整。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYcoderIS

PORT(din:

INSTD_LOGIC_VECTOR(9DOWNTO0);

output:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDcoder;

ARCHITECTUREbehavOFCODERIS

SIGNALSIN:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(DIN)

BEGIN

IF(din(9)='0')THENSIN<="1001";

ELSIF(din(8)=’0’)THENSIN<="1000";

ELSIF(din(7)='0')THENSIN<="0111";

ELSIF(din(6)='0')THENSIN<="0110";

ELSIF(din(5)='0')THENSIN<="0101";

ELSIF(din(4)='0')THENSIN<="0100";

ELSIF(din(3)='0')THENSIN<="0011";

ELSIF(din

(2)='0')THENSIN<="0010";

ELSIF(din

(1)='0')THENSIN<="0001";

ELSESIN<=“0000”;

ENDIF;

ENDPROCESS;

Output<=sin;

ENDbehav;

LIBRARYIEEE;--8位分频器程序设计

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYPULSEIS

PORT(CLK:

INSTD_LOGIC;

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

FOUT:

OUTSTD_LOGIC);

END;

ARCHITECTUREoneOFPULSEIS

SIGNALFULL:

STD_LOGIC;

BEGIN

P_REG:

PROCESS(CLK)

VARIABLECNT8:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

IFCLK’EVENTANDCLK=‘1’THEN

IFCNT8="11111111"THEN

CNT8:

=D;--当CNT8计数计满时,输入数据D被同步预置给计数器CNT8

FULL<='1';--同时使溢出标志信号FULL输出为高电平

ELSECNT8:

=CNT8+1;--否则继续作加1计数

FULL<='0';--且输出溢出标志信号FULL为低电平

ENDIF;

ENDIF;

ENDPROCESSP_REG;

P_DIV:

PROCESS(FULL)

VARIABLECNT2:

STD_LOGIC;

BEGIN

IFFULL'EVENTANDFULL='1'THEN

CNT2<=NOTCNT2;--如果溢出标志信号FULL为高电平,D触发器输出取反

IFCNT2='1'THENFOUT<='1';

ELSEFOUT<='0';

ENDIF;

ENDIF;

ENDPROCESSP_DIV;

END;

下面程序是参数可定制带计数使能异步复位计数器的VHDL描述,试补充完整。

libraryieee;

useIEEE.std_logic_1164.all;

useIEEE.std_logic_unsigned.all;

useIEEE.std_logic_arith.all;

entitycounter_nis

generic(width:

integer:

=8);

port(data:

instd_logic_vector(width-1downto0);

load,en,clk,rst:

instd_logic;

q:

outstd_logic_vector(width-1downto0));

endcounter_n;

architecturebehaveofcounteris

signalcount:

std_logic_vector(width-1downto0);

begin

process(clk,rst)

begin

ifrst='1'then

count<=(others=>‘0’);――清零

elsifclk’eventandclk=‘1’then――边沿检测

ifload='1'then

count<=data;

elsifen='1'then

count<=count+1;

endif;

endif;

endprocess;

q<=count;

endbehave;

阅读下列VHDL程序,画出相应原理图(3道题)

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYTRISIS

PORT(CONTROL:

INSTD_LOGIC;

INN:

INSTD_LOGIC;

Q:

INOUTSTD_LOGIC;

Y:

OUTSTD_LOGIC);

ENDTRIS;

ARCHITECTUREONEOFTRISIS

BEGIN

PROCESS(CONTROL,INN,Q)

BEGIN

IF(CONTROL='0')THEN

Y<=Q;

Q<='Z';

ELSE

Q<=INN;

Y<='Z';

ENDIF;

ENDPROCESS;

ENDONE;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYthreeIS

PORT

(

clk,d:

INSTD_LOGIC;

dout:

OUTSTD_LOGIC);

END;

ARCHITECTUREbhvOFthreeIS

SIGNALtmp:

STD_LOGIC;

BEGIN

P1:

PROCESS(clk)

BEGIN

IFrising_edge(clk)THEN

Tmp<=d;

dout<=tmp;

ENDIF;

ENDPROCESSP1;

ENDbhv;

libraryieee;

useieee.std_logic_1164.all;

entitylfsris

port(clk:

instd_logic;

clr:

instd_logic;

d:

instd_logic;

mout:

outstd_logic);

endlfsr;

architecturertloflfsris

signalsreg:

std_logic;

begin

shift_p:

process(clk,clr)

variables:

std_logic;

begin

ifclr='1'thens:

=’0’;

elsifrising_edge(clk)then

s:

=sregxor(notd);

endif;

sreg<=s;

endprocess;

mout<=

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 程序

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx