计算机组成原理实验报告.docx

计算机组成原理实验报告.docx

- 文档编号:7418829

- 上传时间:2023-01-23

- 格式:DOCX

- 页数:20

- 大小:209.99KB

计算机组成原理实验报告.docx

《计算机组成原理实验报告.docx》由会员分享,可在线阅读,更多相关《计算机组成原理实验报告.docx(20页珍藏版)》请在冰豆网上搜索。

计算机组成原理实验报告

实验1通用寄存器实验

一、实验目的

1.熟悉通用寄存器的数据通路。

2.了解通用寄存器的构成和运用。

二、实验要求

掌握通用寄存器R3~R0的读写操作。

三、实验原理

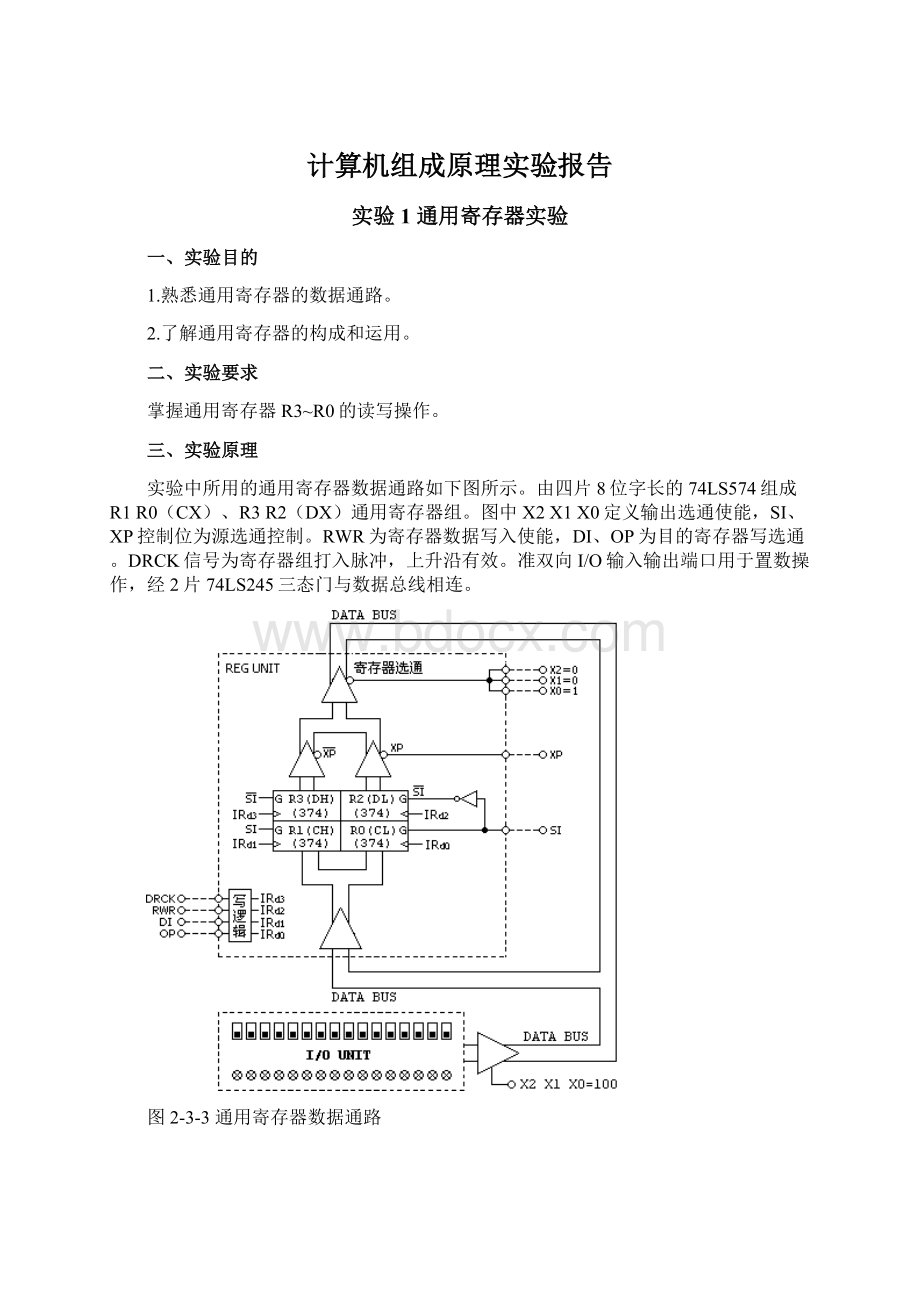

实验中所用的通用寄存器数据通路如下图所示。

由四片8位字长的74LS574组成R1R0(CX)、R3R2(DX)通用寄存器组。

图中X2X1X0定义输出选通使能,SI、XP控制位为源选通控制。

RWR为寄存器数据写入使能,DI、OP为目的寄存器写选通。

DRCK信号为寄存器组打入脉冲,上升沿有效。

准双向I/O输入输出端口用于置数操作,经2片74LS245三态门与数据总线相连。

图2-3-3通用寄存器数据通路

四、实验内容

1.实验连线

K23~K0置“1”,灭M23~M0控位显示灯。

然后按下表要求“搭接”部件控制电路。

连线

信号孔

接入孔

作用

有效电平

1

DRCK

CLOCK

单元手动实验状态的时钟来源

上升沿打入

2

X2

K10(M10)

源部件译码输入端X2

三八译码

八中选一

低电平有效

3

X1

K9(M9)

源部件译码输入端X1

4

X0

K8(M8)

源部件译码输入端X0

5

XP

K7(M7)

源部件奇偶标志:

0=偶寻址,1=奇寻址

6

SI

K20(M20)

源寄存器地址:

0=CX,1=DX

7

RWR

K18(M18)

通用寄存器写使能

低电平有效

8

DI

K17(M17)

目标寄存器地址:

0=CX,1=DX

9

OP

K16(M16)

目标部件奇偶标志:

0=偶寻址,1=奇寻址

2.寄存器的读写操作

1目的通路

当RWR=0时,由DI、OP编码产生目的寄存器地址,详见下表。

通用寄存器“手动/搭接”目的编码

目标使能

通用寄存器目的编址

功能说明

RW(K18)

DI(K17)

OP(K16)

T

0

0

0

↑

R0写

0

0

1

↑

R1写

0

1

0

↑

R2写

0

1

1

↑

R3写

2通用寄存器的写入

通过“I/O输入输出单元”向R0、R1寄存器分别置数11h、22h,操作步骤如下:

通过“I/O输入输出单元”向R2、R3寄存器分别置数33h、44h,操作步骤如下:

3源通路

当X2~X0=001时,由SI、XP编码产生源寄存器,详见下表。

通用寄存器“手动/搭接”源编码

源使能

通用寄存器源编址

功能说明

K10

K9

K8

K20

K7

X2

X1

X0

SI

XP

0

0

1

0

0

R0送总线

0

1

R1送总线

1

0

R2送总线

1

1

R3送总线

4通用寄存器的读出

关闭写使能,令K18(RWR)=1,按下流程分别读R0、R1、R2、R3。

五、实验心得

通过这个实验让我清晰的了解了通用寄存器的构成以及通用寄存器是如何运用的,并且熟悉了通用寄存器的数据通路,而且还深刻的掌握了通用寄存器R3~R0的读写操作。

实验2运算器实验

一、实验目的

掌握八位运算器的数据传输格式,验证运算功能发生器及进位控制的组合功能。

二、实验要求

完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运用。

三、实验原理

实验中所用的运算器数据通路如图2-3-1所示。

ALU运算器由CPLD描述。

运算器的输出FUN经过74LS245三态门与数据总线相连,运算源寄存器A和暂存器B的数据输入端分别由2个74LS574锁存器锁存,锁存器的输入端与数据总线相连,准双向I/O输入输出端口用来给出参与运算的数据,经2片74LS245三态门与数据总线相连。

图2-3-1 运算器数据通路

图中AWR、BWR在“搭接态”由实验连接对应的二进制开关控制,“0”有效,通过【单拍】按钮产生的脉冲把总线上的数据打入,实现运算源寄存器A、暂存器B的写入操作。

四、实验内容

1.运算器功能编码

表2.3.1ALU运算器编码表

算术运算

逻辑运算

K15

K13

K12

K11

功能

K15

K13

K12

K11

功能

M

S2

S1

S0

M

S2

S1

S0

0

0

0

0

A+B+C

1

0

0

0

B

0

0

0

1

A—B—C

1

0

0

1

/A

0

0

1

0

RLC

1

0

1

0

A-1

0

0

1

1

RRC

1

0

1

1

A=0

0

1

0

0

A+B

1

1

0

0

A#B

0

1

0

1

A—B

1

1

0

1

A&B

0

1

1

0

RL

1

1

1

0

A+1

0

1

1

1

RR

1

1

1

1

A

2.实验连线

K23~K0置“1”,灭M23~M0控位显示灯。

然后按下表要求“搭接”部件控制电路。

表2.3.2运算实验电路搭接表

连线

信号孔

接入孔

作用

有效电平

1

DRCK

CLOCK

单元手动实验状态的时钟源

上升沿打入

2

X2

K10(M10)

源部件译码输入端X2

三八译码

八中选一

低电平有效

3

X1

K9(M9)

源部件译码输入端X1

4

X0

K8(M8)

源部件译码输入端X0

5

XP

K7(M7)

源部件奇偶标志:

0=偶寻址,1=奇寻址

6

M

K15(M15)

运算控制位:

0=算术运算,1=逻辑运算

7

S2

K13(M13)

运算状态位S2

8

S1

K12(M12)

运算状态位S1

9

S0

K11(M11)

运算状态位S0

10

AWR

K17(M17)

A运算源寄存器写使能

低电平有效

11

BWR

K18(M18)

B运算源暂存器写使能

低电平有效

示例1算术运算

1.运算源寄存器写流程

通过I/O单元“S7~S0”开关向累加器A和暂存器B置数,具体操作步骤如下:

2.运算源寄存器读流程

关闭A、B写使能,令K18=K17=“1”,按下流程分别读A、B。

3.加法与减法运算

令MS2S1S0(K15K13~K11=0100),为算术加,FUN及总线单元显示A+B的结果

令MS2S1S0(K15K13~K11=0101),为算术减,FUN及总线单元显示A-B的结果。

示例2 逻辑运算

1.运算源寄存器写流程

通过“I/O输入输出单元”开关向寄存器A和B置数,具体操作步骤如下:

2.运算源寄存器读流程

关闭A、B写使能,令K17=K18=1,按下流程分别读A、B。

1若运算控制位设为(MS2S1S0=1111)则F=A,即A内容送到数据总线。

2若运算控制位设为(MS2S1S0=1000)则F=B,即B内容送到数据总线。

3.逻辑运算

令MS2S1S0(K15K13~K11=1101),为逻辑与,FUN及总线显示A逻辑与B的结果。

令MS2S1S0(K15K13~K11=1100),为逻辑或,FUN及总线显示A逻辑或B的结果。

示例3移位运算

(1)A寄存器置数

拨动“I/O输入输出单元”开关向移位源寄存器A置数,具体操作步骤如下:

(2)A寄存器移位流程

完成上流程的操作后,按表2.3.3改变K13、K11的状态,再按动【单拍】钮,观察A的变化。

1当K13K11=11,每按一次【单拍】钮,A右移一位。

2当K13K11=10,每按一次【单拍】钮,A左移一位。

3当K13K11=01,每按一次【单拍】钮,A带进位右移一位。

4当K13K11=00,每按一次【单拍】钮,A带进位左移一位。

实验思考:

验证表2.3.1ALU运算器编码表所列的运算功能。

在给定A=55h、B=77h的情况下,K23~K0置“1”,改变运算器的功能设置位MS2S1S0(K15K13~K11),观察运算器的输出,填入下页表格中,并和理论分析进行比较、验证。

表2.3.4 ALU运算器真值表

运算控制

运算表达式

K15

K13

K12

K11

A

B

运算结果

M

S2

S1

S0

带进位算术加

A+B+C

0

0

0

0

55

77

FUN=(CC)

带借位算术减

A-B-C

0

0

0

1

55

77

FUN=(DE)

带进位左移

RLCA

0

0

1

0

55

77

FUN=(AA)

带进位右移

RRCA

0

0

1

1

FUN=(2A)

算术加

A+B

0

1

0

0

FUN=(CC)

算术减

A-B

0

1

0

1

FUN=(DE)

左移

RLA

0

1

1

0

FUN=(AA)

右移

RRA

0

1

1

1

FUN=(AA)

取B值

B

1

0

0

0

55

77

FUN=(77)

A取反

NOTA

1

0

0

1

55

77

FUN=(AA)

A减1

A-1

1

0

1

0

55

77

FUN=(54)

清零

0

1

0

1

1

FUN=(00)

逻辑或

AORB

1

1

0

0

FUN=(77)

逻辑与

AANDB

1

1

0

1

FUN=(55)

A加1

A+1

1

1

1

0

FUN=(56)

取A值

A

1

1

1

1

FUN=(55)

五、实验心得

这个实现让我掌握了八位运算器的数据传输格式,并且验证运算功能发生器及进位控制的组合功能,顺利的完成了算术、逻辑、移位运算的实验,熟悉了ALU运算控制位的运用。

实验3准双向I/O口实验

一、实验目的

熟悉与了解准双向I/O口的构成原理。

二、实验要求

掌握准双向I/O口的输入/输出特性的运用。

三、实验原理

Dais-CMX08+向用户提供的是按准双向原理设计的十六位输入/输出I/O口,当该位为“1”时才能用作输入源,上电或复位(手动态按【返回】键),该十六位I/O口被置位(即为“0FFFFh”)。

通常情况下,在用作输入的时候就不能再有输出定义。

电路结构如图2-3-4所示。

该口外接十六位二进制数据开关,适用于外部数据的输入,该口跨接十六个发光二极管和经缓冲驱动的四个七段显示,能以二进制和十六进制两种方式显示I/O口的输入输出状态。

发光管在高电平“1”时发光点亮。

图2-3-4准双向I/O电路

实验中所用的I/O口数据通路如图2-3-5所示。

I/O的输入经2片74LS245缓冲与数据总线相连,I/O口的输出由2片74LS574锁存后输出,锁存器的输入端与数据总线相连。

图2-3-5十六位I/O的数据通路

四、实验内容

1.实验连线

K23~K0置“1”,灭M23~M0控位显示灯。

然后按下表要求“搭接”部件控制电路。

连线

信号孔

接入孔

作用

有效电平

1

IOCK

CLOCK

单元手动实验状态的时钟来源

上升沿打入

2

X2

K10(M10)

源部件译码输入端X2

三八译码

八中选一

低电平有效

3

X1

K9(M9)

源部件译码输入端X1

4

X0

K8(M8)

源部件译码输入端X0

5

XP

K7(M7)

源部件奇偶标志:

0=偶寻址,1=奇寻址

6

IOW

K17(M17)

I/O输出使能,本例定义到M17位

低电平有效

7

OP

K16(M16)

目标部件奇偶标志:

0=偶寻址,1=奇寻址

2.搭接方式I/O的寻址定义

I/O口源编址

I/O口目的编址

源编码

I/O编址

注释

目的I/O编址

注释

K10

K9

K8

K7

K17

K16

X2

X1

X0

XP

IOW

OP

1

0

0

0

S7~S0读

0

0

S7~S0写

1

S15~S8读

1

S15~S0写

3.I/O口奇送偶(S15~S8送S7~S0)

4.I/O口偶送奇(S7~S0送S15~S8)

五、实验心得

通过这个实现让我彻底的掌握了准双向I/O口的输入/输出特性的运用,并且熟悉与了解了准双向I/O口的构成原理。

实验4地址总线组成实验

一、实验目旳

1.熟悉和了解地址总线的组成结构、地址来源及集合原理。

2.掌握程序段与数据段的寻址规则及地址部件的运用技巧。

二、实验要求

通过地址形成部件实验,建立“段”概念,学会“段”运用。

三、实验原理

地址总线的作用是传递地址信息,输出当前数据总线上发送信息的源地址或接收信息的目的地址。

如下图所示本系统设有程序与数据两条地址总线,通过PC计数器提供程序存储器地址,并由地址寄存器AR传递数据存储器地址及外设地址,通过指令总线送AR形成指令定义的内存地址。

图2-3-6 地址总线组成通路

1.8位内存地址Addr

如图2-3-6所示,本系统从提高信息存取效率的角度设计存储器地址通路,按现代计算机体系结构中最为典型的分段存取理念合成存储器地址总线addr,在指令操作“时段”(取操作码与取操作数),以当前程序指针PC为址;遇数据与内存传递“时段”,以当前数据指针AR为址。

addr地址的合成通路见图2-3-6。

其寻址范围为0~0FFh。

2.8位外设地址Address

如图2-3-6所示,本系统外设地址总线Address由地址锁存器AR直接提供,在P4页图1-5-1所示的XRD、XWR、ALE等外设控制信号的管理下,通过外DBUG数据总线完成外设信息由内到外或由外到内的传递。

其寻址范围为0~0FF,可达256字节。

四、实验内容

1.程序计数器实验

图2-3-7所示的PC指针由2片161组成八位程序计数器,计数器的输入端与总线相连构成PC装载通路,计数器的输出端途经三态门缓冲分离为两条通路,其一与总线相连构成程序指针访问通路,其二与地址寄存器AR集合组成存储器地址总线。

它的清零端由中央外理器单元直控,上电时PC计数器自动清零,在手动实验中,按【返回】键亦可实现计数器的强制清零。

手控“搭接”状态,本实验由下表定义PC计数器的预置与加1操作,实验中以准双向I/O部件的S7~S0为计数器预置源。

当IP=0时按单拍按钮,遇E/M=“0”,在脉冲下降沿把S7~S0的内容装入PC计数器;遇E/M=“1”,在脉冲下降沿完成PC计数器加1操作。

目标部件定义

节拍

功能说明

K23

K22

T

上升沿打入

E/M

LDPC

X

1

X

PC保持

1

0

↑

PC加1

0

0

↑

PC装载

说明:

“↑”表示上升沿有效

PC读出由P8页表2.2源编码表定义,在X2~X0(K10~K8=000)时,当前PC送总线。

2.实验连线

K23~K0置“1”,灭M23~M0控位显示灯。

然后按下表要求“搭接”部件控制电路。

连线

信号孔

接入孔

作用

有效电平

1

DRCK

CLOCK

单元手动实验状态的时钟来源

上升沿打入

2

X2

K10(M10)

源部件译码输入端X2

三八译码

八中选一

低电平有效

3

X1

K9(M9)

源部件译码输入端X1

4

X0

K8(M8)

源部件译码输入端X0

5

XP

K7(M7)

源部件奇偶标志:

0=偶寻址,1=奇寻址

6

LDAR

K19(M19)

数据存储器地址指针,本例定义K19

7

LDPC

K22(M22)

PC程序计数器更新位,本例定义到K22

低电平有效

8

E/M

K23(M23)

当IP有效时,E/M:

0=PC装载,1=PC加1

2)程序计数器PC的写入、读出与加1

通过“I/O单元”开关向程序计数器PC置数,按【单拍】按钮完成PC指针的装载;然后K23、K22置“1”,令K10~K8为“0”,执行PC读操作。

再令K23K22=“10”,实现PC+1

保持PC+1状态,按【单拍】按钮,在CLOCK的上升沿PC加1并送数据总线,程序计数器和总线单元显示12h。

继续按【单拍】按钮,观察PC与总线内容的变化。

3、地址寄存器实验

图2-3-7所示的AR由1片74LS574锁存器构成八位数据指针,锁存器的输入端与总线相连构成置数通路,锁存器的输出端途经三态门缓冲分离与PC计数器集合组成存储器地址总线及外设总线。

由中央外理器单元控制锁存器的清零,在手动实验中,按【返回】键即可实现AR锁存器的强制清零。

1)地址寄存器AR打入

在手控“搭接”态,数据指针AR由LDAR及DRCK(CLOCK脉冲)二信号组合控制地址的装入操作。

本实验以总线上准双向I/O部件的S7~S0为置数源。

当K19=0时,按【单拍】钮,在脉冲下降沿把S7~S0的内容装入地址锁存器AR。

操作步骤如下:

五、实验心得

本次实现我熟悉和了解了地址总线的组成结构、地址来源及集合原理,学习到了程序段与数据段的寻址规则以及地址部件的运用技巧,通过地址如何形成部件实验,建立“段”概念,学会“段”运用。

实验5存储器读写实验

一、实验目的

熟悉和了解存储器组织与总线组成的数据通路。

二、实验要求

按照实验步骤完成实验项目,掌握存储部件在原理计算机中的运用。

三、实验原理

存储器是计算机的存储部件,用于存放程序和数据。

存储器是计算机信息存储的核心,是计算机必不可少的部件之一,计算机就是按存放在存储器中的程序自动有序不间断地进行工作。

本系统从提高存储器存储信息效率的角度设计数据通路,按现代计算机中最为典型的分段存储理念把存储器组织划分为程序段、数据段、内存或堆栈段,由此派生了数据总线(DBus)、指令总线(IBus)、微总线(μBus)等与现代计算机设计规范相吻合的实验环境。

实验所用的存储器电路原理如图2-3-8所示,该存储器组织由一片6116构成具有段概念的信息存储体系,该存储体系Addr由IP指针和AR指针分时提供,E/M控位为“1”时选通IP,反之选通AR。

该存储器可动态变更程序源与数据源,把我们的教学实验提高到能与现代计算机设计规范相匹配与接轨的层面。

图2-3-8存储器数据通路

四、实验内容

1.实验连线

K23~K0置“1”,灭M23~M0控位显示灯。

然后按下表要求“搭接”部件控制电路。

连线

信号孔

接入孔

作用

有效电平

1

MOCK

CLOCK

单元手动实验状态的时钟来源

上升沿打入

2

X2

K10(M10)

源部件译码输入端X2

三八译码

八中选一

低电平有效

3

X1

K9(M9)

源部件译码输入端X1

4

X0

K8(M8)

源部件译码输入端X0

5

XP

K7(M7)

I/O部件奇偶标志:

0=偶寻址,1=奇寻址

6

E/M

K23(M23)

Addr地址段定义:

0=AR指针,1=PC指针

7

MWR

K21(M21)

存储器写使能:

0=存储器写,1=存储器读

8

LDAR

K19(M19)

AR地址寄存器写使能

低电平有效

9

LDPC

K22(M22)

PC装载与PC+1

低电平有效

2.存储器数据段读写操作

(1)数据段写操作

按下流程从0址单元开始,向数据段00h~05h单元依次写入112233445566。

(2)数据段读操作

依次读出数据段00~05h单元的内容,这里以0址单元读出为例阐述操作流程。

执行上述流程总线单元应显示11h,若正确可按上述流程读出01h~05h单元的内容。

3.存储器程序段读写操作

(1)程序段写操作

1PC装载写操作流程:

2PC+1写操作流程:

重复PC+1写流程,分别对02~04写入234567。

(2)程序段读操作

PC装载及PC+1读操作流程

完成上流程,PC=01,总线单元显示AA,此时每按一次【单拍】按钮,PC+1,总线单元依次显示234567……等内容。

4.程序与数据存储器的分段读出

1分段读出流程

由上流程可知存储器组织0地址的内容有两个,其中55为程序段内容,11为数据段内容。

五、实验心得

这次实验让我熟悉和了解了存储器组织与总线组成的数据通路,并且按照实验步骤完成了实验项目,掌握存储部件在原理计算机中的运用。

通过这几次实验也让我知道了合作的重要性,没有团队的合作,我也不可能那么顺利的完成所有实验。

温馨提示:

最好仔细阅读后才下载使用,万分感谢!

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 计算机 组成 原理 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx