第七章 复和系统时钟.docx

第七章 复和系统时钟.docx

- 文档编号:7415131

- 上传时间:2023-01-23

- 格式:DOCX

- 页数:29

- 大小:149.89KB

第七章 复和系统时钟.docx

《第七章 复和系统时钟.docx》由会员分享,可在线阅读,更多相关《第七章 复和系统时钟.docx(29页珍藏版)》请在冰豆网上搜索。

第七章复和系统时钟

第七章复位和系统时钟

7.1复位

复位,是系统开始正常运转前的一个必经过程,复位部分设计的好坏,关系体统的稳定。

STM32F10xxx支持三种复位形式,分别为系统复位、上电复位和备份区域复位。

7.1.1系统复位

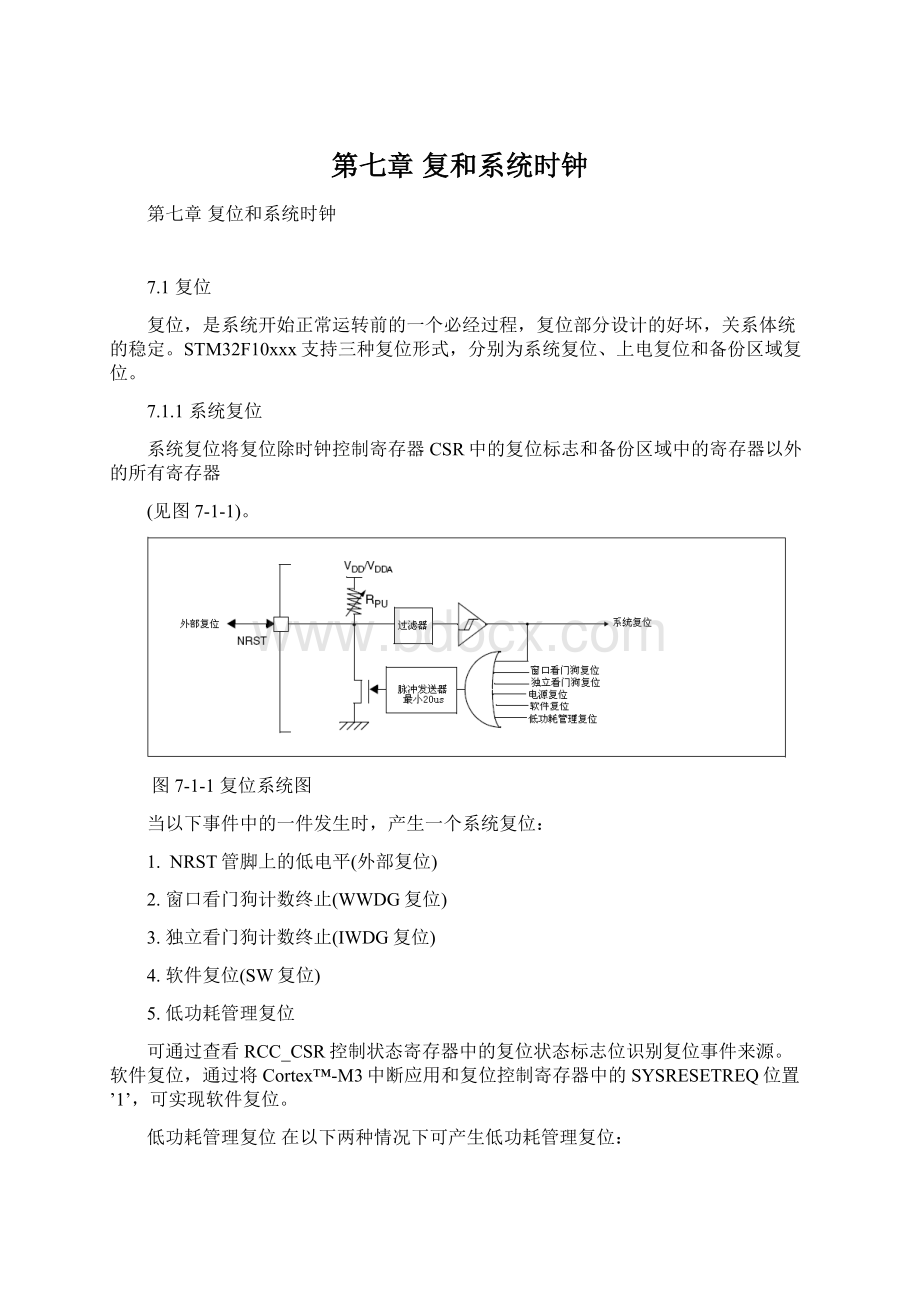

系统复位将复位除时钟控制寄存器CSR中的复位标志和备份区域中的寄存器以外的所有寄存器

(见图7-1-1)。

图7-1-1复位系统图

当以下事件中的一件发生时,产生一个系统复位:

1.NRST管脚上的低电平(外部复位)

2.窗口看门狗计数终止(WWDG复位)

3.独立看门狗计数终止(IWDG复位)

4.软件复位(SW复位)

5.低功耗管理复位

可通过查看RCC_CSR控制状态寄存器中的复位状态标志位识别复位事件来源。

软件复位,通过将Cortex™-M3中断应用和复位控制寄存器中的SYSRESETREQ位置’1’,可实现软件复位。

低功耗管理复位在以下两种情况下可产生低功耗管理复位:

1.在进入待机模式时产生低功耗管理复位:

通过将用户选择字节中的nRST_STDBY位置’1’将使能该复位。

这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式。

2.在进入停止模式时产生低功耗管理复位:

通过将用户选择字节中的nRST_STOP位置’1’将使能该复位。

这时,即使执行了进入停机模式的过程,系统将被复位而不是进入停机模式。

7.1.2电源复位

当以下事件中之一发生时,产生电源复位:

1.上电/掉电复位(POR/PDR复位)

2.从待机模式中返回

电源复位将复位除了备份区域外的所有寄存器。

(见图7-1-1)图中复位源将最终作用于RESET管脚,并在复位过程中保持低电平。

复位入口矢量被固定在地址0x0000_0004。

备份区域拥有两个专门的复位,它们只影响备份区域。

7.1.3备份域复位

当以下事件中之一发生时,产生备份区域复位。

软件复位,备份区域复位可由设置备份区域控制寄存器RCC_BDCR中的BDRST位产生。

在VDD和VBAT两者掉电的前提下,VDD或VBAT上电将引发备份区域复位。

7.2时钟

三种不同的时钟源可被用来驱动系统时钟(SYSCLK):

HSI振荡器时钟

HSE振荡器时钟

PLL时钟

这些设备有以下2种二级时钟源:

1.40kHz低速内部RC,可以用于驱动独立看门狗和通过程序选择驱动RTC。

RTC用于从停机/待机模式下自动唤醒系统。

2.32.768kHz低速外部晶体也可用来通过程序选择驱动RTC(RTCCLK)。

当不被使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗。

图7-2-1是系统的时钟树。

图7-2-1时钟树

当HSI被用于作为PLL时钟的输入时,系统时钟的最大频率不得超过64MHz。

用户可通过多个预分频器配置AHB、高速APB(APB2)和低速APB(APB1)域的频率。

AHB和APB2域的最大频率是72MHZ。

APB1域的最大允许频率是36MHZ。

SDIO接口的时钟频率固定为HCLK/2。

RCC通过AHB时钟8分频后供给Cortex系统定时器的(SysTick)外部时钟。

通过对SysTick控制与状态寄存器的设置,可选择上述时钟或CortexAHB时钟作为SysTick时钟。

ADC时钟由高速APB2时钟经2、4、6或8分频后获得。

定时器时钟频率分配由硬件按以下2种情况自动设置:

1.如果相应的APB预分频系数是1,定时器的时钟频率与所在APB总线频率一致。

2.否则,定时器的时钟频率被设为与其相连的APB总线频率的2倍。

FCLK是Cortex™-M3的自由运行时钟。

7.2.1HSE时钟(外部高速时钟)

高速外部时钟信号(HSE)由以下两种时钟源产生:

HSE外部晶体/陶瓷谐振器

HSE用户外部时钟

为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容器必须尽可能地靠近振荡器管脚。

负载电容值必须根据所选择的振荡器来调整。

图7-2-2HSE/LSE时钟源

硬件配置

外部时钟

晶体

陶瓷谐振器

图7-2-2时钟电路

外部时钟源(HSE旁路)

在这个模式里,必须提供外部时钟。

它的频率最高可达25MHz。

用户可通过设置在时钟控制寄存器中的HSEBYP和HSEON位来选择这一模式。

外部时钟信号(50%占空比的方波、正弦波或三角波)必须连到SOC_IN管脚,同时保证OSC_OUT管脚悬空。

见图7-2-2。

外部晶体/陶瓷谐振器(HSE晶体)

4~16Mz外部振荡器可为系统提供更为精确的主时钟。

相关的硬件配置可参考图7-2-2。

在时钟控制寄存器RCC_CR中的HSERDY位用来指示高速外部振荡器是否稳定。

在启动时,直到这一位被硬件置’1’,时钟才被释放出来。

如果在时钟中断寄存器RCC_CIR中允许产生中断,将会产生相应中断。

HSE晶体可以通过设置时钟控制寄存器里RCC_CR中的HSEON位被启动和关闭。

7.2.2HSI时钟

HSI时钟信号由内部8MHz的RC振荡器产生,可直接作为系统时钟或在2分频后作为PLL输入。

HSIRC振荡器能够在不需要任何外部器件的条件下提供系统时钟。

它的启动时间比HSE晶体振荡器短。

然而,即使在校准之后它的时钟频率精度仍较差。

校准:

制造工艺决定了不同芯片的RC振荡器频率会不同,这就是为什么每个芯片的HSI时钟频率在出厂前已经被ST校准到1%(25°C)的原因。

系统复位时,工厂校准值被装载到时钟控制寄存器的HSICAL[7:

0]位。

如果用户的应用基于不同的电压或环境温度,这将会影响RC振荡器的精度。

你可以通过利用在时钟控制寄存器里的HSITRIM[4:

0]位来调整HSI频率。

时钟控制寄存器中的HSIRDY位用来指示HSIRC振荡器是否稳定。

在时钟启动过程中,直到这一位被硬件置’1’,HSIRC输出时钟才被释放。

HSIRC可由时钟控制寄存器中的HSION位来启动和关闭。

如果HSE晶体振荡器失效,HSI时钟会被作为备用时钟源。

7.2.3PLL

内部PLL可以用来倍频HSIRC的输出时钟或HSE晶体输出时钟。

参考图7-2-1时钟树和时钟控制寄存器。

PLL的设置(选择HIS振荡器除2或HSE振荡器为PLL的输入时钟,和选择倍频因子)必须在其被激活前完成。

一旦PLL被激活,这些参数就不能被改动。

如果PLL中断在时钟中断寄存器里被允许,当PLL准备就绪时,可产生中断申请。

如果需要在应用中使用USB接口,PLL必须被设置为输出48或72MHZ时钟,用于提供48MHz的USBCLK时钟。

7.2.4LSE时钟

LSE晶体是一个32.768kHz的低速外部晶体或陶瓷谐振器。

它为实时时钟或者其他定时功能提供一个低功耗且精确的时钟源。

LSE晶体通过在备份域控制寄存器(RCC_BDCR)里的LSEON位启动和关闭。

在备份域控制寄存器(RCC_BDCR)里的LSERDY指示LSE晶体振荡是否稳定。

在启动阶段,直到这个位被硬件置’1’后,LSE时钟信号才被释放出来。

如果在时钟中断寄存器里被允许,可产生中断申请。

外部时钟源(LSE旁路)

在这个模式里必须提供一个32.768kHz频率的外部时钟源。

你可以通过设置在备份域控制寄存器(RCC_BDCR)里的LSEBYP和LSEON位来选择这个模式。

具有50%占空比的外部时钟信号(方波、正弦波或三角波)必须连到OSC32_IN管脚,同时保证OSC32_OUT管脚悬空。

见图7-2-1。

7.2.5LSI时钟

LSIRC担当一个低功耗时钟源的角色,它可以在停机和待机模式下保持运行,为独立看门狗和自动唤醒单元提供时钟。

LSI时钟频率大约40kHz(在30kHz和60kHz之间)。

进一步信息请参考数据手册中有关电气特性部分。

LSIRC可以通过控制/状态寄存器(RCC_CSR)里的LSION位来启动或关闭。

在控制/状态寄存器(RCC_CSR)里的LSIRDY位指示低速内部振荡器是否稳定。

在启动阶段,直到这个位被硬件设置为’1’后,此时钟才被释放。

如果在时钟中断寄存器(RCC_CIR)里被允许,将产生LSI中断申请。

注意:

只有大容量产品可以进行LSI校准

LSI校准:

可以通过校准内部低速振荡器LSI来补偿其频率偏移,从而获得精度可接受的RTC时间基数,以及独立看门狗(IWDG)的超时时间(当这些外设以LSI为时钟源)。

校准可以通过使用TIM5的输入时钟(TIM5_CLK)测量LSI时钟频率实现。

测量以HSE的精度为保证,软件可以通过调整RTC的20位预分频器来获得精确的RTC时钟基数,以及通过计算得到精确的独立看门狗(IWDG)的超时时间。

LSI校准步骤如下:

1.打开TIM5,设置通道4为输入捕获模式;

2.设置AFIO_MAPR的TIM5_CH4_IREMAP位为’1’,在内部把LSI连接到TIM5的通道4;

3.通过TIM5的捕获/比较4事件或者中断来测量LSI时钟频率;

4.根据测量结果和期望的RTC时间基数和独立看门狗的超时时间,设置20位预分频器。

7.2.6系统时钟(SYSCLK)选择

系统复位后,HSI振荡器被选为系统时钟。

当时钟源被直接或通过PLL间接作为系统时钟时,它将不能被停止。

只有当目标时钟源准备就绪了(经过启动稳定阶段的延迟或PLL稳定),从一个时钟源到另一个时钟源的切换才会发生。

在被选择时钟源没有就绪时,系统时钟的切换不会发生。

直至目标时钟源就绪,才发生切换。

在时钟控制寄存器(RCC_CR)里的状态位指示哪个时钟已经准备好了,哪个时钟目前被用作系统时钟。

7.2.7时钟安全系统(CSS)

时钟安全系统可以通过软件被激活。

一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被使能,并在HSE时钟关闭后关闭。

如果HSE时钟发生故障,HSE振荡器被自动关闭,时钟失效事件将被送到高级定时器TIM1的刹车输入端,并产生时钟安全中断CSSI,允许软件完成营救操作。

此CSSI中断连接到Cortex™-M3的NMI中断。

注意:

一旦CSS被激活,并且HSE时钟出现故障,CSS中断就产生,并且NMI也自动产生。

NMI将被不断执行,直到CSS中断挂起位被清除。

因此,在NMI的处理程序中必须通过设置时钟中断寄存器(RCC_CIR)里的CSSC位来清除CSS中断。

如果HSE振荡器被直间或间接地作为系统时钟,(间接的意思是:

它被作为PLL输入时钟,并且PLL时钟被作为系统时钟),时钟故障将导致系统时钟自动切换到HSI振荡器,同时外部HSE振荡器被关闭。

在时钟失效时,如果HSE振荡器时钟(被分频或未被分频)是用作系统时钟的PLL的输入时钟,PLL也将被关闭。

7.2.8RTC时钟

通过设置备份域控制寄存器(RCC_BDCR)里的RTCSEL[1:

0]位,RTCCLK时钟源可以由HSE/128、LSE或LSI时钟提供。

除非备份域复位,此选择不能被改变。

LSE时钟在备份域里,但HSE和LSI时钟不是。

因此:

如果LSE被选为RTC时钟:

只要VBAT维持供电,尽管VDD供电被切断,RTC仍继续工作。

如果LSI被选为自动唤醒单元(AWU)时钟:

详见7.2.5节LSI时钟。

如果VDD供电被切断,AWU状态不能被保证。

如果HSE时钟128分频后作为RTC时钟:

如果VDD供电被切断或内部电压调压器被关闭(1.8V域的供电被切断),则RTC状态不确定。

7.2.9看门狗时钟

如果独立看门狗已经由硬件选项或软件启动,LSI振荡器将被强制在打开状态,并且不能被关闭。

在LSI振荡器稳定后,时钟供应给IWDG。

7.2.10时钟输出

微控制器允许输出时钟信号到外部MCO管脚。

相应的GPIO端口寄存器必须被配置为相应功能。

以下四个时钟信号可被选作MCO时钟:

SYSCLK

HSI

HSE

除2的PLL时钟

7.3外设时钟

STM32系列的芯片,所有外设的时钟都可以独立的打开和关闭,这样可以只把使用的那部分外设时钟打开,这样的好处是,可以降低系统的能耗,满足低功耗的要求。

用户可通过多个预分频器配置AHB、高速APB(APB2)和低速APB(APB1)域的频率。

AHB和APB2域的最大频率是72MHZ。

APB1域的最大允许频率是36MHZ。

下面是各个具体外设的时钟情况:

1》USB时钟:

USB时钟来源于PLLCLK,通过USB分频器为USB外设提供48MHz时钟。

由于USB时钟分频器只能1分频(即不分频)和1.5分频,所以PLL出来的时钟频率只能是48MHz和72MHz。

当需要使用USB时,PLLCLK时钟只能设定为48MHz和72MHz。

2》独立看门狗时钟:

独立看门狗时钟来源于内部的低速RC时钟,可以提供30KHz—60KHz之间,标准时40KHz的时钟。

当独立看门狗打开时,这个时钟被强制打开,并且不会被关闭。

3》I2S时钟:

I2S时钟直接来源于系统时钟,通过使能控制位来控制该外设时钟。

4》AHB时钟:

AHB时钟为其他外设时钟提供时钟源。

AHB时钟通过系统时钟1,2……512分频而来,最高为72MHz。

5》DMA时钟:

DMA时钟来源于AHB,最高可以到72MHz。

6》APB2高速时钟:

APB2时钟来源于AHB时钟1,2,4,8,16分频,最高可以到72MHz。

连接在APB2时钟上的是系统的高速外设,有TIME1、TIME8、SPI1、USART1、ADC1、ADC2、ADC3和所有I/O口等这些外设。

这些外设时钟都可以单独打开和关闭。

7》APB1低速时钟:

APB1时钟来源于AHB时钟1,2,4,8,16分频,最高可达36MHz。

连接在APB1时钟上的是系统的低速外设,有TIME2—TIME7、窗口看门狗、USART2—USART5、SPI2、SPI3、CAN、I2C1、I2C2、BKP后备域、电源控制和DAC时钟。

这些外设可以单独打开和关闭。

7.4RCC库函数

7.4.1函数RCC_DeInit

表7-4-1.描述了函数RCC_DeInit

表7-4-1.RCC_DeInit

函数名

RCC_DeInit

函数原形

voidRCC_DeInit(void)

功能描述

将外设RCC寄存器重设为缺省值

输入参数

无

输出参数

无

返回值

无

先决条件

无

被调用函数

无

1.该函数不改动寄存器RCC_CR的HSITRIM[4:

0]位。

2.该函数不重置寄存器RCC_BDCR和寄存器RCC_CSR。

例:

设置RCC寄存器为初始状态

RCC_DeInit();

7.4.2函数RCC_HSEConfig

表7-4-2.描述了函数RCC_HSEConfig

函数名

RCC_HSEConfig

函数原形

voidRCC_HSEConfig(u32RCC_HSE)

功能描述

设置外部高速晶振(HSE)

输入参数

RCC_HSE:

HSE的新状态

输出参数

无

返回值

无

先决条件

如果HSE被直接或者通过PLL用于系统时钟,那么它不能被停振

被调用函数

无

RCC_HSE

该参数设置了HSE的状态(见表7-4-3.)。

表7-4-3RCC_HSE定义

RCC_HSE

描述

RCC_HSE_OFF

HSE晶振OFF

RCC_HSE_ON

HSE晶振ON

RCC_HSE_Bypass

HSE晶振被外部时钟旁路

例:

使能HSE

RCC_HSEConfig(RCC_HSE_ON);

7.4.3函数RCC_WaitForHSEStartUp

表7-4-4.描述了函数RCC_WaitForHSEStartUp

函数名

RCC_WaitForHSEStartUp

函数原形

ErrorStatusRCC_WaitForHSEStartUp(void)

功能描述

等待HSE起振该函数将等待直到HSE就绪,或者在超时的情况下退出

输入参数

无

输出参数

无

返回值

一个ErrorStatus枚举值:

SUCCESS:

HSE晶振稳定且就绪

ERROR:

HSE晶振未就绪

先决条件

无

被调用函数

无

例:

ErrorStatusHSEStartUpStatus;

/*使能HSE*/

RCC_HSEConfig(RCC_HSE_ON);

/*等待直到HSE起振或超时退出*/

HSEStartUpStatus=RCC_WaitForHSEStartUp();

if(HSEStartUpStatus==SUCCESS)

{

/*在此处加入PLL和系统时钟的定义*/

}

else

{

/*在此处加入超时错误处理*/

}

7.4.4函数RCC_PLLConfig

表7-4-5.描述了函数RCC_PLLConfig

函数名

RCC_PLLConfig

函数原形

voidRCC_PLLConfig(u32RCC_PLLSource,u32RCC_PLLMul)

功能描述

设置PLL时钟源及倍频系数

输入参数1

RCC_PLLSource:

PLL的输入时钟源

输入参数2

RCC_PLLMul:

PLL倍频系数

输出参数

无

返回值

无

先决条件

无

被调用函数

无

RCC_PLLSource

RCC_PLLSource用以设置PLL的输入时钟源。

表7-4-6.给出了该参数可取的值

表7-4-6.RCC_PLLSource值

RCC_PLLSource

描述

RCC_PLLSource_HSI_Div2

PLL的输入时钟=HSI时钟频率除以2

RCC_PLLSource_HSE_Div1

PLL的输入时钟=HSE时钟频率

RCC_PLLSource_HSE_Div2

PLL的输入时钟=HSE时钟频率除以2

RCC_PLLMul

该参数用以设置PLL的倍频系数。

表7-4-7.给出了该参数可取的值

表7-4-7.RCC_PLLMul值

RCC_PLLMul

描述

RCC_PLLMul_2

PLL输入时钟x2

RCC_PLLMul_3

PLL输入时钟x3

RCC_PLLMul_4

PLL输入时钟x4

RCC_PLLMul_5

PLL输入时钟x5

RCC_PLLMul_6

PLL输入时钟x6

RCC_PLLMul_7

PLL输入时钟x7

RCC_PLLMul_8

PLL输入时钟x8

RCC_PLLMul_9

PLL输入时钟x9

RCC_PLLMul_10

PLL输入时钟x10

RCC_PLLMul_11

PLL输入时钟x11

RCC_PLLMul_12

PLL输入时钟x12

RCC_PLLMul_13

PLL输入时钟x13

RCC_PLLMul_14

PLL输入时钟x14

RCC_PLLMul_15

PLL输入时钟x15

RCC_PLLMul_16

PLL输入时钟x16

警告:

必须正确设置软件,使PLL输出时钟频率不超过72MHz

例:

/*设定PLL时钟输出72MHz使用8MHz外部晶振*/

RCC_PLLConfig(RCC_PLLSource_HSE_Div1,RCC_PLLMul_9);

7.4.5函数RCC_PLLCmd

表7-4-8.描述了函数RCC_PLLCmd

函数名

RCC_PLLCmd

函数原形

voidRCC_PLLCmd(FunctionalStateNewState)

功能描述

使能或者失能PLL

输入参数1

NewState:

PLL新状态

这个参数可以取:

ENABLE或者DISABLE

输出参数

无

返回值

无

先决条件

如果PLL被用于系统时钟,,那么它不能被失能

被调用函数

无

例:

/*使能PLL*/

RCC_PLLCmd(ENABLE);

7.4.6函数RCC_SYSCLKConfig

表7-4-9.描述了函数RCC_SYSCLKConfig

函数名

RCC_SYSCLKConfig

函数原形

voidRCC_SYSCLKConfig(u32RCC_SYSCLKSource)

功能描述

设置系统时钟(SYSCLK)

输入参数1

RCC_SYSCLKSource:

用作系统时钟的时钟源

输出参数

无

返回值

无

先决条件

无

被调用函数

无

RCC_SYSCLKSource:

该参数设置了系统时钟(见表7-4-10)。

表7-4-10RCC_SYSCLKSource值

RCC_SYSCLKSource

描述

RCC_SYSCLKSource_HSI

选择HSI作为系统时钟

RCC_SYSCLKSource_HSE

选择HSE作为系统时钟

RCC_SYSCLKSource_PLLCLK

选择PLL作为系统时钟

例:

/*选择PLL作为系统时钟源*/

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

7.4.7函数RCC_GetSYSCLKSource

表7-4-11.描述了函数RCC_GetSYSCLKSource

函数名

RCC_GetSYSCLKSource

函数原形

u8RCC_GetSYSCLKSource(void)

功能描述

返回用作系统时钟的时钟源

输入参数1

RCC_PLLSource:

PLL的输入时钟源

输出参数

无

返回值

用作系统时钟的时钟源:

0x00:

HSI作为系统时钟

0x04:

HSE作为系统时钟

0x08:

PLL作为系统时钟

先决条件

无

被调用函数

无

例:

/*检测HSE是否为系统时钟*/

if(RCC_GetSYSCLKSource()!

=0x04)

{

}

else

{

}

7.4.8函数RCC_HCLKConfig

表7-4-12描述了函数RCC_HCLKConfig

函数名

RCC_HCLKConfig

函数原形

voidRCC_HCLKConfig(u32RCC_HCLK)

功能描述

设置AHB时钟(HCLK)

输入参数1

RCC_HCLK:

定义HCLK,该时钟源自系统时钟(SYSCLK)

输出参数

无

返回值

无

先决条件

无

被调用函数

无

RCC_HCLK:

该参数设置了AHB时钟,表7-4-13.给出了该参数可取的值。

表7-4-13RCC_HCLK值

RCC_HCLK

描述

RCC_SYSCLK_Div1

AHB时钟=系统时钟

RCC_SYSCLK_Div2

AHB时钟=系统时钟/2

RCC_SYSCLK_Div4

AHB时钟=系统时钟/4

RCC_SYSCLK_Div8

AHB时钟=系统

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 第七章 复和系统时钟 第七 系统 时钟

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx