PCB规范要点.docx

PCB规范要点.docx

- 文档编号:7277292

- 上传时间:2023-01-22

- 格式:DOCX

- 页数:17

- 大小:668.39KB

PCB规范要点.docx

《PCB规范要点.docx》由会员分享,可在线阅读,更多相关《PCB规范要点.docx(17页珍藏版)》请在冰豆网上搜索。

PCB规范要点

PCB设计规范

1.设计前的预评估:

PCB的层数,厚度,尺寸,PCB预布局构想,以及关键信号走线要求,关键器件走线要求等。

2.结构布局规范

2.1.布局步骤:

结构设计—抓模块—优化模块—集合模块—优化组合—微调整原件。

2.2.符合结构设计及装配要求。

2.3.根据结构图设置板框尺寸,按结构要素布置安装孔,接插件等需要定位的器件,并给这些器件赋予不可移动的属性。

按工艺设计规范的要求进行尺寸标注。

2.4.根据结构限高图设置印制板的禁止布线区,禁止布局区域,根据某些元件的特殊要求,设置禁止布线区,限高区。

以及考虑通风及散热要求。

2.5.符合生产工艺要求;

3.PCB布局要求

3.1通用器件布局要求

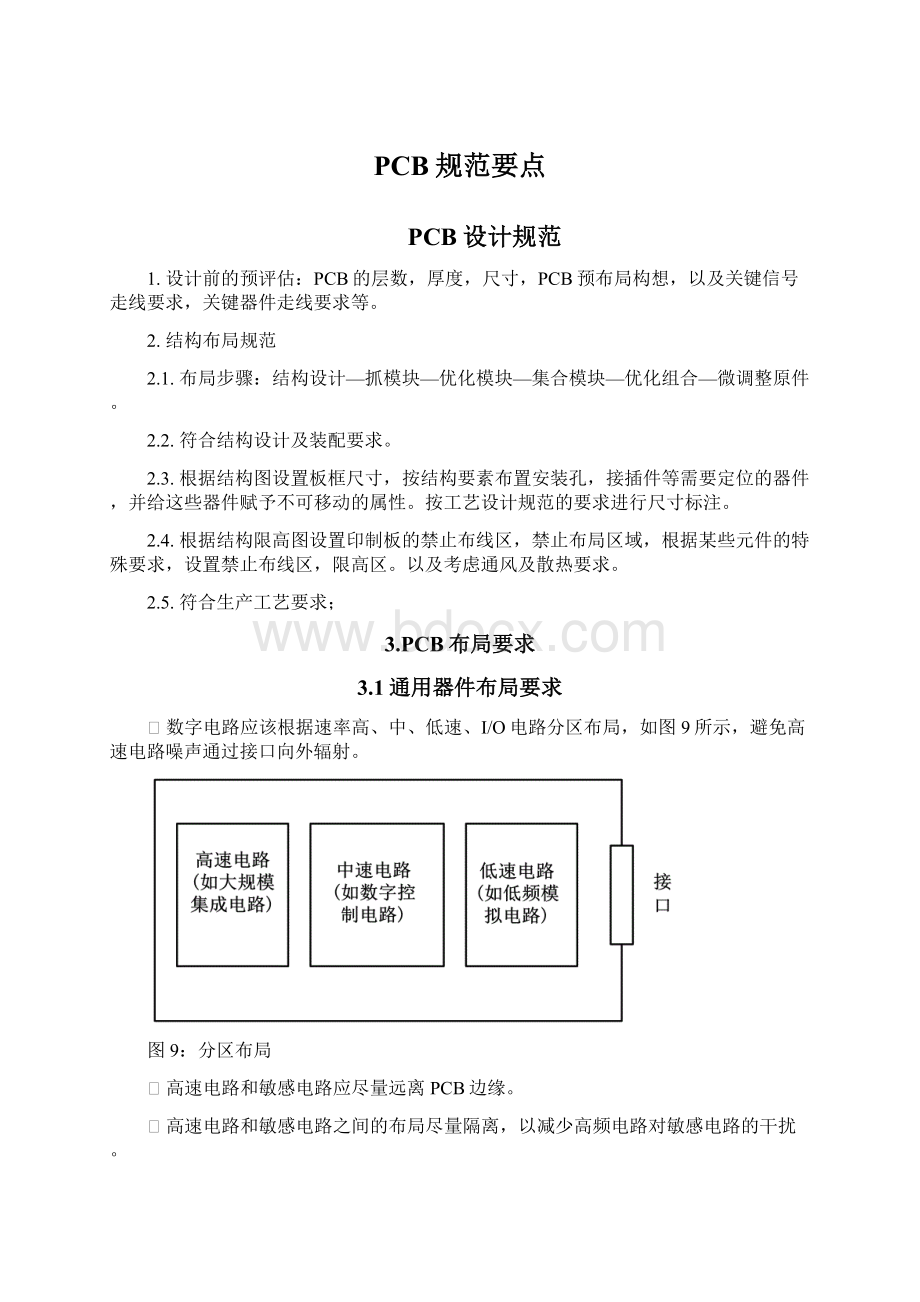

Ø数字电路应该根据速率高、中、低速、I/O电路分区布局,如图9所示,避免高速电路噪声通过接口向外辐射。

图9:

分区布局

Ø高速电路和敏感电路应尽量远离PCB边缘。

Ø高速电路和敏感电路之间的布局尽量隔离,以减少高频电路对敏感电路的干扰。

Ø高速总线信号的过冲和振铃会产生比较严重的EMC问题,需要通过SI仿真采取适当的匹配措施加以抑制。

Ø将PCB分区应为独立的模拟部分和数字部分,如图10所示。

数字电路通过平面对模拟电路的干扰较强。

(a)不正确(b)正确

图10:

数模混合电路分区布局

Ø合适的元器件布局应考虑信号流的走向,弱信号、强信号、数字信号应有序排布。

ØA/D转换器跨模数分区放置。

应注意A/D的模拟地和数字地的交流压差不能大。

在A/D之下是模拟地和数字地相连的最佳位置之一,如图11所示。

图11:

数模转换器连接数模分区

Ø源端串阻应尽量放在靠近驱动器件位置;终端端接器件应尽量放在靠近接收器件位置。

Ø去耦电容的摆放要尽量靠近芯片的电源管脚,如图12所示。

(a)最佳(b)次之

图12:

去耦电容的摆放位置

Ø信号线以不同电平的平面作为参考平面,如图13,当跨越平面分割区域时,参考平面间的续流电容必须靠近信号的走线区域。

图13:

跨接电容的位置

Ø芯片的保护电路应尽可能靠近被保护的芯片放置,如图14。

图14:

芯片的保护电路放置

ØI/O滤波器与变压器应该尽量靠近与其相连的连接器放置,如图15。

(a)不正确

(b)正确

图15:

I/O滤波器位置

Ø如果分区的数字电路与模拟电路之间有少量信号线相联系,则应在其分割开的数字地与模拟地之间搭桥,实现二地的单点连接,桥的位置应在信号线的下方,应保证所有信号线在跨越二区时都从桥的上面走线,如图16。

图16:

模拟地与数字地通过桥连接

Ø如果分区的数字电路与模拟电路之间有很多信号线相联系,且这些信号线很难集中走线,则数字地与模拟地之间不应进行分割,二地为一个完整的地层。

布线时除了联接二区的信号线可以跨区外,各区内部的信号线严禁跨区走线。

3.2时钟布局要求

Ø晶振、晶体以及相关电路应尽量布置在PCB的中间,不要靠近I/O接口或板边。

Ø时钟电路要远离敏感器件布局。

Ø时钟源的滤波电路尽可能的靠近振荡器的电源输入引脚,以最大程度减小环路电流。

Ø晶振去耦电容的摆放要靠近芯片的电源管脚,并且电容的电源线和地线所包围的面积应最小。

Ø晶体和晶振的布局要注意远离大功率的元器件、散热器等发热的器件。

Ø晶体和晶振要尽量靠近与其相关联的IC器件。

3.3接口器件布局要求

Ø选择具有良好高频隔离性能的隔离变压器。

在PCB布局时不要破坏隔离变压器的隔离性能,尽可能不要将隔离变压器的初、次级线圈布放在同一个地层上,而是分别放在二个分割的地上,如图17,用户线通常应接保护地。

图17:

隔离变压器布局位置

Ø用户线上可采用共模滤波和变压器隔离,共模电感的位置必须放在收、发端接地点的电路侧。

Ø用户线一般不应浮空,PCB上用户线参考平面接保护地。

Ø外接电源端口的一些差模和共模滤波器件在PCB板上布局时要尽量靠近电源端口,以减小外部电源噪声耦合进板内的机会,同时也可减小PCB板内耦合出板外的噪声。

图18中L1\C1\C2\C3\C4为电源入口的差模滤波器件,L2为电源入口的共模滤波器件,这些器件均应靠近电源入口放置。

图18:

电源的共模/差模滤波器件

Ø网口、电话口等端口信号线上的所加的一些抑制共模噪声的共模电感在布局时要尽量靠近端口放置,以减小板内噪声通过端口线缆传导和辐射出去,同时也可减小外部噪声通过端口线缆耦合进板内,如图19所示。

图19:

外接端口共模电感布局

Ø一些直流电源端口电源和地信号上串加的高频磁珠尽量靠近端口放置,见图20。

图20:

直流电源端口部分磁珠布局

Ø一些噪声较大的器件及电路(如晶振、时钟驱动、高速处理器、一些高速数字电路等)要尽量远离外接端口放置,以减小这些器件及电路产生的噪声通过平面和空间耦合进端口,再通过端口外接线缆传导和辐射出去。

Ø端口部分的滤波器件要按照信号流向来布局,输入和滤波后的输出要尽量远离,以防止输入信号噪声耦合进输出信号。

Ø各个端口之间的布局尽量不要互相交错,以防止端口之间的互相干扰。

3.4电源器件布局要求

Ø电源部分的布局要按照电源电流的流向来布局,电源输入输出要分开,电源布局采用直线方式布局,尽量不采用迂回布局,以防止电源前后互相干扰。

Ø无论是差模滤波电路还是共模滤波电路,电容和电感上的引线要尽量加宽。

Ø在满足热设计的前提下,电源部分布局要紧凑,紧凑的布局可减小连线长度,减小连线上分布参数带来的不利影响,同时布局紧凑可减小电源环路面积。

Ø电源的输入滤波器布局时尽量靠近电源入口处,如图21所示。

图21:

电源的输入滤波布局

Ø电源滤波器的输入及输出端在布局时要尽量远离,避免噪声从输入端耦合进输出端。

Ø电源部分的布局要尽量远离不相关的强干扰电路及器件,以防止外部噪声耦合进电源造成电源的波动。

Ø电源的去耦钽电容,应靠近电压调整模块的输出地位置。

Ø雷击浪涌保护器件应该尽可能靠近与其相连的连接器放置,如图22。

图22:

雷击浪涌保护器件放置

Ø电源的布局要尽量靠近被供电器件,以缩短电源传输路径,减小电源传输路径上分布参数带来的不利影响。

Ø供电LDO尽量靠近被供电器件,对于那些输出为低电压的LDO要特别注意。

Ø电源的布局要有利于形成小的电源环路和滤波环路,以减小这些环路对外部的干扰,同时这些小的环路也可减小外部噪声对电源的干扰。

图23:

电源的电流环路

4.PCB布线要求

4.1通用布线设计要求

Ø高速信号线要尽量远离外部接口。

Ø高速信号走线要尽量远离晶振和时钟芯片。

Ø在信号层铺铜时,铺铜与信号线之间的间距应大于3H(H为信号线离参考平面的高度),如图24所示。

图24:

走线与铜皮间距

Ø边延触发的中断和复位信号上的测试点不应分叉,如图29所示。

Ø高速串行总线(如SERDES等GHz以上信号)、百兆/千兆以太网线上的测试点不应分叉,如图25。

图25:

关键和高速信号线上不允许出现分叉测试点

Ø高速信号线不能跨越地平面沟槽布线(如图26),以防产生高阻抗回流路径,增加共模和差模辐射。

图26:

高速信号线不允许跨越平面沟槽

Ø高速信号布线时要尽量保持良好的回流路径,可通过在高速信号换层过孔旁添加地过孔/旁路电容等措施改善信号回流。

Ø关键信号尽量不要选择电源平面作为回流平面。

Ø关键信号不能跨越平面沟槽;检查器件管脚和过孔的安全避让,尽量不要有因为过孔密集而破坏平面完整,如图27所示。

图27:

密集过孔导致平面断裂(左)过孔安全间距过大(右)

Ø没有平面隔离的间距很小的相邻信号层走线必须遵循垂直走线的原则,否则会造成线间串扰。

Ø严格控制高速信号和敏感信号路径上的stub,如图28。

图28:

走线Stub

Ø在电路板的所有层中,数字信号只能在电路板的数字部分布线。

Ø在电路板的所有层中,模拟信号只能在电路板的模拟部分布线。

ØPCB的边缘尽量不要有走线,高速信号线和敏感的信号线应该远离PCB板的边缘。

Ø靠近面板等易受ESD影响的区域,尽量在内层走线。

4.2时钟电路的布线

Ø在时钟电路附近或者通过时钟区域处、时钟晶体附近或下面尽量不要布其它高速信号线。

如图29所示,避免信号间产生容性和感性耦合。

图29:

禁止在时钟下方布其它信号线

Ø时钟信号和其它信号的间距应尽量加大。

Ø时钟信号尽量走内层,并以地层为参考平面。

Ø时钟信号上不允许有分叉的测试点。

Ø晶振与晶体的表层应铺地网络铜皮,在该地网络铜皮上应多打地过孔与地平面相连。

Ø对于顶层和底层时钟线,应避免1/4波长的走线。

Ø时钟线应尽量保持良好的回流路径。

可通过在时钟信号换层过孔旁放置地过孔\电容等措施去改善时钟信号的回流。

图30:

时钟线换层的处理

Ø时钟信号等高速信号网络,在多层PCB走线时如果产生了图31所示的闭环和图32所示的开环,这样的闭环和开环都会产生天线效应,从而增加EMI的辐射强度,在设计中都要注意避免。

图31:

闭环图32:

开环

4.3接口电路的布线

Ø端口滤波器件到端口之间的连线要尽量短,如图33所示。

图33:

滤波器件与端口之间的连线

Ø端口部分的信号线尽量布在内层,以防止空间噪声耦合到端口信号线上,再通过端口外接线缆传导和辐射出去。

Ø各个端口之间信号线在布线时不要互相交错,以防止端口之间噪声的互相干扰。

Ø滤波器件(电路)输入和输出信号不要交错在一起,图34中输入输出互相交错的情况应该避免,以防止输入信号的噪声干扰输出信号。

图34:

输入输出信号相交错

Ø与端口不相关的高压、大电流和高速数字信号要远离端口布线,以减小这些信号产生的噪声通过平面和空间耦合进端口。

ØPCB上的用户线尽量远离高速线或时钟线,严禁与相邻的高速线或时钟线长距离平行走线。

4.4电源的布线要求

Ø对于电源的功率部分布线要尽量粗短(如图35中红线部分),可以用敷铜替代布线,以减小布线上分布参数带来的不利影响。

图35:

电源功率部分走线

Ø电源部分布线时要尽量减小高电压大电流回路特别是续流二极管、续流MOS管的电压跳变端所包围的环流面积;要尽量保持电源电路中一些易产生高次谐波的整流、功率开关等器件滤波、吸收回路的最小化,如图36。

图36:

滤波/吸收的环流面积

Ø如图37所示的电源滤波器,L1、L2、Cx(Cx1、Cx2)用来抑制差模噪声,L、Cy(Cy1、Cy2)用来抑制共模噪声。

图37:

电源滤波器

在对图37所示的电源滤波器布线时,抑制差模噪声的差模电容Cx要如图38一样保持到主干电源、地线的引线尽量短,以减小引线电感带来的负面影响;抑制共模噪声的共模电容Cy到地的引线要尽量保持粗短,以减小引线电感带来负面影响,如图39。

(a):

不正确(b)正确

图38:

差模电容Cx的布线方法

图39:

共模电容Cy的布线方法

5电源完整性(PI)设计要求

5.1叠层设计

叠层是PCB的EMC设计中关键的一环,在设计叠层时必须考虑布线分配和电源分割。

Ø叠层必须保证高速信号阻抗可控制在预期的阻抗要求范围内,同时通过阻抗控制保证各信号层阻抗的连续性,以消除因阻抗不连续产生信号反射带来的过冲和振铃对系统EMC不利的影响。

Ø尽量使电源层有紧耦合的参考地平面,以保证电源平面的低阻抗特性和地对电源噪声的耦合吸收,电源、地层间距不应大于10mil,通常应小于5mil。

Ø信号层尽量以地平面为参考平面,在PCB的EMC设计中以地平面为参考优于电源平面。

Ø在各层间厚度设置时,尽量做到以下几点:

Ø尽量使信号层紧耦合参考的平面层,以减小信号回流面积和加强平面层对信号层噪声的耦合吸收。

Ø尽量使相邻的电源层和地层紧耦合以改善电源层阻抗特性。

Ø如有相邻的信号层,除了正交布线规则外,要尽量拉大两相邻信号层之间的间距以尽量减小两相邻信号层之间的噪声互扰。

Ø在叠层安排上要尽量避免有相邻的两个电源层,尤其是电压差别较大的两个电源层,以防止相邻两个电源层噪声的互相耦合导致低电压器件工作不稳定;如不可避免有相邻的两个电源层,要尽量拉大两个电源层间的间距。

5.2信号线的参考平面

信号线的参考平面包括电源平面和地平面。

地平面能够对信号层和电源层产生的噪声加以隔离、屏蔽和吸收,充分的利用地平面的这些特性可以有效地改善系统的EMC;同时还要关注电源平面的谐振和阻抗。

Ø尽量保证参考平面的完整性,参考平面的完整性能保证信号层良好回流路径,同时可有效降低参考平面的阻抗。

Ø尽量保证参考平面尤其电源参考平面的低阻抗特性,参考平面的低阻抗可通过在PCB上加旁路电容和调整叠层等加以改善,在可能的情况下可通过PI仿真来解决。

Ø尽量抑制参考平面在系统工作频率范围内的谐振,抑制参考平面的谐振也可通过在PCB上加旁路电容和调整叠层等加以改善,在可能的情况下可通过PI仿真来解决。

5.3多种电源的分割

Ø对于PCB上小范围内用到的电源如某个IC芯片的核心工作电压,尽量在信号层上敷铜加以解决以保证电源层的完整性,如图40。

但要尽量避免在表层敷电源铜皮,以防止电源不干净带来噪声辐射。

图40:

某BGA核心电压通过信号层敷铜加以解决

Ø对于平面的分割宽度,电压大于12V时,分隔宽度可加大至50mil,反之,可选20~30mil。

对于模拟电源和数字电源的分割宽度需适当加大,以防止数字电源对模拟电源的噪声干扰。

Ø较少节点的电源网络应该尽量在走线层完成(最好采用铺铜皮方式),对于长度较长地电源网络,必须加一些滤波电容。

Ø分割后的电源平面要尽量保持规则,不规则的分割形状易造成平面的谐振和电源阻抗的增大,见如41,电源地平面上应尽量避免有细长条及哑铃形分割。

图41:

某BGA核心电压在电源平面层上的不规则分割及PI仿真结果

Ø如有不规则电源分割如图41,需要注意电流通道是否能承载所需要的电流,在保证能承载所需电流的前提下对于那些窄的瓶颈需要尽量加宽。

Ø相邻层不同的电源平面要避免交叠放置,以防止噪声的互扰。

Ø在平面层分割时要注意:

不要将没有联系的平面之间形成交叠,模拟电源和模拟地;数字电源和数字地,两者要严格分开,不要在平面上存在容性耦合,见图42。

图42:

平面层交叠

Ø电源的分割区域要正确,模拟电源区域上要避免有数字信号和数字器件,数字电源区域上要避免有模拟信号和模拟器件,以防止噪声的互扰。

Ø如有信号层以分割的电源平面为参考平面,电源平面分割时需考虑信号的回流,尽量避免多信号跨越分割平面,如不可避免,要适当以电容搭接形成信号回流通道。

5.4平面的滤波

5.4.1电源地平面阻抗控制

Ø电源平面尽量与地平面紧耦合并成对。

Ø采用两个电源平面时应确保它们都有地平面相邻。

Ø工作频率大于500MHz的芯片,应主要依靠平面电容滤波,并采用组合电容滤波。

总体滤波效果应通过电源完整性仿真确定。

Ø严格控制平面去耦电容的安装电感,如图43所示,包括:

加宽电容引线与加大电容过孔,选用适当的引线方式。

图43:

推荐电容引线

Ø在使用电源完整性(PI)仿真电源平面的阻抗时,要求电源地阻抗控制在目标阻抗以下。

5.4.2高速器件的去耦

Ø在高速器件的电源管脚处应该放置去耦/旁路电容。

Ø为防止高速器件的同步开关噪声带来的地弹,在高速器件的电源管脚附近必须放置1-2个储能电容。

Ø芯片上的电源、地引出线从焊盘引出后就近接电源、地平面,线宽≥0.2mm(8mil),尽量做到≥0.25mm(10mil)。

Ø高速器件应该采用电容组合去耦,缺省电容组合有:

0.1uf、0.01uf、1000pf。

Ø高速器件的去耦电容应选用ESL小,ESR适当的电容,如:

X7R、NPO等。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- PCB 规范 要点

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx