第10章局部总线控制器mpc83xx中文手册上册.docx

第10章局部总线控制器mpc83xx中文手册上册.docx

- 文档编号:7141814

- 上传时间:2023-01-21

- 格式:DOCX

- 页数:76

- 大小:115.74KB

第10章局部总线控制器mpc83xx中文手册上册.docx

《第10章局部总线控制器mpc83xx中文手册上册.docx》由会员分享,可在线阅读,更多相关《第10章局部总线控制器mpc83xx中文手册上册.docx(76页珍藏版)》请在冰豆网上搜索。

第10章局部总线控制器mpc83xx中文手册上册

第十章Localbus

本章介绍了局部总线控制器(LBC)模块。

介绍LBC的外部信号和内存映射寄存器,以及通用片选机制(GPCM)、同步DRAM(SDRAM)机和用户可编程机(UPM)。

最后,包括初始化和应用信息一节,其中有许多关于使用的特色的例子。

10.1绪论

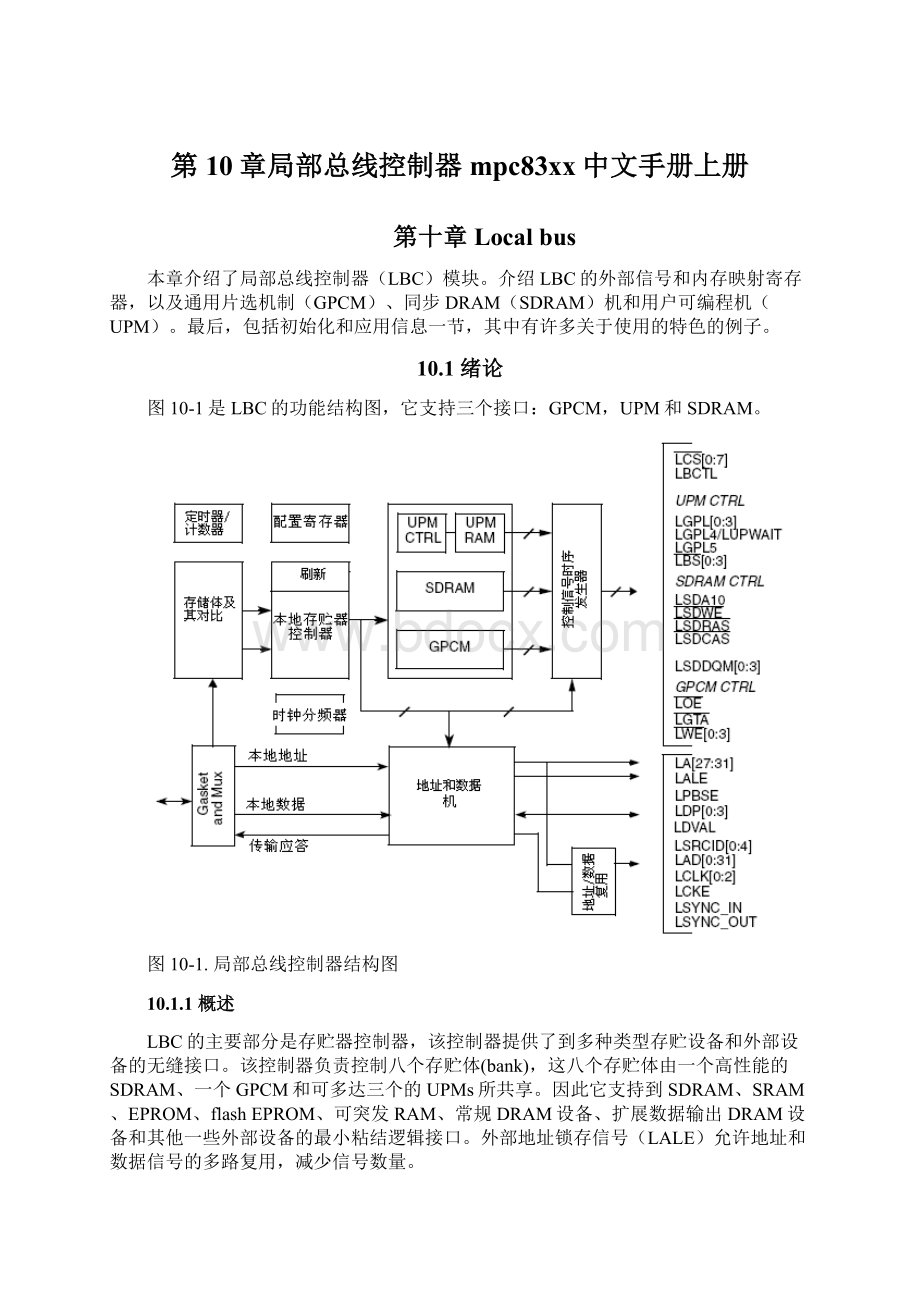

图10-1是LBC的功能结构图,它支持三个接口:

GPCM,UPM和SDRAM。

图10-1.局部总线控制器结构图

10.1.1概述

LBC的主要部分是存贮器控制器,该控制器提供了到多种类型存贮设备和外部设备的无缝接口。

该控制器负责控制八个存贮体(bank),这八个存贮体由一个高性能的SDRAM、一个GPCM和可多达三个的UPMs所共享。

因此它支持到SDRAM、SRAM、EPROM、flashEPROM、可突发RAM、常规DRAM设备、扩展数据输出DRAM设备和其他一些外部设备的最小粘结逻辑接口。

外部地址锁存信号(LALE)允许地址和数据信号的多路复用,减少信号数量。

LBC还包括许多数据校验和保护特性,例如数据奇偶的生成和校验、写保护和一个总线监控器以确保每个总线周期在用户指定的时间内结束。

10.1.2特性

LBC主要包含以下几个方面的特性:

•拥有八个存贮体

—带屏蔽的32位地址译码

—可变存贮块大小(32K字节到2G字节)

—基于存贮体的控制信号生成的选择

—基于存贮体激活的数据缓冲控制

—大事务的自动分段

—用于单访问的奇偶校验,包括读-修改-写(RMW)校验

—写保护能力

—奇偶字节选择

•SDRAM机

—向符合JEDEC标准的SDRAM设备的无缝连接提供控制功能和信号

—支持每个设备多达4个的并发打开页面

—支持32位、16位和8位端口大小的SDRAM

—支持外部的地址和/或命令线缓冲

•通用片选机(GPCM)

—与SRAM、EPROM、FEPROM和外部设备兼容

—系统复位时可用的全局(引导)片选

—引导片选支持8位,16位或32位的设备

—最小可以3个时钟周期访问外部设备

—4个字节写允许信号(

[0:

3])

—输出允许信号(

)

—外部访问终止信号(

)

•三个用户可编程机(UPM)

—基于可编程阵列机控制外部信号的定时,其精度最多可达外部总线时钟周期的四分之一

—在内部主控器请求单拍的或者突发读写访问时运行用户特定的控制信号模式

—UPM刷新定时器运行用户特定的控制信号模式,以支持刷新

—软件可以启动用户特定的控制信号模式

—可把每个UPM定义为支持64,128,256,512K字节和1,2,4,8,16,32,64,128,256M字节大小的DRAM设备

—支持8,16,32位的设备

—页面模式支持一个突发内的连续传输

—内部地址复用支持64,128,256,512K字节和1,2,4,8,16,32,64,128,256M字节大小的页或存贮体

•可选的局部总线内部主设备和局部总线从设备之间的传输监控(局部总线出错报告)

•支持带软件可配置旁路的延迟锁相环(DLL),支持低频总线时钟

10.1.3操作模式

LBC为局部总线提供一个GPCM、一个SDRAM机和三个UPM,对八个存贮体(片选)中可以编程用来操作任何给定机器的存储体数量没有限制。

当把一个存贮器事务分发到LBC时,将存贮器地址与每个存贮体(片选)的地址信息进行比较。

分配给那个存贮体的对应的机器(GPCM、SDRAM或者UPM)获得控制访问的外部信号的所有权,并保持对其控制直到事务结束。

这样,利用在GPCM、SDRAM或UPM模式下,在事务期间,八个片选只有一个是活动的。

10.1.3.1LBC的总线时钟和时钟比率

LBC支持快速内部(系统)时钟和慢速外部总线时钟(LCLK[0:

2])之间2、4和8的比率。

该比率可以通过对时钟比率寄存器(LCRR[CLKDIV])进行软件设置。

该比率对SDRAM模式下的操作不产生影响,但会影响GPCM模式下的信号时序变化的精度和UPM模式下对UPM阵列字的解释。

将总线时钟完全不变驱动地驱动到信号LCLK[0:

2]上,允许在一对信号网之间平等的共享时钟负载,从而可以提高总线时钟的占空比率。

10.1.3.2源ID调试模式

LBC在外部设备信号上提供事务源的ID。

当选择了这些信号的时候,只要LBC外部信号线上的有效地址或数据可用,当前事务源的5位内部ID就出现在LSRCID[0:

4]上。

保留值为0X1F,该值表示任何其他时间在源ID信号上出现无效的地址或数据。

有效的源ID(除0X1F之外的任何值)和外部地址锁存允许(LALE),以及数据有效(LDVAL)的组合方便了调试数据的捕获,具体如下:

•如果在LSRCID[0:

4]上检测到有效源ID且LALE有效,那么就可以从LAD[0:

31]锁存一个有效的完整的32位的地址。

这里要注意的是,在SDRAM的模式下,地址向量包含完整的地址{row,bank,column,lsb’s},对于给定的column地址,row是指对应的相同的row地址;对于给定的端口大小,lsb’s是指未连接的地址的最低有效位。

•如果在LSRCID[0:

4]上检测到有效的源ID且LDVAL有效,则可以从LAD[0:

31]锁存有效数据。

LSRCID[0:

4]和LDVAL信号是复用,它们和其他的功能共享相同的外部信号。

请参考第3章的外部信号描述和第5章的系统配置,从中可以知道如何允许LSRCID/LDVAL信号。

10.1.4参考资料

•MPC8260PowerQUICCII系列参考手册,第4,6和第10章,MPC8260UM/D,Rev.1,Freescale,Inc.,May2003.

10.2外部信号描述

表10-1给出了和LBC有关的外部信号的列表,并描述了它们的功能。

该表还给出了在

有效时的所有外部信号的复位状态。

要了解更多的将其中某些信号用作复位配置信号的情况,参考4.3.2节“上电复位流”。

这里要注意的是,在

有效时,DLL一开始是未锁定的,所以LCLK和LSYNC_OUT的值有可能处在不稳定/抖动的状态,该状态可能会持续几个微秒。

在DLL锁定后,才会在这些信号上驱动稳定的时钟信号。

表10-1.信号属性——汇总

名称

替代功能

模式

说明

信号数

I/O

复位状态

(输出)

LALE

—

—

外部地址锁存允许

1

O

Reset_cfg

—

—

片选0

1

O

Reset_cfg

[1:

7]

—

—

片选[1-7]

7

O

都为高

[0:

3]/

LSDDQM/

[0:

3]

[0:

3]

GPCM

写允许

4

O

Reset_cfg

SDDQM

SDRAM

字节通道数据屏蔽

[0:

3]

UPM

字节(通道)选择

LGPL0

LSDA10

LGPL0

UPM

通用线路0

1

O

Reset_cfg

LSDA10

SDRAM

行地址位/命令位

LGPL1

LGPL1

UPM

通用线路1

1

O

Reset_cfg

SDRAM

写允许

/

/

LGPL2

GPCM

输出允许

1

O

SDRAM

行地址选通

LGPL2

UPM

通用线路2

LGPL3

LGPL3

UPM

通用线路3

1

O

Reset_cfg

SDRAM

列地址选通

/

LGPL4/

LUPWAIT/

LPBSE

GPCM

事务终止

1

I

高阻

LGPL4

UPM

通用线路4

O

LUPWAIT

UPM

外部设备等待

I

LPBSE

—

局部总线奇偶字节选择

O

LGPL5

—

UPM

通用线路5

1

O

Reset_cfg

LBCTL

—

—

数据缓冲控制

1

O

LA[27:

31]

—

—

局部总线非复用地址的最低有效位

5

O

LAD[0:

31]

—

—

复用的地址/数据总线

32

I/O

LDP

—

—

局部总线数据奇偶校验

4

I/O

高阻

LCKE

—

—

局部总线时钟允许

1

O

为高

LCLK[0:

2]

—

—

局部总线时钟。

这些时钟由MCKENR寄存器激活,更详细的信息请参考4.6.3.1节,”MCK允许寄存器(MCKENR)”

3

O

受其他信号驱动

LSYNC_IN

—

—

DLL同步输入

1

I

—

LSYNC_OUT

—

—

DLL同步输出

1

O

驱动

LDVAL

—

LBC调试

局部总线数据有效

1

O

没有连到外部信号上

LSRCID[0:

4]

—

LBC调试

局部总线源ID

5

O

没有连到外部信号上

表10-2给出了LBC外部信号的详细描述。

表10-2.局部总线控制器详细信号描述

信号

I/O

描述

LALE

O

外部地址锁存允许。

局部总线存贮器控制器提供对外部地址锁存的控制,允许在设备信号线上复用地址和数据。

参见10.4.1.2,”外部地址锁存允许信号(LALE)”

状态含义

有效/无效——LALE用每一个存贮器控制器事务开始时的地址置为有效,设定成有效状态的周期数由ORn[EAD]和LCRR[EADC]字段确定,而设置成无效的时间由RCWH[LALE]字段控制。

这里要注意的是在LALE有效期间,任何其他的控制信号都处于无效状态。

[0:

7]

O

片选,可提供八个互斥的片选信号

状态含义

有效/无效——用于启用连到LBC上的特定的存贮设备或外设。

[0:

7]提供基于存贮体的片选,如

对应的是存贮体0,其存贮类型和属性由BR0和OR0定义。

[0:

3]/

LSDDQM[0:

3]/

[0:

3]

O

GPM写允许/SDRAM数据屏蔽/UPM字节选择。

这些信号选择使数据总线的每个字节通道有效。

对于端口大小为32位的存贮体(由BRn[PS]设定),所有四个信号都要定义;对于16位的端口大小,只定义第0和第1位;对于8位的端口大小,只定义第0位。

每个访问的最低有效地址位还为每个给定的数据传输决定采用哪个字节通道。

状态含义

有效/无效——对于GPCM操作,

[0:

3]使每个字节通道都能够进行写操作。

对于SDRAM操作,LSDDQM[0:

3]的功能和符合JEDEC标准的SDRAM设备所提供的DQM或者数据屏蔽信号的功能一样,为每个字节通道提供一个DQM。

当LBC希望写屏蔽或者禁止SDRAM中读数据输出时,LSDDQM[0:

3]被置高。

[0:

3]在UPM模式下是可编程的字节选择信号。

关于设置

[0:

3]的详细信息参见10.4.4.4节“RAM阵列”。

时序

有效/无效——关于

[0:

3]时序的详细的信息参见10.4.2节“通用片选机(GPCM)”。

LSDA10/

LGPL0

O

SDRAMA10/通用线路0号。

状态含义

有效/无效——对于SDRAM访问,代表地址位10。

当驱动行地址的时候,该位驱动地址位10。

当驱动列地址的时候,它是SDRAM命令的一部分。

在UPM模式下,它是六个通用信号之一,驱动在UPM阵列中设定的值。

/

LGPL1

O

SDRAM写允许/通用线路1

状态含义

有效/无效——应连接到SDRAM设备的WE输入端。

在访问SDRAM的时候作为SDRAM的写允许信号。

在UPM模式下,它是六个通用信号之一,驱动在UPM阵列中设定的值。

/

/

LGPL2

O

GPCM输出允许/SDRAMRAS/通用线路2

状态含义

有效/无效——在GPCM模式下,访问存贮器/外设的时候控制存贮器的输出缓冲。

对于SDRAM访问,它为行地址选通(RAS)信号。

在UPM模式下,它是六个通用信号之一,驱动在UPM阵列中设定的值。

/

LGPL3

O

SDRAMCAS/通用线路3

状态含义

有效/无效——在SDRAM模式下,驱动列地址选通(CAS)信号。

在UPM模式下,它是六个通用信号之一,驱动在UPM阵列中设定的值。

/

LGPL4/

LUPWAIT/

LPBSE

I/O

GPCM传输应答/通用线路4/UPM等待/奇偶字节选择

状态含义

有效/无效——在GPCM模式下输入该信号用来终止事务。

在UPM模式下还可以将该信号配置为六个通用输出信号之一,或者作为输入信号强制UPM控制器等待存贮器/设备。

当配置成LPBSE的时候,该信号禁止GPCM和UPM模式下的任何应用。

因为采用读-修改-写奇偶性的系统需要一个附加的存贮设备,并和正常设备一样生成字节选择。

通过外部逻辑对

[0:

3]进行与运算可以获得字节选择的逻辑功能,该运算在字节选择通道中增加了一个延迟,该延迟可以影响存贮器访问的时序。

LBC提供该可选择的字节选择信号,该信号是四个(低有效)字节选择内部与运算的结果,允许到n-奇偶校验设备的无粘合快速连接。

注意:

在UPM将LGPL4/LPBSE置为低状态的期间,可在

/LUPWAIT信号有效(低有效)时对其采样。

对于后续的GPCM事务,它用作

/LUPWAIT。

因此,在

/LUPWAIT变为逻辑1之前,GPCM的事务有可能被过早终止。

解决方法:

解决这个问题的一个方法是确保将

/LGPL4信号用一个外部1KΩ的电阻上拉至3.3V。

这样可以保证在局部总线存贮控制器启动后该GPCM的任何时候

都采样为高(非有效)。

如果将该信号纯作为输入(

/LUPWAIT)使用,则可用一个较弱(10-KΩ)上拉电阻代替;此外,如果该信号用作LPBSE,则不需要采用上拉电阻,因为

/LUPWAIT被禁止了。

软件解决该问题的方法是对UPM编程,这样的话,可以在切换为输入模式之前提前将LGPL4置高。

此时仍需要采用一个弱上拉电阻(10KΩ或者更高),以使用于GPCM目的的

保持稳定。

LGPL5

O

通用线路5

状态含义

有效/无效——在UPM模式下,它是六个通用信号之一,驱动在UPM阵列中设定的值。

LBCTL

O

数据缓冲控制。

当访问某个GPCM或者UPM控制下的存贮体时,该存贮控制器为局部总线激活LBCTL。

对SDRAM机所控制的存贮体的访问将不会激活缓冲控制。

使缓冲控制无效可以通过设定ORn[BCTLD]来实现。

状态含义

有效/无效——一般作为连到LAD线路上的总线收发器的write/

控制。

要注意的是当LBCTL为高的时候,外部数据缓冲一定不能驱动和LBC发生冲突的LAD信号线,因为LBCTL在复位和地址阶段时将会保持高电平。

LA[27:

31]

O

局部总线非复用地址的最低有效位。

LA[27:

31]上驱动的所有位都是为8位端口大小定义的。

对于32位的端口大小,不用关注LA[30:

31]的值;对于16位的端口大小,无需关注LA31的值。

状态含义

有效/无效——尽管LBC共享一条地址和数据总线,但RAM地址可多达5个最低有效位始终出现在专门的地址信号LA[27:

31]上。

在地址阶段可以使用解锁代替LAD[27:

31]连接到地址的最低5个有效位。

对于某些RAM设备,比如说fast-pageDRAM,LA[27:

31]用作突发访问期间的列地址偏移量。

LAD[0:

31]

I/O

复用的地址/数据总线。

当在BRn[PS]中将端口配置为32位的时候,LAD[0:

31]所有的信号线必须都连接到外部RAM数据总线,其中LAD[0:

7]是最高有效字节通道(地址偏移量为0)。

对于16位的端口大小,LAD[0:

7]连接到最高有效字节通道(地址偏移量为0),LAD[8:

15]连接到最低有效字节通道(地址偏移量为1);对于16位的端口LAD[16:

31]无用。

对于8位的端口大小,只有LAD[0:

7]连接到外部RAM。

状态含义

有效/无效——LAD[0:

31]是一条共享的32位地址/数据总线,外部RAM设备通过它传送数据和接收地址。

时序

有效/无效——在LALE有效期间,LAD[0:

31]上驱动的是用于后续访问的RAM地址,在LALE有效时,外部逻辑应将地址置于LAD[0:

31]上,在LALE无效时锁存该地址。

在LALE无效之后,此时LAD[0:

31]或者受写数据的驱动或者被LBC置于高阻状态,以便对外部设备驱动的读数据进行采样。

在写访问的最后一个数据传输之后,LAD[0:

31]将被再次置为高阻状态。

LDP[0:

3]

I/O

局部总线数据奇偶校验位。

驱动和接收LAD[0:

31]上对应的数据阶段的奇偶校验位。

状态含义

有效/无效——在访问期间,对LAD[0:

31]的每8位都会产生一个奇偶校验位。

这样,LDP0是LAD[0:

7]的奇偶校验位,而LDP3是LAD[24:

31]的奇偶校验位。

对于端口尺寸小于32位的不用的字节通道则没有定义其奇偶校验位。

时序

有效/无效——驱动和接收LAD[0:

31]上对应的数据奇偶校验位。

对于读访问来说,在LDP[0:

3]上采样每个字节通道的奇偶校验位的时序与在LAD[0:

31]上采样读数据的时序相同。

LDP[0:

3]的阻态变化和LAD[0:

31]一致。

LCKE

O

局部总线时钟允许

状态含义

有效/无效——用于符合JEDEC标准的SDRAM设备的总线时钟允许信号(CKE)。

在正常SDRAM操作期间有效。

LCLK[0:

2]

O

局部总线时钟

状态含义

有效/无效——LCLK[0:

2]为分配的负载提供相同的总线时钟信号。

如果允许LBCDLL(见上图10-19的LCRR[DBYP]),总线时钟相位早于其他LBC信号的跳变(比如LAD[0:

310:

15]和

),提前的时间为匹配LSYNC_OUT和LSYNC_IN之间建立的DLL时序循环所需要的延时。

LSYNC_OUT

O

DLL同步输出

状态含义

有效/无效——总线时钟的复制,出现在LSYNC_OUT上,应通过被动时序循环传播,最后返回到LSYNC_IN,以获得正确的DLL锁定。

时序

有效/无效——时序循环所产生的时间延迟必须补偿LCLK[0:

2]双向传输时间和系统中的时钟同步驱动器。

只有时序循环负载才能出现在LSYNC_OUT上。

LSYNC_IN

I

DLL同步输入

状态含义

有效/无效——见关于LSYNC_OUT的描述。

LDVAL

O

局部总线数据有效(仅用于LBC调试模式)

状态含义

有效/无效——对于读访问,LDVAL在立即对LAD[0:

31]上读数据采样之前的一个总线周期中有效。

对于写访问,LDVAL在LAD[0:

31]上的当前写数据有效的最后一个周期中有效。

在突发传输中,LDVAL在每个数据节拍中都有效。

时序

有效/无效——只有在LBC处于系统调试模式时才有效。

在调试模式中,当LBC产生数据传输应答的时LDVAL有效。

LSRCID[0:

4]

O

局部总线源ID(仅用于LBC调试模式)。

在调试模式中,LSRCID[0:

4]的所有信号将被置高,除非LSRCID[0:

4]驱动的是标识控制LBC的内部系统设备的调试源ID。

状态含义

有效/无效——一直保持高电平,直到最后一个LALE有效的总线周期,此时指示地址的源ID,或者直到LDVAL有效,此时指示与数据传输相关联的源ID。

在地址调试的情况下,只有当LAD[0:

31]上的地址包含所有的物理地址位—带有可选的填充—以重新构建提交给LBC的系统地址时,LSRCID[0:

4]才是有效的。

例如,LSRCID[0:

4]只有在SDRAM访问的CAS阶段才是有效的,因为在CAS周期中,列、存贮体选择和行地址(通常不用)位都出现在LAD[0:

31]上。

10.3内存映射/寄存器定义

表10-3列出了LBC的内存映射寄存器。

偏移量在0x000-0xFFF范围的未定义的4字节地址空间是保留的。

表10-3.局部总线控制器内存映射

地址偏移量

用途

操作

复位

节/页

0x0_5000

基寄存器0

R/W

0x0000_RR011

10.3.1.2/10-12

0x0_5008

基寄存器1

0x0000_0000

0x0_5010

基寄存器2

0x0_5018

基寄存器3

0x0_5020

基寄存器4

0x0_5028

基寄存器5

0x0_5030

基寄存器6

0x0_5038

基寄存器7

0x0_5004

可选寄存器0

R/W

0x0000_0FF7

10.3.1.2/10-12

0x0_500C

可选寄存器1

0x0000_0000

0x0_5014

可选寄存器2

0x0_501C

可选寄存器3

0x0_5024

可选寄存器4

0x0_502C

可选寄存器5

0x0_5034

可选寄存器6

0x0_503C

可选寄存器7

0x0_5068

MAR—UPM地址寄存器

R/W

0x0000_0000

10.3.1.3/10-18

0x0_5070

MAMR—UPMA模式寄存器

R/W

0x0000_0000

10.3.1.4/10-19

0x0_5074

MBMR—UPMB模式寄存器

R/W

0x0000_0000

10.3.1.4/10-19

0x0_5078

MCMR—UPMC模式寄存器

R/W

0x0000_0000

10.3.1.4/10-19

0x0_5084

MRTPR—存贮器刷新定时器预分频寄存器

R/W

0x0000_0000

10.3.1.5/10-21

0x0_5088

MDR—UPM数据寄存器

R/W

0x0000_0000

10.3.1.6/10-22

0x0_5094

LSDMR—SDRAM模式寄存器

R/W

0x0000_0000

10.3.1.7/10-22

0x0_50A0

LURT—UPM刷新定时器

R/W

0x0000_0000

10.3.1.8/10-24

0x0_50A4

LSRT—SDRAM刷新定时器

R/W

0x0000_0000

10.3.1.9/10-25

0x0_50B0

LTESR—传输错误状态寄存器

Read/

位复位

0x0000_0000

10.3.1.10/10-26

0x0_50B4

LTEDR—传输错误禁止寄存器

R/W

0x0000_0000

10.3.1.11/10-27

0x0_50B8

LTEIR—传输错误中断寄存器

R/W

0x0000_0000

10.3.1.12/10-28

0x0_50BC

LTEATR—传输错误属性寄存器

R/W

0x0000_0000

10.3.1.13/10-28

0x0_50C0

LTEAR—传输错误地址寄存器

R/W

0x0000_0000

10.3.1.14/10-29

0x0_50D0

LBCR—配置寄存器

R/W

0x0000_0000

10.3.1.15

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 10 局部 总线 控制器 mpc83xx 中文 手册 上册

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx