88点阵显示电路课程报告.docx

88点阵显示电路课程报告.docx

- 文档编号:6959117

- 上传时间:2023-01-13

- 格式:DOCX

- 页数:12

- 大小:1.66MB

88点阵显示电路课程报告.docx

《88点阵显示电路课程报告.docx》由会员分享,可在线阅读,更多相关《88点阵显示电路课程报告.docx(12页珍藏版)》请在冰豆网上搜索。

88点阵显示电路课程报告

一、设计目的

这次课程设计主要是通过对FPGA(现场可编程门阵列)芯片的设计实践,使学生掌握一般的PLD(可编程逻辑器件)的设计过程、设计要求、设计内容、设计方法,能根据要求及工艺需要进行电子芯片设计并制定有关技术文件。

这个课题还要求我们掌握8×8点阵显示电路原理和VHDL设计方法,学习用VHDL语言设计较复杂电路,利用EDA技术知识,解决常见实际问题的能力,使学生积累实际EDA编程经验。

二、设计要求

(1)熟悉掌握常用仿真开发软件QuartusⅡ9.0,能熟练运用开发软件完成特定功能的电子电路的仿真、软硬件调试;

(2)用8X8LED点阵实现简单字符的显示:

1)LED共阳方式;

2)采用扫描的方式显示信息,信息内容可存于文件;

3)显示方式:

自动滚动或者手动选择;

4)完成全部流程:

设计规范文档、模块设计、代码输入、功能仿真、约束与综合、布局布线、下载验证等。

三、总体设计方案要求

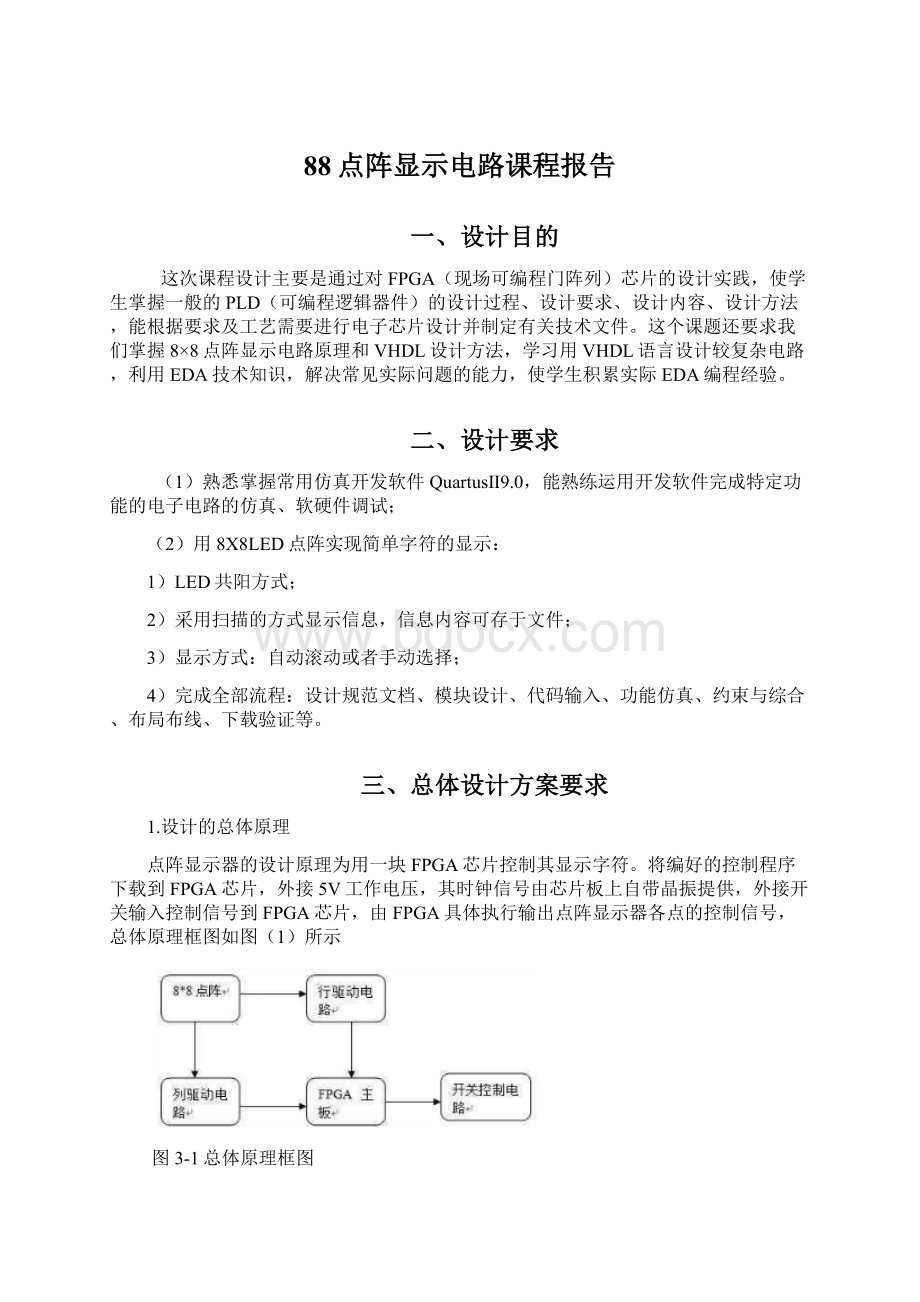

1.设计的总体原理

点阵显示器的设计原理为用一块FPGA芯片控制其显示字符。

将编好的控制程序下载到FPGA芯片,外接5V工作电压,其时钟信号由芯片板上自带晶振提供,外接开关输入控制信号到FPGA芯片,由FPGA具体执行输出点阵显示器各点的控制信号,总体原理框图如图

(1)所示

图3-1总体原理框图

2.设计内容

若要用点阵发光二极管显示字符,首先要将字符放在一个方块内,方块分成8×8共64个小方块,在方块内写上字符,小方块里有字符笔划则填“1”,无笔划则填“0”,这样就形成了一个字符的二进制数据。

图

(2)为8×8点阵LED外观及引脚图,其等效电路如图(3)所示,只要

其对应的X、Y轴顺向偏压,即可使LED发亮。

例如如果想使左上角LED点亮,则Y0=1,X0=0即可。

应用时限流电阻可以放在X轴或Y轴。

要使一个字符在显示器整屏显示,点阵点阵发光显示器就必须通过快速逐列点亮,而且是周而复始的循环点亮,使人眼的暂留视觉效应形成一个全屏字符。

图3-28×8点阵LED外观及引脚图

图3-38×8点阵LED等效电路

四、EDA设计及仿真

1.计数器

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDZDQIS

PORT(CLK:

INSTD_LOGIC;

RST:

INSTD_LOGIC;

QOUT:

OUTSTD_LOGIC_VECTOR(5DOWNTO0));

END;

ARCHITECTUREDZDQOFDZDQIS

SIGNALQ0:

STD_LOGIC_VECTOR(5DOWNTO0);--地址读取信号

BEGIN

P0:

PROCESS(CLK)

VARIABLEAQ1:

STD_LOGIC_VECTOR(5DOWNTO0);--末位地址

VARIABLEATEMP:

INTEGERRANGE0TO16;--循环计数

VARIABLEAQ0:

STD_LOGIC_VECTOR(5DOWNTO0);--初始地址

BEGIN

IFRST='1'THEN

AQ1:

="001000";--末位地址初值

ELSIF(CLK'EVENTANDCLK='1')THEN

AQ0:

=AQ0+1;--依次读取前8位地址

IF(AQ0=AQ1)THEN

AQ0:

=AQ0-"001000";

ATEMP:

=ATEMP+1;--当读完8位返回首地址

IF(ATEMP=16)THEN

AQ0:

=AQ0+1;

AQ1:

=AQ1+1;

ATEMP:

=0;--重复读取第一屏16遍,首地址,末地址均加1,显示下一屏

IF(AQ0="100001")THEN

AQ0:

="000000";--首地址回到000000

AQ1:

="001000";--末地址回到001000

ENDIF;

ENDIF;

ENDIF;

ENDIF;

QOUT<=AQ0;

ENDPROCESSP0;

END;

图4-1计数器框图

图4-2计数器时序仿真图

计数器的波形分析:

由程序及仿真波形图可以看出该计数器每个上升沿都从ROM中读出一个数,然后下一个上升沿读下一个数,读出0—7的内容后,返回初始值重新读,反复16次之后,读从1—8的数值。

2.行变换

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDZ_LEDIS

PORT(CLK:

INSTD_LOGIC;

HANG_OUT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));--行输出

END;

ARCHITECTUREDZ_LEDOFDZ_LEDIS

COMPONENTROOM

PORT(ADDRESS:

INSTD_LOGIC_VECTOR(5DOWNTO0);

CLOCK:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDCOMPONENT;--调用ROM

SIGNALHANG:

STD_LOGIC_VECTOR(7DOWNTO0);--行变换信号

BEGIN

P1:

PROCESS(HANG,CLK)

BEGIN

IF(CLK'EVENTANDCLK='1')THEN

IFHANG(7DOWNTO0)="00000000"ORHANG(7DOWNTO0)="10000000"THEN

HANG(7DOWNTO0)<="00000001";

ELSIFHANG(7DOWNTO0)<="00000001"THEN

HANG(7DOWNTO0)<="00000010";

ELSIFHANG(7DOWNTO0)<="00000010"THEN

HANG(7DOWNTO0)<="00000100";

ELSIFHANG(7DOWNTO0)<="00000100"THEN

HANG(7DOWNTO0)<="00001000";

ELSIFHANG(7DOWNTO0)<="00001000"THEN

HANG(7DOWNTO0)<="00010000";

ELSIFHANG(7DOWNTO0)<="00010000"THEN

HANG(7DOWNTO0)<="00100000";

ELSIFHANG(7DOWNTO0)<="00100000"THEN

HANG(7DOWNTO0)<="01000000";

ELSIFHANG(7DOWNTO0)<="01000000"THEN

HANG(7DOWNTO0)<="10000000";

ENDIF;--信号HANG进行逐列扫描

ENDIF;

HANG_OUT<=NOTHANG;

ENDPROCESSP1;

END;

图4-3行变换原理框图

图4-4行变换的时序仿真波形图

行变换部分在每一个上升沿进行判断,从而使列从右到左不断扫描。

但是,由于HANG信号应为低电平有效,但是在仿真的时候若将信号定义为“11111110”、“11111101”、“11111011”、“11110111”、“11101111”、“11011111”、“10111111”、“01111111”时,仿真错误。

所以用HANG_OUT<=NOTHANG进行仿真。

3.ROM

这里的ROM并没有用VHDL代码进行编写,而是利用原理图,直接进行设置,并建立后缀为.mif的文件,放入其中作为存储的内容。

实现方法如下:

1、点击file→new,选择MemoryLnitializationFile

2、选择存储空间为40,更改数据类型为16进制,输入如下数字:

0000000000000000

0000525252527E00

00FE9292FE9292FE

5E52525252527200

0000000000000000

3、点击保存,此时不要建立工程

4、点击file→new,选择点击BlockDiagram/SchematicFile

5、在空白处双击鼠标左键,选择MegaWizardPlug-lnManager选择next,选择MemoryCompiler→ROM-1PORT,键入名称ROM

6、将存储空间选为32字节,去掉q’

7、添加刚刚制作的后缀为.mif的文件。

8、保存并建立工程。

图4-5ROM原理框图

4、系统设计

将上述的两个程序生成元件,与ROM一起放在原理图文件中并进行连接,具体过程如下:

1、在程序输入文件中点击file→Create/Update→CreateSymbolFilesForCurrentFile

2、将两个程序都生成元件,然后进入原理图文件,在空白处双击鼠标左键,在quartus/libraries中就能找到生成的元件,将对应的管脚连接起来。

图4-6总原理框图

3、保存、编译并仿真

图4-7总程序的时序仿真波形图

程序仿真波形图分析:

在整个程序中时钟信号统一,为了保证读取的数据和HANG信号能一一对应。

HANG信号为“0”以此左移,Q不断输出存储数据。

五、硬件实现

1、给出硬件实现

实验步骤:

⑴打开QuartusⅡ9.0软件,点击新建选择VHDLFile,然后把程序输入进去,然后保存,保存名字和程序的名字相同;

⑵建立新工程管理窗,将设计文件加入工程,选择仿真器及其综合器类型,在选择完目标芯片后结束设置;

(3)保存文件点击软件页面上方的编译按键进行编译;

(4)编译成功后,打开波形编辑器,设置仿真时间区域,然后编辑输入波形,进行软件仿真,观察仿真结果。

(5)在引脚锁定,选择编程模式和配置后进行下载,进行硬件测试。

图5-1脚码锁定图

2.硬件仿真结果

(1)调试时遇到的问题

下载完成后,上电调试时,点阵显示器有一行两列不亮,经检查后发现时因为点阵显示器与硬件电路板接触不良,将其按紧,使其接触良好后,问题解决。

显示器显示固定的图案,经分析,软件应该没显示问题,硬件无接线问题,可能是时钟频率过高,显示的字变化太快,人眼不能分辨。

将软件改写,使经分频器分频后的频率降低,在重新编译,下载调试,发现其一屏一屏显示时,能正常显示汉字,并且速度不算太快。

(2)通过修改程序等措施排除调试问题后,得到正确硬件效果,如下图所示:

图5-2硬件显示字符“E”

图5-3硬件显示字符“田”

图5-4硬件显示字符“2”

六、设计总结

通过本次EDA课程设计,我们加深了课上所学,在此次点阵数字显示电路设计过程中,进一步熟悉了quartus软件的使用,深入了解了芯片的结构及性能参数。

在焊接完电路板后调试过程应注意以下几点:

用万用表检测电路的焊接中是否有虚焊和漏焊;检测电源电压是否为5V;用万用表测试电源通道不短路后加电;给行以高电平,给列以低电平,依次检测每个二极管是否都正常发光;用万用表检测开关的连接是否有误。

值得注意的是,仿真与电路焊接时有一定区别的,并不完全一致,焊接过程要仔细了解各接点的关系。

经过课程设计,我感觉到个人的能力往往是有限的,通过集体,集思广益,任何问题都可以得到合理的解决办法。

七.参考文献

⑴孙俊逸,EDA技术课程设计,华中科技大学出版社,2009;

(2)杨旭,EDA技术基础与实验教程,清华大学出版社,2010;

(3)VolneiA.Pedroni.VHDL数字电路设计教程.电子工业出版社;

(4)杭州康芯电子有限公司.EDA技术实验讲义;

八、设计生成的电路图

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 88 点阵 显示 电路 课程 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx