数码管扫描显示电路16开.docx

数码管扫描显示电路16开.docx

- 文档编号:6904187

- 上传时间:2023-01-12

- 格式:DOCX

- 页数:10

- 大小:432.75KB

数码管扫描显示电路16开.docx

《数码管扫描显示电路16开.docx》由会员分享,可在线阅读,更多相关《数码管扫描显示电路16开.docx(10页珍藏版)》请在冰豆网上搜索。

数码管扫描显示电路16开

实验二数码管扫描显示电路

一、实验目的

通过使用Max+plus2开发工具设计简单数字电路的实验,学习有关可编程逻辑器件PLD的基本知识,掌握原理图设计输入、编译、仿真的基本方法,提高对EDA设计方法的认识。

为进一步学好用好EDA设计奠定基础

二、实验要求

(1)利用Max+plus2开发系统采用原理图方式进行设计,计数器每秒计一次数,外围8个数码管显示十进制计数器的计数结果,同时计数器的输出又作为数码管位译码输入信号,从而形成扫描信号。

(2)输入设计完成后,为验证逻辑功能的正确性应进行逻辑功能仿真。

(3)下载到实验板进行实验验证。

三、实验设备

个人计算机、GEXINEDAPRO/240H实验箱,PLD器件型号为ACEX系列的EP1K30QC208型号,下载电缆,插线等。

四、实验过程

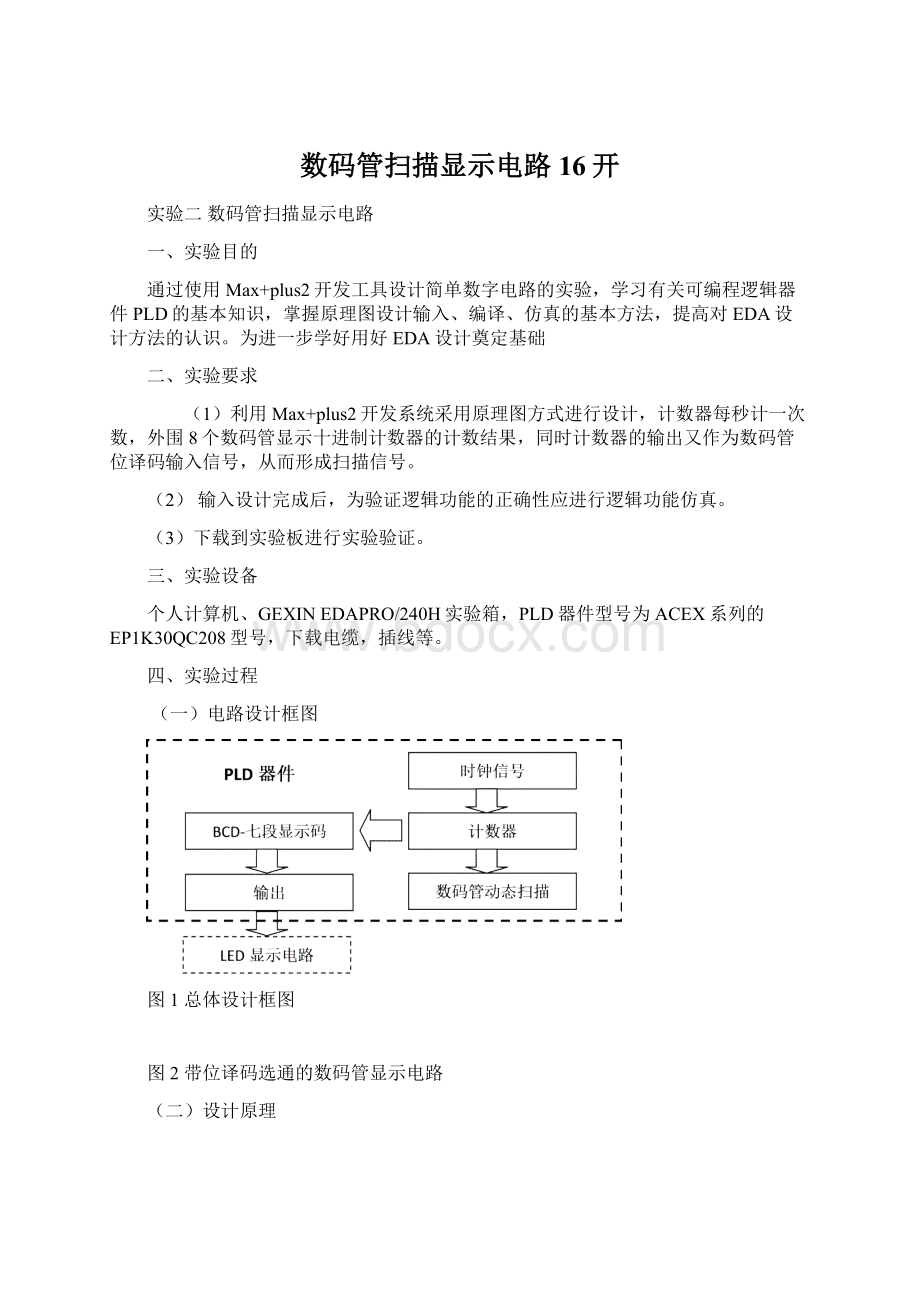

(一)电路设计框图

图1总体设计框图

图2带位译码选通的数码管显示电路

(二)设计原理

图3设计原理图

在原理图方式中设计了两个模块,其中一个使用74160十进制加法计数器的输出QA,QB,QC形成共阴极数码管位译码选通输入信号(8个数码管需8位扫描信号,实验板上8个数码管带3×8译码器,因此只需三位扫描信号)。

QA,QB,QC,QD作为另一个BCD码译码模块的输入数据,译码模块的输出为七段显示码,输出端口A~G通过数码管驱动电路分别驱动各段来点亮动态数码管。

74160的输入端有时钟信号CLK和复位信号RESET。

(三)设计过程

a、打开图形编辑器

点击File菜单,选择New选项,打开如图4所示New对话框,单选GraphicEditorfile,最后点击OK按钮。

b、原理图设计输入

在图形编辑器窗口的空白处单击鼠标左键以确定输入位置,双击鼠标左键,将出现一个EnterSymbol对话框,如图5所示,在symbolLibrary框中鼠标双击以选择相应的库。

则所选库中所有图元在SymbolFiles列表框中显示出来,单击选择所需图元,然后选择OK,即可输入图元。

图4New对话框

图5EnterSymbol对话框

(1)输入图元

根据原理图,在该实验中,需输入74160和7448图元,这两个图元在符号库“..\maxplus2\max2lib\mf\”中;以及输入input、output和vcc图元,这三个图元在符号库“..\maxplus2\max2lib\prim\”中。

(2)连线

图元输入完成后,需将对应的两个端口连接。

将鼠标移到其中一个端口,则鼠标自动变为’+’形状。

一直按住鼠标左键并将鼠标拖到第二个端口,放开左键,则一条连线被画好了。

如果需要删除一条连线,单击该线并按Del键即可。

(3)端口命名

端口连接完成后,还需对输入、输出图元或节点命名。

在图元的PIN_NAME处双击,然后输入名字,名字第一个字符必须是字母。

c、保存文件

选择File菜单的Save选项,将出现如图6SaveAs对话框。

在FileName对话框内输入设计文件名,注意文件扩展名为“.gdf”,然后选择OK即可保存文件。

图6SaveAs对话框

d、编译文件

编译文件按如下步骤进行:

首先,在编译一个文件前,必须确定一个设计文件作为当前项目。

按如下步骤确定项目名:

(1)在File菜单中选择Project\Name项,将出现ProjectName对话框;

图7ProjectName对话框

(2)在Files列表框内选择需编译的文件;

(3)选择OK按钮,即可将该设计文件设定为当前项目,系统的标题条将显示新的项目名称。

若将正编辑的文件设定为当前项目,只需在File菜单中选择Project/SetProjecttoCurrentFile即可,如下图8所示。

图8

其次,选择目标文件下载的目标器件。

在主菜单Assign内选择Device项,将出现Device对话框;

在DeviceFamlily框内选择器件系列,这里我们选择ACEX1K系列,在列表框Devices中选择具体型号为EP1K30QC208-3。

注意:

对话框底部的两个选项不选。

图9Device对话框

最后,打开编译器窗口编译

在系统的MAX+plusⅡ菜单中选择Compiler项即可打开编译器窗口,如图所示。

单击Start按钮即可开始编译。

编译成功会出现如下对话框。

图10编译成功信息对话框

e、逻辑仿真

程序下载前,为验证以上所设计电路的逻辑功能是否正确,可先进行逻辑功能仿真。

<1>首先生成仿真波形文件

(a)打开波形编辑器

点击主菜单的MAX+plusⅡ/WaveformEditor选项,就可在屏幕上显示波形编辑器窗口。

在未输入信号名以前,整个窗口是空白的。

图11波形编辑器窗口

(b)确定仿真持续时间

选择主菜单File中的EndTime选项,可打开EndTime对话框来设定仿真时间的长短。

(c)选入输入输出端口名

点击主菜单Node/EnterNodefronSNF即可打开脚位接点对话框。

在对话框左下角Type下面的选项选择Inputs和outputs,点击对话框右上角的List选项,则在AvailableNodes&Groups列表栏中列出了所有输入输出端口名。

点击对话框中间的=>按钮,将输入输出端口名选进右侧的SelectedNodes&Groups栏,然后点击OK按钮。

则在波形编辑窗口显示了输入输出端口名。

图12选入输入输出端口窗口

(d)编辑输入信号波形

通过波形编辑器左侧的信号设置工具栏可以进行输入信号的波形编辑。

对于输出信号波形,由仿真结果确定,可以把它设置为缺省值。

(e)存盘

信号波形编辑完成后存盘,文件名采取默认方式即可。

<2>打开仿真器;

点击主菜单MAX+plusⅡ\Simulator项,此时弹出Simulator对话框。

如图13所示。

图13

点击对话框的Start按钮,仿真即开始。

仿真结束后单击右下角的OpenSCF按钮即可以显示仿真结果。

如图14所示。

图14仿真结果

f、器件编程

器件编程按以下步骤完成:

(1)管脚设定。

即选择PLD目标器件的某些I/O管脚作为所设计电路的输入输出端口。

具体操作为:

选择主菜单MAX+plusⅡ中的FloorplanEditor选项打开管脚设定窗口。

若窗口下面部分不是Device视图,可选择主菜单Layout中的DeviceView和CurrentAssignmentsFloorplan,即如下图15操作,则可看到器件的管脚排列情况。

图15

在UnassignedNodes&Pins列表框中会出现所设计电路的输入输出端口命名。

将输入输出端口名分别用鼠标拖放到器件的一个I/O管脚上,实现管脚的设定,注意Clk端口名应和器件的GlobalCLK管脚相对应。

管交设定完成后,再编译一次,系统生成最终编程文件。

下图16的管脚设定情况可供参考。

图16管脚设定情况

(2)器件设定的引脚和数码管显示电路连接。

将实验箱左侧的8个数码管上方位选扫描信号接线组“DS1-8A(T)”和数码管段位引线组的引线插孔分别和目标器件的73,74,75及83,85,86,87,88,89,90管脚插孔通过导线连接。

代表时钟信号Clk的79管脚插孔和实验箱上的频率组CLOCK(T)引线插孔之一相连,这里和21号插孔连接(可提供1Hz时钟)。

代表复位信号Reset的92管脚插孔和实验箱上的多功能复用按键F1~F12引线插孔之一相连,这里和F1插孔连接。

(3)打开编程器窗口编程。

在MAX+plusⅡ主菜单中选择Programmer项,编程器窗口如图17所示。

通过JTAG实现在系统编程:

(a)将ByteBlaster电缆一端与微机并行口相连,另一端与实验箱的JTAG下载口相连。

并打开实验箱电源。

(b)选择系统主菜单Options中的HardwareSetup命令,将出现如下对话框,见图17。

在下拉条中选择ByteBlaster(MV),指定配置时使用的并行口LPT1,按下OK按钮。

(c)在编程器窗口中检查编程文件和目标器件型号是否正确。

如果选择的编程文件不正确,可在File菜单中单击SelectProgrammingFile选项来选择编程文件。

注意:

对于该型号器件配置(编程)文件的扩展名为“.sof”。

(d)将PLD器件插到编程插座中,单击Configure按钮。

硬件设置窗口

编程器窗口

图17

g、实验操作

按下F1按键,观察显示器显示结果。

增大或减小计数时钟频率,结果会发生什么变化?

五、实验预习

学习Max+plus2软件的基本操作,认真阅读实验指导书,弄清内容与要求,熟悉设计原理及设计流程,。

六、实验报告

(1)设计步骤;

(2)具体操作过程;

(3)逻辑仿真波形;

(4)实验结果;

(5)实验心得、体会及意见。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数码管 扫描 显示 电路 16

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx