msp430最全的指令集.docx

msp430最全的指令集.docx

- 文档编号:6855174

- 上传时间:2023-01-11

- 格式:DOCX

- 页数:15

- 大小:23.39KB

msp430最全的指令集.docx

《msp430最全的指令集.docx》由会员分享,可在线阅读,更多相关《msp430最全的指令集.docx(15页珍藏版)》请在冰豆网上搜索。

msp430最全的指令集

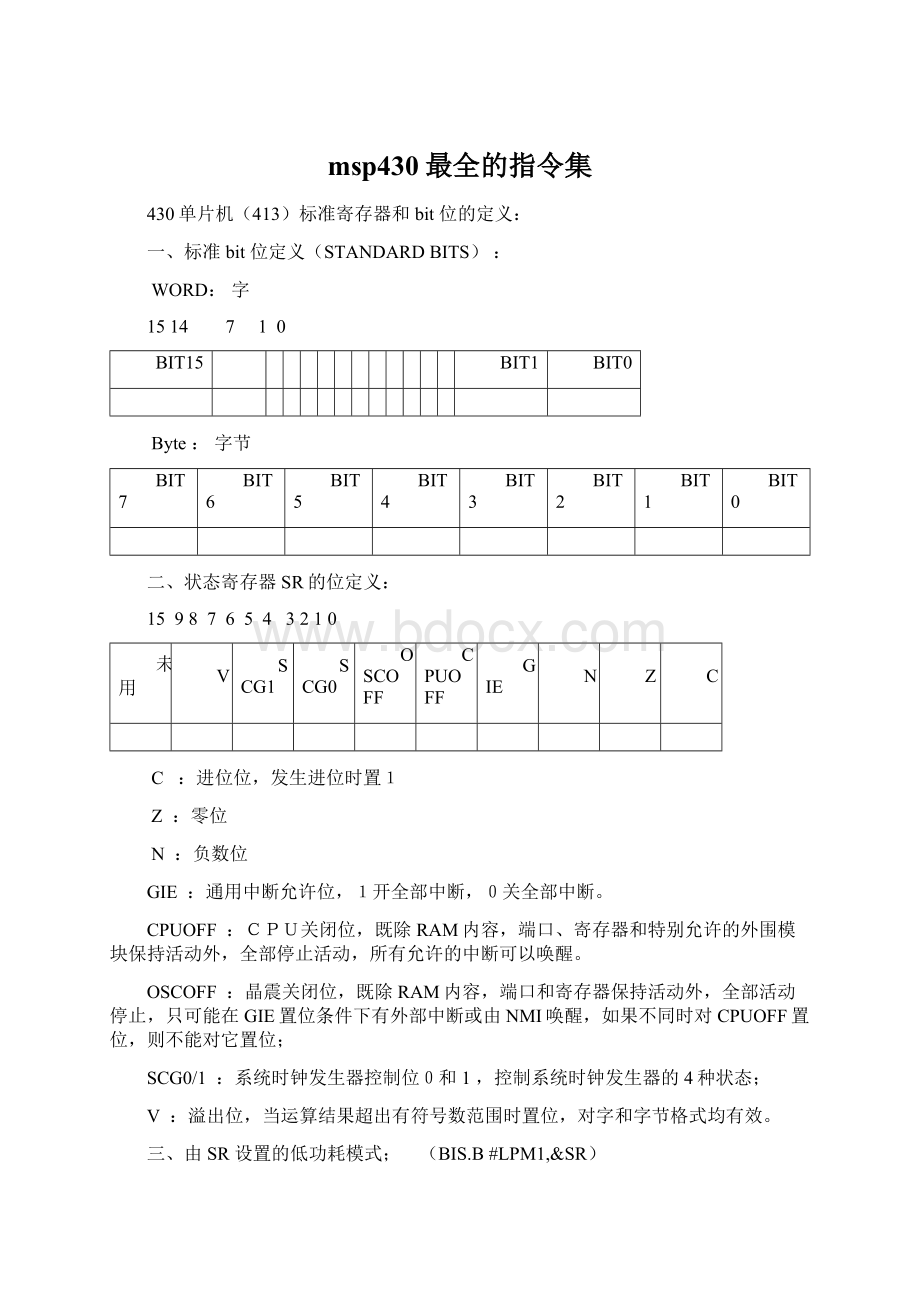

430单片机(413)标准寄存器和bit位的定义:

一、标准bit位定义(STANDARDBITS):

WORD:

字

1514710

BIT15

BIT1

BIT0

Byte:

字节

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

二、状态寄存器SR的位定义:

159876543210

未用

V

SCG1

SCG0

OSCOFF

CPUOFF

GIE

N

Z

C

C:

进位位,发生进位时置1

Z:

零位

N:

负数位

GIE:

通用中断允许位,1开全部中断,0关全部中断。

CPUOFF:

CPU关闭位,既除RAM内容,端口、寄存器和特别允许的外围模块保持活动外,全部停止活动,所有允许的中断可以唤醒。

OSCOFF:

晶震关闭位,既除RAM内容,端口和寄存器保持活动外,全部活动停止,只可能在GIE置位条件下有外部中断或由NMI唤醒,如果不同时对CPUOFF置位,则不能对它置位;

SCG0/1:

系统时钟发生器控制位0和1,控制系统时钟发生器的4种状态;

V:

溢出位,当运算结果超出有符号数范围时置位,对字和字节格式均有效。

三、由SR设置的低功耗模式; (BIS.B#LPM1,&SR)

#defineLPM0(CPUOFF)

#defineLPM1(SCG0+CPUOFF)

#defineLPM2(SCG1+CPUOFF)

#defineLPM3(SCG1+SCG0+CPUOFF)

#defineLPM4(SCG1+SCG0+OSCOFF+CPUOFF)

说明:

低功耗模式可以被允许的中断唤醒;

1)LPM0:

CPUOFF置位,不使外围模块停止运行。

ACLK,MCLK信号保持活动,MCLK可用于模块,FLL+锁相环保持活动。

2)LPM1:

CPU停止活动,MCLK可用于模块,FLL+锁相环关闭。

(SCG0控制)

3)LPM2:

CPU停止活动,ACLK保持活动,MCLK,DCO被禁止;

4)LPM3:

CPU停止活动,ACLK保持活动,MCLK,FLL+,DCO,DCOCLK被禁止。

5)LPM4:

CPU停止活动,ACLK关闭,MCLK,FLL+,DCO,DCOCLK被禁止。

四、SFR中断控制位;

大多数的中断允许集中在少数几个SFR中,这些SFR以字节形式在低地址空间区,只能以字节指令访问;

1)中断允许寄存器1:

IE1(0x0000)

ACCVIE

NMIIE

P0IE。

1

P0IE。

0

OFIE

WDTIE

中断标志寄存器1:

IFG1(0x0002)

NMIIFG

P0IFG。

1

P0IFG。

0

OFIFG

WDTIFG

WDTIE(0x01)看门狗定时器允许,选中看门狗模式时无效;

OFIE(0x02)震荡器故障中断允许;

P0IE。

0(0X04)I/OP0。

0(413没有)

P0IE。

1(0X08)I/OP0。

1(413没有)

NMIIE(0x10)

ACCVIE(0x20)

2)中断允许寄存器2:

IE2(0x0001)

BTIE

TPIE

ADIE/TPIE

UTXIE

URXIE

中断标志寄存器2:

IFG2(0x0003)

BTIFG

ADIFG

UTXIFG

URXIFG

URXIE(0x01)UASRT接受中断允许

UTXRIE(0x02)UASRT发送中断允许

ADIE/TPIE(0x04)ADC或定时器/端口中断允许(适合320)

TPIE(0x08)定时器/端口(适合310,330)

BTIE(0x80)BacicTime中断允许。

五、看门狗定时器(WATCHDOGTIMER)

1)看门狗定时器控制寄存器:

WDTCTL(0x0120)

HOLD

NMIES

NMI

TMSEL

CNTCL

SSEL

TIS1

TIS0

IS0,IS1:

选择WDCNT的输出,详细见下面:

SSEL:

选择WDTCNT的时钟源-----0:

系统时钟MCLK;1:

ACLK(晶震时钟)

CNTCL:

在两种模式中,写入1,是WDTCNT从00000H重启动;

TMSEL:

模式选择:

0:

看门狗模式;1:

定时器模式;

NMI:

选择RST/NMI引脚功能;0:

输入做复位用;1:

中断敏感的非屏蔽中断输入;

NMIES:

选择NMI的触发沿,0:

上升沿触发,1:

下降沿触发;

HOLD:

1-----看门狗的所有工作停止,0-----所有功能激活;

2)、WDT的定时时间:

(时钟为系统时钟:

CLK=1MHz)

WDT_MDLY_32(WDTPW+WDTTMSEL+WDTCNTCL)

WDT_MDLY_8(WDTPW+WDTTMSEL+WDTCNTCL+WDTIS0)WDT_MDLY_0_5(WDTPW+WDTTMSEL+WDTCNTCL+WDTIS1)

WDT_MDLY_0_064(WDTPW+WDTTMSEL+WDTCNTCL+WDTIS1+WDTIS0)

3)、WDT的定时时间:

(时钟为ACLK=32KHz)

WDT_ADLY_1000(WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL)

WDT_ADLY_250(WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS0)WDT_ADLY_16(WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS1)WDT_ADLY_1_9(WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS1+WDTIS0)

4)、WDTPW(0x5A00)

(1)WDT的时钟为MCLK=1MHz

WDT_MRST_32(WDTPW+WDTCNTCL)WDT_MRST_8(WDTPW+WDTCNTCL+WDTIS0)WDT_MRST_0_5(WDTPW+WDTCNTCL+WDTIS1)WDT_MRST_0_064(WDTPW+WDTCNTCL+WDTIS1+WDTIS0)

(2)WDT时钟为fACLK=32KHz

WDT_ARST_1000(WDTPW+WDTCNTCL+WDTSSEL)WDT_ARST_250(WDTPW+WDTCNTCL+WDTSSEL+WDTIS0)WDT_ARST_16(WDTPW+WDTCNTCL+WDTSSEL+WDTIS1)WDT_ARST_1_9(WDTPW+WDTCNTCL+WDTSSEL+WDTIS1+WDTIS0)

(3)对应的SFR中断位

#defineWDTIE0x01

#defineWDTIFG0x01

六、端口设置

1)、P1/P2口(I/OPort1/2)

#defineP1IN(0x0020)P1输入寄存器:

存放输入数据

#defineP1OUT(0x0021)P1输出寄存器:

存放输出数据

#defineP1DIR(0x0022)P1方向寄存器:

0:

输入,1:

输出

#defineP1IFG(0x0023)P1中断标志寄存器:

#defineP1IES(0x0024)P1中断触发沿选择寄存器:

0:

上升沿中断。

1:

下降沿中断;

#defineP1IE(0x0025)P1中断允许寄存器:

开放对应的中断0:

禁止,1:

开放

#defineP1SEL(0x0026)P1功能选择寄存器:

0:

端口功能,1:

模块功能;

P2口的定义从0X0028-----0X002E。

2)P3,P4,P5,P6口

#definePXIN输入寄存器:

存放输入数据

#definePXOUT输出寄存器:

存放输出数据

#definePXDIR方向寄存器:

0:

输入,1:

输出

#definePXSEL功能选择寄存器:

0:

端口功能,1:

模块功能

七、基本定时器:

BT

BTCTL控制寄存器040H

BTCNT1计数器1046H

BTCNT2计数器2047H

1)、控制寄存器BTCTL(0x0040)

SSEL

HOLD

DIV

FRFQ1

FRFQ0

IP2

IP1

IP0

IP0,IP1,IP2:

决定中断间隔时间,即BTIFG置位时间

FRFQ0:

选择flcd频率,

FRFQ1:

选择flcd频率,

DIV:

fCLK2=ACLK:

256

HOLD:

1:

停止BTCNT1工作,HOLD+DIV:

停止BTCNT2工作;

SSEL:

与DIV一起选择BTCNT2的输入频率;

BTCNT1(0x0046)/*BasicTimerCount1计数器1*/

BTCNT2(0x0047)/*BasicTimerCount2计数器2*/

对应的Byte位如下:

2e7

2e6

2e5

2e4

2e3

2e2

2e1

2e0

2)BT的设置(通过设置BTCTL的各位来设置)

BTCNT1:

对时钟ACLK分频;

BTCNT2:

对时钟频率分频,输入时钟可以是ACLK,MCLK或ACLK/256;

(1)、计数器2(BTCNT2)的输入频率设置

#defineBT_fCLK2_ACLK(0x00)f=ACLK

#defineBT_fCLK2_ACLK_DIV256(BTDIV)f=ACLK/256

#defineBT_fCLK2_MCLK(BTSSEL)f=MCLK

(2)、中断间隔时间的设置

#defineBT_fCLK2_DIV2(0x00)/*fINT=fCLK2:

2(default)*/

#defineBT_fCLK2_DIV4(BTIP0)/*fINT=fCLK2:

4*/

#defineBT_fCLK2_DIV8(BTIP1)/*fINT=fCLK2:

8*/

#defineBT_fCLK2_DIV16(BTIP1+BTIP0)/*fINT=fCLK2:

16*/

#defineBT_fCLK2_DIV32(BTIP2)/*fINT=fCLK2:

32*/

#defineBT_fCLK2_DIV64(BTIP2+BTIP0)/*fINT=fCLK2:

64*/

#defineBT_fCLK2_DIV128(BTIP2+BTIP1)/*fINT=fCLK2:

128*/

#defineBT_fCLK2_DIV256(BTIP2+BTIP1+BTIP0)/*fINT=fCLK2:

256*/

(3)当fBT=fACLK时LCD的驱动频率设置

#defineBT_fLCD_1K(0x00)/*fACLK:

32(default)*/

#defineBT_fLCD_512(BTFRFQ0)/*fACLK:

64*/

#defineBT_fLCD_256(BTFRFQ1)/*fACLK:

128*/

#defineBT_fLCD_128(BTFRFQ1+BTFRFQ0)/*fACLK:

256*/

(4)fBT=fMCLK时LCD的频率设置

#defineBT_fLCD_31K(BTSSEL)/*fMCLK:

32*/

#defineBT_fLCD_15_5K(BTSSEL+BTFRFQ0)/*fMCLK:

64*/

#defineBT_fLCD_7_8K(BTSSEL+BTFRFQ1+BTFRFQ0)/*fMCLK:

256*/

(5)fBT=fACLK时中断时间设置

#defineBT_ADLY_0_064(0x00)/*0.064msinterval(default)*/

#defineBT_ADLY_0_125(BTIP0)/*0.125ms"*/

#defineBT_ADLY_0_25(BTIP1)/*0.25ms"*/

#defineBT_ADLY_0_5(BTIP1+BTIP0)/*0.5ms"*/

#defineBT_ADLY_1(BTIP2)/*1ms"*/

#defineBT_ADLY_2(BTIP2+BTIP0)/*2ms"*/

#defineBT_ADLY_4(BTIP2+BTIP1)/*4ms"*/

#defineBT_ADLY_8(BTIP2+BTIP1+BTIP0)/*8ms"*/

#defineBT_ADLY_16(BTDIV)/*16ms"*/

#defineBT_ADLY_32(BTDIV+BTIP0)/*32ms"*/

#defineBT_ADLY_64(BTDIV+BTIP1)/*64ms"*/

#defineBT_ADLY_125(BTDIV+BTIP1+BTIP0)/*125ms"*/

#defineBT_ADLY_250(BTDIV+BTIP2)/*250ms"*/

#defineBT_ADLY_500(BTDIV+BTIP2+BTIP0)/*500ms"*/

#defineBT_ADLY_1000(BTDIV+BTIP2+BTIP1)/*1000ms"*/

#defineBT_ADLY_2000(BTDIV+BTIP2+BTIP1+BTIP0)/*2000ms"*/

(6)fBT=fMCLK(1MHz)中断时间设置

#defineBT_MDLY_0_002(BTSSEL)/*0.002msinterval#defineBT_MDLY_0_004(BTSSEL+BTIP0)/*0.004ms"#defineBT_MDLY_0_008(BTSSEL+BTIP1)/*0.008ms"#defineBT_MDLY_0_016(BTSSEL+BTIP1+BTIP0)/*0.016ms"#defineBT_MDLY_0_032(BTSSEL+BTIP2)/*0.032ms"*/

#defineBT_MDLY_0_064(BTSSEL+BTIP2+BTIP0)/*0.064ms"*/

#defineBT_MDLY_0_125(BTSSEL+BTIP2+BTIP1)/*0.125ms"*/

#defineBT_MDLY_0_25(BTSSEL+BTIP2+BTIP1+BTIP0)/*0.25ms"*/

(7)BT时钟选择/*Reset/HoldcodedwithBits6-7inBT

(1)CTL*/

#defineBTHOLD_CNT1(BTHOLD)停止BTCNT1工作,

#defineBTHOLD_CNT1_2(BTHOLD+BTDIV)停止BTCNT2工作;

(8)对应的SFR中断位和标志

#defineBTIE0x80*/

#defineBTIFG0x80*/

八、系统时钟FLL+(SYSTEMCLOCK,FLL+(x41x))

1)、相关的寄存器

SCFI0、SCFI1:

系统时钟频率积分器

SCFQCTL:

系统时钟频率控制寄存器

(1)系统时钟频率积分器0:

SCFI0(0x0050)

FN_8

FN_4

FN_3

FN_2

2*2

2e0

#defineFN_2(0x04)/*fDCOCLK=1.4-12MHz*/

#defineFN_3(0x08)/*fDCOCLK=2.2-17Mhz*/

#defineFN_4(0x10)/*fDCOCLK=3.2-25Mhz*/

#defineFN_8(0x20)/*fDCOCLK=5-40Mhz*/

#defineFLLD0(0x40)/*LoopDividerBit:

0*/

#defineFLLD1(0x80)/*LoopDividerBit:

1*/

#defineFLLD_1(0x00)/*MultiplySelectedLoopFreq.By1*/

#defineFLLD_2(0x40)/*MultiplySelectedLoopFreq.By2*/

#defineFLLD_4(0x80)/*MultiplySelectedLoopFreq.By4*/

#defineFLLD_8(0xC0)/*MultiplySelectedLoopFreq.By8*/

(2)系统时钟频率积分器1:

SCFI1(0x0051)

2e9

2e8

2e7

2e6

2e5

2e4

2e3

2e2

由SCF0和SCF1来控制DCO

NDCO=(X*2e9+X*2e8+X*2e7+X*2e6+X*2e5)

+(1-M)*(X*2e4+X*2e3+X*2e2+X*e1+X*2e0)

(3)系统时钟频率控制寄存器:

SCFQCTL(0x0052)

M

2e6

2e5

2e4

2e3

2e2

2e1

2e0

fMCLK=(X*2e6+X*2e5+X*2e4+X*2e3+X*2e2+X*e1+X*2e0+1)*ACLK

2)、系统时钟设置MCLK;(ACLK=32K通过对SCFQCTL来设置);(BIS.B#XXX,&SCFQCTL)

#defineSCFQ_32K(0x00)/*fMCLK=1*fACLK*/#defineSCFQ_64K(0x01)/*fMCLK="2"*fACLK*/#defineSCFQ_128K(0x03)/*fMCLK="4"*fACLK*/

#defineSCFQ_256K(0x07)/*fMCLK="8"*fACLK*/

#defineSCFQ_512K(0x0F)/*fMCLK="16"*fACLK*/

#defineSCFQ_1M(0x1F)/*fMCLK="32"*fACLK*/

#defineSCFQ_2M(0x3F)/*fMCLK="64"*fACLK*/

#defineSCFQ_4M(0x7F)/*fMCLK="128"*fACLK*/

#defineSCFQ_M(0x80)/*ModulationDisable*/

3)、锁相环设置FLL+

(1)、锁相环控制寄存器0:

FLL_CTL0(0x0053)

DCOPLUS

XTS_FLL

OSCCAP1

OSCCAP0

XT1OF

LFOF

DCOF

DCOF:

DCO停止位

LFOF:

低频模式下LFXT1震荡器失效位

XT1OF:

高频模式下LFXT1震荡器失效位

OSCCAP0:

有效晶体振荡器选择0

OSCCAP1:

有效晶体振荡器选择1

XTS_FLL:

LFXT1的模式选择:

0:

低频1:

高频

DCOPLUS:

DCO+使能位

相对的设置:

外接电容的设置:

通过OSCCAP0、OSCCAP1来设置

#defineXCAP0PF(0x00)/*XINCap=XOUTCap=0pf*/

#defineXCAP10PF(0x10)/*XINCap=XOUTCap=10pf*/

#defineXCAP14PF(0x20)/*XINCap=XOUTCap=14pf*/

#defineXCAP18PF(0x30)/*XINCap=XOUTCap=18pf*/

(2)锁相环控制寄存器1(FLL_CTL1)(0x0054)/*FLL+Control1*/

SMCLKOFF

XT2ON

SELM1

SELM0

SELS

FLL-DIV1

FLL-DIV0

#defineFLL_DIV0(0x01)/*FLL+DividePx.x/ACLK0*/

#defineFLL_DIV1(0x02)/*FLL+DividePx.x/ACLK1*/

对应的设置:

#defineFLL_DIV_1(0x00)/*FLL+DividePx.x/ACLKBy1*/

#defineFLL_DIV_2(0x01)/*FLL+DividePx.x/ACLKBy2*/

#defineFLL_DIV_4(0x02)/*FLL+DividePx.x/ACLKBy4*/

#defineFLL_DIV_8(0x03)/*FLL+DividePx.x/ACLKBy8*/

4)对应的SFR的中断位

#defineOFIFG0x02

#defineOFIE0x02

九、SVS

SVSCTL(0x0056)/*SVSControl*/

#defineSVSFG(0x01)/*SVSFlag*/

#defineSVSOP(0x02)/*SVSoutput(readonly)*/

#defineSVSON(0x04)/*SwitchestheSVSon/off*/

#definePORON(0x08)/*EnablePORGenerationifLowVoltage*/

#defineVLDON(0x10)

#defineVLDOFF(0x00)

#defineVLD_1_8V(0x10)

十一、TimerA3

1)寄存器:

TAIV(0x012E)中断向量寄存器

TACTL(0x0160)控制寄存器

CCTL0(0

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- msp430 指令

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx