数字电路教案阎石第三章逻辑门电路.docx

数字电路教案阎石第三章逻辑门电路.docx

- 文档编号:685050

- 上传时间:2022-10-12

- 格式:DOCX

- 页数:15

- 大小:320.43KB

数字电路教案阎石第三章逻辑门电路.docx

《数字电路教案阎石第三章逻辑门电路.docx》由会员分享,可在线阅读,更多相关《数字电路教案阎石第三章逻辑门电路.docx(15页珍藏版)》请在冰豆网上搜索。

数字电路教案阎石第三章逻辑门电路

第3章逻辑门电路

3.1概述

逻辑门电路:

用以实现基本和常用逻辑运算的电子电路。

简称门电路。

用逻辑1和o分别来

表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:

利用半导体开关元件的导通、截止(即开、关)两种工作状态。

在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路)。

另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

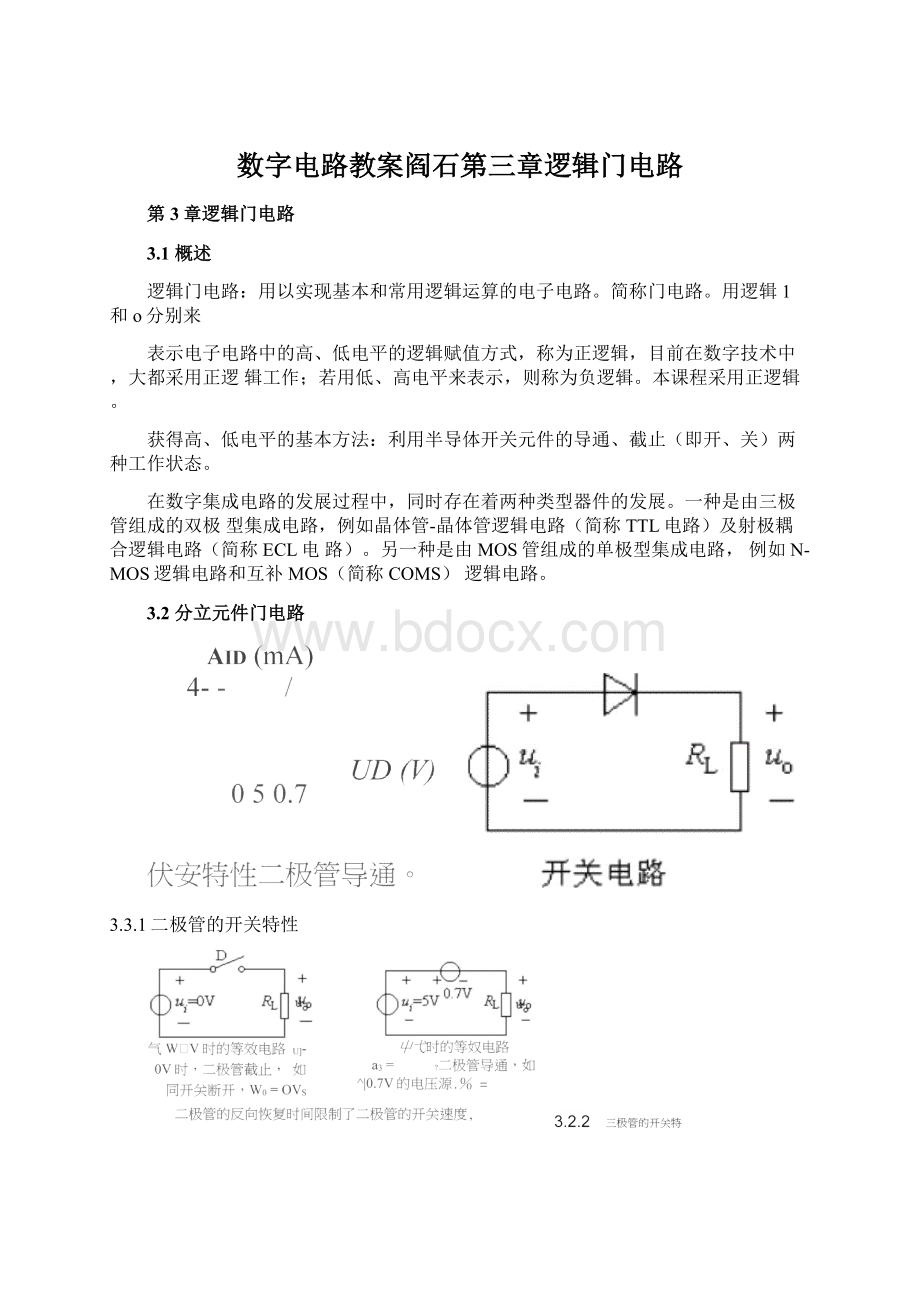

3.2分立元件门电路

3.3.1二极管的开关特性

性NPN型三极管截止、放大、饱和3种工作状态的特点

工作状态

截止

放大

饱和

条件

ib=0

0vib iB>Ibs 工 作 吐偏置情况 特 占 八、、 发射结反偏集电结反偏 UBE<0,UBC<0 发射结正偏 集电结反偏 UBE>0, ubc<0 发射结正偏集电结正偏 UBE>0,UBC>0 集电极电流 ic=0 iC=3iB ic=les ce间电压 uce=Vcc uce=Vcc— ieRc uce=UcES= 0.3V ce间等效电阻 很大,相当开关断开 可变 很小,相当开关闭 合 3.2.3二极管门电路1、二极管与门 輸入 输出 AB Y 00 0 01 0 10 0 11 1 5PIX1Zo—o—卫EV-JV5o % 及B 2 2 0V 0V 0.7V 导通 导通 0V 5V 0.7V 导通 截止 5V 0V 0.7V 截止 导通 5V 5V 5V 截止 截止 2、二极管或门 c~>1 Di °~°j n ¥只 丄3kQ Ua Ub Uy Di D2 0V 0V 0V 截止 截止 0V 5V 4.3V 截止 导通 5V 0V 4.3V 导通 截止 5V 5V 4.3V 导通 导通 3.2.4三极管非门 电路图逻辑符号 1 (Dua-OV时.三极管截止,rE=0,ic=0,输出电压wy=^c=5V ②细=5V时,三极管导通。 基极电流为' 5-0.7A’A it,=mA=1mA £4.3 3.2.5组合逻辑门电路 1与非门电路 A5■VrjV乡o 2、或非门电路 三极管临券饱和时的基极电流为' 5-0.3 30x1 016mA 怙〉』时三极管工作在饱和状态右输出电压旳=t^ES=0 A y 0 1 1 0 3.3集成逻辑门电路 一、TTL与非门 1、电路结构 °+fM+W) V1 (1)抗饱和三极管 作用: 使三极管工作在浅饱和状态。 因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。 构成: 在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称 SBD)。 特点: 开启电压低,其正向导通电压只有0.4V,比普通硅二极管0.7V的正向导通压降小得多;没有电荷存储效应;制造工艺和TTL电路的常规工艺相容,甚至无须增加工艺就可制造出SBD。 (2)采用有源泄放电路 上图中的V6、R3、R6组成。 2、TTL与非门的工作原理 (1)Vi的等效电路 Vi是多发射极三极管,其有三个发射结为PN结。 故输入级用 以实现A、B、C与的关系。 其等效电路如右图所示。 (2)工作原理分析 ①输入信号不全为1: 女口Ua=0.3V,ub=uc=3.6V 则Ubi=0.3+0.7=1V,T2、T5截止,T3>T4导通 忽略iB3,输出端的电位为: uy~5—0.7—0.7=3.6V 输出Y为高电平。 ②输入信号全为1: 如 ua=ub=uc3.6V 则ub1=2.1V,T2、T5导通, T4截止 输出端的电位为: uy=Uces=0.3V 输出Y为低电平。 功能 0.3V占□ 3.6VBo 3.6V匚0 Vi V ①输入信号不全为1 +JW+5V) Wy 0.3V0.3V 3.6V 0.3V3.6V 3,6V 36VOJV 3.6V 3.6V3.6V 0.3V 逻辑表达式: 真值表 0 1 1 1 0 1 1 丄 集成与非门电路引脚排列图(顶视) UiHmin~UiHmax=1.2〜5V;低电平UiLmin~UiLmax=0.2〜1.0V上述输入低电平中的最大值,即UoFF=UiLmax=1.0V。 U| 上述输入高电平中的最小值,即Uon=UiHmin=1.2V Ui>Uon时,与非门才开通,输出低电平。 工作在电压传输特性曲线转折区中点对应的输入电压称为阈值电压,又称为门槛电 (74LS00内含4个2输入与非门,74LS20 3、电压传输特性和噪声容限 (1)电压传输特性定义: 门电路输出电压Uo随输入电压变化的特性曲线称为电压传输特性。 (电压传输特性曲线见课本图3.3.3.) (2)概念输入电平范围: 高电平 •关门电平。 只有当输入 •开门电平。 只有当输入 •阈值电压。 压。 用UTH表示。 近似分析时,可以认为: 当UI ui>Uth时,与非门工作在开通状态,输出低电平Uol。 (3)噪声容限 在输入信号上叠加的噪声电压只要不超过允许值,就不会影响电路的正常逻辑功能,这个允许值称为噪声容限。 电路的噪声容限越大,其抗干扰能力就越强。 4、输入负载特性 定义: 输入电压Ui随输入端对地外接电阻Ri变化的曲线,称为输入负载特性。 在Ri上升到V和V开始导通时,Ui不能用上式进行计算。 当Ui上升到1.1V时,Vi的基极电压被钳在1.8V上,V2和V5导通,输出Uo为低电增Uol,此后,Ui不再随Ri的增大而升高。 Ui随Ri变化的曲线如上面右图所示。 •维持输出高电平的Ri最大值称为关门电阻,用Roff表示,其值约为700Qo •维持输出低电平的Ri最小值称为开门电阻,用Ron表示,其值约为2。 1KQ。 5、输出负载特性 输出电压uo随负载电流Io变化的特性曲线称为输出负载特性。 6、传输延迟时间 由于二极管、三极管由导通变为截止或由截止变为导通时,都需要一定的时间,再加上其它原因,输出电压u0的脉冲波形不仅比输入波形延迟了一定的时间,而且波形的上升沿和下降沿也都变坏了。 3.3.2低功耗肖特基系列 3.3.3其它功能的ttl门电路 TTL集成逻辑门电路除与非门外,常用的还有集电极开路与非门、或非门、与或非门、三态门和异或门等。 它们都是在上面所述的非门的基础上发展出来的。 1、集电极开路与非门(0C门) •电路结构与逻辑符号 •工作原理 1当EN=0时,二极管D截止,TSL门的输出状态完全取决于输入信号A、B的状态,电路 输出与输入的逻辑关系和一般与非门相同。 2当EN=1时,二极管D导通,一方面使Uc2=1V,V4截止;另一方面使Ubi=1V,从而使V2和v5截止。 输出端开路,电路处于高阻状态。 结论: 电路的输出有高阻态、高电平和低电平3种状态。 •三态输出门的应用(a)构成单向总线(b)构成双向总线TTL数字集成电路及主要参 数 TTL系列集成电路 174: 标准系列,前面介绍的TTL门电路都属于74系列,其典型电路与非门的平均传输时间tpd =10ns,平均功耗P=10mW。 274H: 高速系列,是在74系列基础上改进得到的,其典型电路与非门的平均传输时间tpd=6ns, 平均功耗P=22mW。 374S: 肖特基系列,是在74H系列基础上改进得到的,其典型电路与非门的平均传输时间tpd= 3ns,平均功耗P=19mW。 TTL与非门主要参数 (1)输出高电平UOH: TTL与非门的一个或几个输入为低电平时的输出电平。 产品规范值 UOH》2.4V,标准高电平Ush=2.4V。 (2)高电平输出电流IOH: 输出为高电平时,提供给外接负载的最大输出电流,超过此值会使输出高电平下降。 IOH表示电路的拉电流负载能力。 (3)输出低电平Uol: TTL与非门的输入全为高电平时的输出电平。 产品规范值UolW0.4V,标准低电平USL=0.4V。 (4)低电平输出电流IOL: 输出为低电平时,外接负载的最大输出电流,超过此值会使输出低电平上升。 IoL表示电路的灌电流负载能力。 (5)扇出系数No: 指一个门电路能带同类门的最大数目,它表示门电路的带负载能力。 一般TTL门电路NOA8,功率驱动门的NO可达25。 (6)最大工作频率fmax: 超过此频率电路就不能正常工作。 (7)输入开门电平Uon: 是在额定负载下使与非门的输出电平达到标准低电平Usl的输入电平。 它表示使与非门开通的最小输入电平。 一般TTL门电路的UON~1.8V。 (8)输入关门电平UOFF: 使与非门的输出电平达到标准高电平USH的输入电平。 它表示使与非 门关断所需的最大输入电平。 一般TTL门电路的UOF严0.8V。 (9)高电平输入电流l|H: 输入为高电平时的输入电流,也即当前级输出为高电平时,本级输入电 路造成的前级拉电流。 (10)低电平输入电流Iil: 输入为低电平时的输出电流,也即当前级输出为低电平时,本级输入电路造成的前级灌电流。 (11)平均传输时间tpd: 信号通过与非门时所需的平均延迟时间。 在工作频率较高的数字电路中,信号经过多级传输后造成的时间延迟,会影响电路的逻辑功能。 (12)空载功耗: 与非门空载时电源总电流Ice与电源电压Vec的乘积。 三、TTL集成电路逻辑门电路的使用注意事项 (1)关于电源等: 对于各种集成电路,使用时一定要在推荐的工作条件范围内,否则将导致性能下降或损坏器件。 (2)关于输入端: 数字集成电路中多余的输入端在不改变逻辑关系的前提下可以并联起来使用,也可根据逻辑关系的要求接地或接高电平。 TTL电路多余的输入端悬空表示输入为高电平(3)关于输出端: 具有推拉输出结构的TTL门电路的输出端不允许直接并联使用。 输出端不允许直接接电源Vee或直接接地。 3.4CMOS集成逻辑门电路 一、CMOS反相器 1、MOS管的符号 增强型NMOS管和增强型PMOS管的符号如右图所示: 漏极) 2、CMOS反相器 电路(助5截止、Tp导通eg导通、Tp截止 (1)UA=0V时,Tn截止,Tp导通。 输出电压Uy=Vdd=10V。 (2)uA=10V时,Tn导通,TP截止。 输出电压uY=0V。 、其它功能的CMOS电路CMOS

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电路 教案 第三 逻辑 门电路

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx