流水线加法器.docx

流水线加法器.docx

- 文档编号:6784720

- 上传时间:2023-01-10

- 格式:DOCX

- 页数:9

- 大小:69.25KB

流水线加法器.docx

《流水线加法器.docx》由会员分享,可在线阅读,更多相关《流水线加法器.docx(9页珍藏版)》请在冰豆网上搜索。

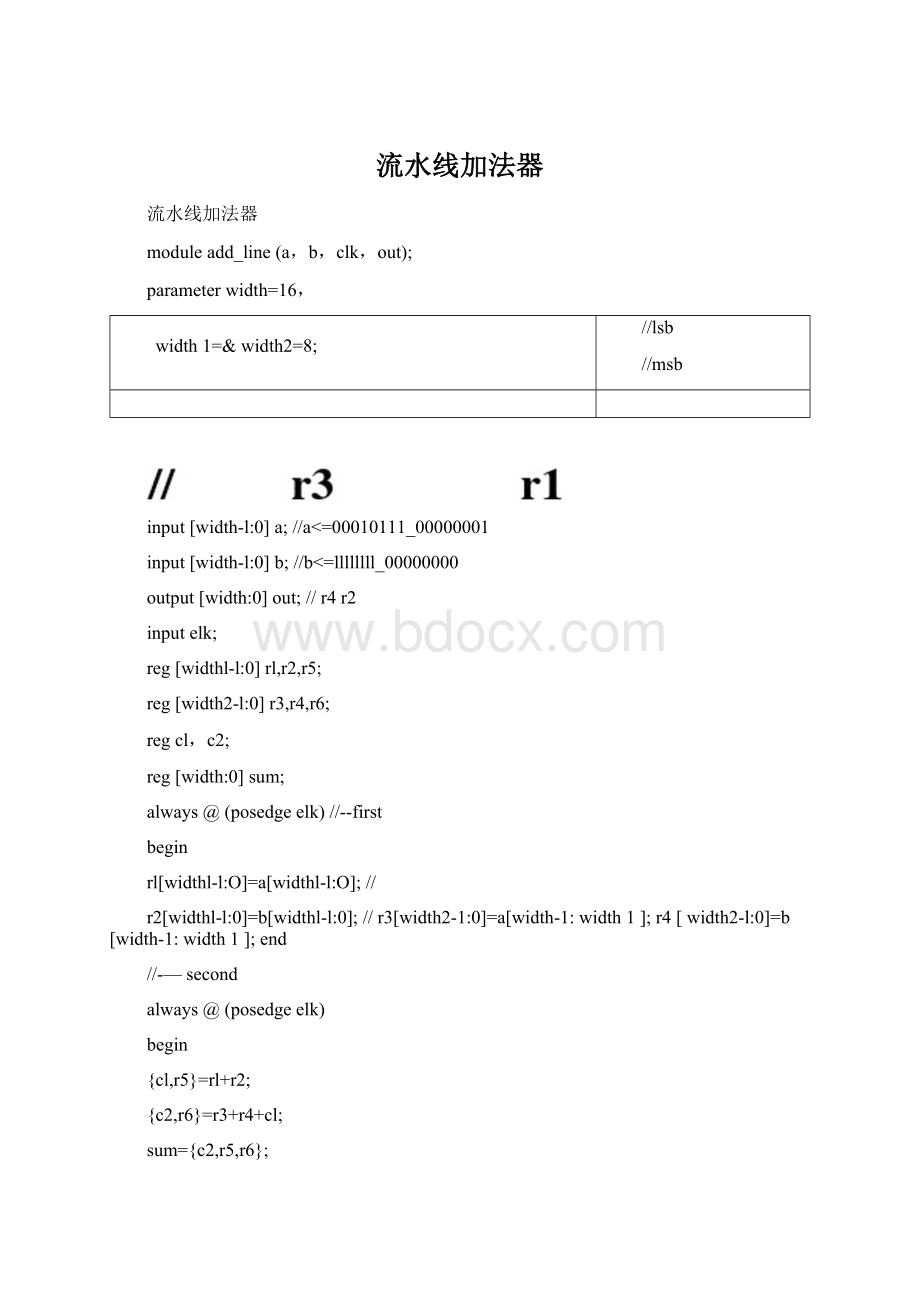

流水线加法器

流水线加法器

moduleadd_line(a,b,clk,out);

parameterwidth=16,

width1=&width2=8;

//lsb

//msb

input[width-l:

0]a;//a<=00010111_00000001

input[width-l:

0]b;//b<=llllllll_00000000

output[width:

0]out;//r4r2

inputelk;

reg[widthl-l:

0]rl,r2,r5;

reg[width2-l:

0]r3,r4,r6;

regcl,c2;

reg[width:

0]sum;

always@(posedgeelk)//--first

begin

rl[widthl-l:

O]=a[widthl-l:

O];//

r2[widthl-l:

0]=b[widthl-l:

0];//r3[width2-1:

0]=a[width-1:

width1];r4[width2-l:

0]=b[width-1:

width1];end

//-—second

always@(posedgeelk)

begin

{cl,r5}=rl+r2;

{c2,r6}=r3+r4+cl;

sum={c2,r5,r6};

end

assignout=sum;

endmodule

af15Oil—

clkl>

PFxE

PFxE

E\A

CLR

CLR

rno-

Add1

Add2

r4[7..O]

r4[7..O]

Ut[1f

bf15Oll~^

ENA

CLR

+

ADDER

ADDER

5:

30]

8h00-

PR£

□Q

>

E\A

CLR

r1[7..O]

r2[7..O]

AddO

ADDER

mF

rbO-

ADDER

b[15..0]|—>ari5oil~yclk(GND)>

I~ut口6-0

图II

上图II是没有assignout二sum;时的rtl级仿真结果;

错误1:

Warning(10034):

Outputportnout[l]natadd」ine.v(9)hasnodriver

原因:

out没有驱动,out根本就没有用;

错误2:

永远有多远(1057978105)10:

43:

30

这样不好有时序又有组合

永远有多远(1057978105)10:

46:

04

最好把它都放在时序里面width改成widthO

★(1003704680)10:

47:

54

那个地方是时序,哪个地方是组合

永远有多远(1057978105)10:

48:

17

always时序assign组合moduleadd_line(a,b,clk,out);

parameterwidth=16,

widthl=8,//lsb

width2=8;//msb

//r3rl

input[width-1:

0]a;

//a<=00010111_00000001

input[width-1:

0]b;

//b<=llllllll_00000000

output[width:

0]out;//r4r2

inputelk;

reg[widthl-l:

0]rl,r2,r5;reg[width2-l:

0]r3,r4,r6;

regcl,c2;

reg[width:

0]out;

always@(posedgeelk)

//-—first

begin

rl[widthl-l:

O]<=a[widthl-l:

0];//

0];//

r2[widthl-l:

0]<=b[widthl-l:

widthl];

r3[width2-l:

0]<=a[width-l:

widthl];

//-—second

r4[width2-1:

0]<=b[width-1:

endalways@(posedgeelk)

begin

{cl,r5}<=rl+r2;{c2,r6}<=r3+r4+cl;out<={c2,r5,r6};

end

endmodule

图皿

上图用阻塞赋值的Hl;

即.0]

4211

out[16.0卜regO

图IV

上图是用非阻塞赋值的rtl;

下图是用非阻塞赋值运算结果:

有两个地方进位错误!

第一个进位推迟一个时钟;

图V下图是用阻塞赋值结果:

鸟MasterlimeBar|SGTSreJjPohtei;

£.75reIrtavat

86.08nsSlait

End

A

)貼

2D.Ok

i

40.A阳心80.冷叫皿120pns

9氏

9.67

5is

J

0&

H0:

C031

0E2\0嘟X3

333\CGEEXEEEZ

0020

$11

闿b

H3E

3535

-X-

0030

"%

dk

A

1

nn

n

舟out

KCOi

0K0

:

(OzSffiXKST

\0359B):

m;(Q3923\12423);

OMCO

图VI

错误原因:

非阻塞赋值语句中,数值的转移须等到下一个时钟周期;

与组合逻辑的比较:

moduleadd(a,b9sum);

input[15:

0]a,b;output[16:

0]sum;

assignsum=a+b;

Endmodule

MasterlimeBar:

&675ns>|Panter:

57.12n$Interval:

57.45Start:

貝5C

Value

9.68

3ps10f)ns20.Qns30.Qns40Qns50.Qns60.Qns70Q

9.67

■

5ns

丿

亍0

Ha

□b

PlZUITi

H07

H疋

K03!

(0031

(0032乂0366X3333X03EEXEEFEX

G

3535X(

务31

(035

汨X03567~®0359BW068S3~■:

CBQ?

'厚12423*

图vn

所谓流水线设计实际上就是把规模较大、层次较多的组合逻辑电路分为几个级,在每一级插入寄存器组暂存中间数据。

K级的流水线就是从组合逻辑的输入到输出恰好有K个寄存器组(分为K级,每一级都有一个寄存器组)上一级的输出是下一级的输入而又无反

馈的电路。

图5・6表示了如何将把组合逻辑设计转换为相同组合逻辑功能的流水线设计。

这个组合逻辑包括两级。

第一级的延迟是T1和T3两个延迟中的最大值;第二级的延迟等于T2的延迟。

为了通过这个组合逻辑得到稳定的计算结果输出,需要等待的传播延迟为

[max(Tl,T3)+T2]个时间单位。

在从输入到输出的每一级插入寄存器后,流水线设计的第一级寄存器所具有的总的延迟为T1与T3时延中的最大值加上寄存器的Tc。

(触发时间)。

同样,第二级寄存器延迟为T2的时延加±Tcoo采用流水线设计为取得稳定的输出总体计算周期为:

max(max(Tl,T3)+Tco,(T2+Tco))

流水线设计需要两个时钟周期来获取第一个计的计算结果。

开始时用来获取第一个计算结果的两个时钟周期被称为采用流水线设计的首次延迟(latency)。

对于CPLD来说,器件的延迟如Tl、T2和T3相对于触发器的Teo要长得多,并且寄存器的建立时间Tsu也要比器件的延迟快得多。

只有在上述关于硬件时延的假设为真的情况下,流水线设计才能获得比同功能的组合逻辑设计更高的性能。

算结果,

而只需要一个时钟周

期来获取随后

釆用流水线设计的优势在于它能提高吞吐量(throughput)o假设Tl、T2和T3具有同样的传递延迟Tpd。

对于组合逻辑设计而言,总的延迟为2*Tpdo对于流水线设计来说,计算周期为(Tpd+Tco)o前面提及的首次延迟(latency)的概念实际上就是将(从输入到输出)最长的路径进行初始化所需要的时间总量;吞吐延迟则是执行一次重复性操作所需要的时间总量。

在组合逻辑设计中,首次延迟和吞吐延迟同为2*Tpdo与之相比,在流水线设计中,首次延迟是2*(Tpd+Tco),而吞吐延迟是Tpd+Tcoo如果CPLD硬件能提供快速的

Teo,则流水线设计相对于同样功能的组合逻辑设计能提供更大的吞吐量。

典型的富含寄存器资源的CPLD器件(如Lattice的ispLSI8840)的Tpd为8.5ns,Teo为6ns。

流水线设计在性能上的提高是以消耗较多的寄存器资源为代价的。

对于非常简单的用于数据传输的组合逻辑设计,例如上述例子,将它们

转换成流水线设计可能只需增加很少的寄存器单元。

随着组合逻辑变得复杂,为了保证中间的计算结果都在同一时钟周期内得到,必须在各级之间加入更多的寄存器。

如果需要在CPLD中实现复杂的流水线设计,以获取更优良的性能,具有丰富寄存器资源的CPLD结构并且具有可预测的延迟这两大特点的FPGA是一个很有吸引力的选择。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 流水线 加法器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx