数字电路实验要求.docx

数字电路实验要求.docx

- 文档编号:6742930

- 上传时间:2023-01-09

- 格式:DOCX

- 页数:9

- 大小:95.22KB

数字电路实验要求.docx

《数字电路实验要求.docx》由会员分享,可在线阅读,更多相关《数字电路实验要求.docx(9页珍藏版)》请在冰豆网上搜索。

数字电路实验要求

数字实验要求

实验一组合数字电路

一、实验目的

1.掌握组合数字电路的设计和实现方法。

2.掌握二进制译码器的原理与应用方法。

二、所用器件

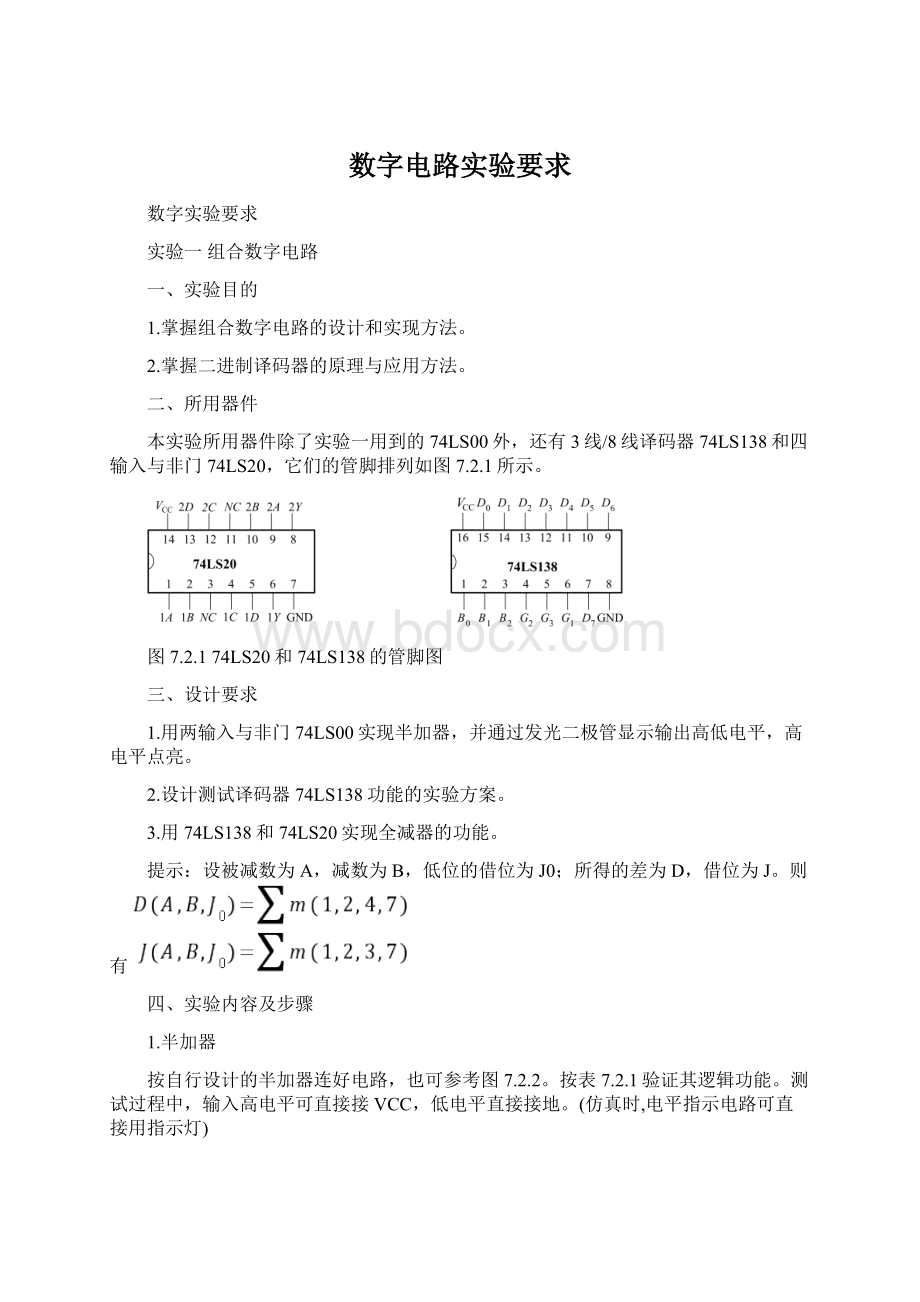

本实验所用器件除了实验一用到的74LS00外,还有3线/8线译码器74LS138和四输入与非门74LS20,它们的管脚排列如图7.2.1所示。

图7.2.174LS20和74LS138的管脚图

三、设计要求

1.用两输入与非门74LS00实现半加器,并通过发光二极管显示输出高低电平,高电平点亮。

2.设计测试译码器74LS138功能的实验方案。

3.用74LS138和74LS20实现全减器的功能。

提示:

设被减数为A,减数为B,低位的借位为J0;所得的差为D,借位为J。

则有

四、实验内容及步骤

1.半加器

按自行设计的半加器连好电路,也可参考图7.2.2。

按表7.2.1验证其逻辑功能。

测试过程中,输入高电平可直接接VCC,低电平直接接地。

(仿真时,电平指示电路可直接用指示灯)

图7.2.2半加器及输出电平指示电路

表7.2.1半加器真值表

A

B

S

C

0

0

0

1

1

0

1

1

2.74LS138功能测试

按表7.2.2验证74LS138功能,步骤自拟,并将你的验证过程在实验报告中加以简要说明。

表7.2.274LS138的功能表

输入

输出

G1G2+G3B2B1B0

H

L

HLLLL

HLLLH

HLLHL

HLLHH

HLHLL

HLHLH

HLHHL

HLHHH

HHHHHHHH

HHHHHHHH

LHHHHHHH

HLHHHHHH

HHLHHHHH

HHHLHHHH

HHHHLHHH

HHHHHLHH

HHHHHHLH

HHHHHHHL

3.用74LS138和74LS20实现的全加器的功能测试

接好实验电路,接上电源,测出真值表(用图7.2.2中的电平指示电路来显示输出)。

将结果填入表7.2.3中。

表7.2.3全减器功能测试表

输入

输出

A

B

J0

D

J

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

实验二数据选择器

一、实验目的

掌握数据选择器的功能和应用方法。

二、所用器件

双四选一数据选择器74LS253的管脚排列见图7.3.1。

图7.3.174LS253的管脚图

三、设计要求

1.用双四选一数据选择器74LS253和74LS00实现全加器。

四、实验内容及步骤

1.测试由数据选择器构成的全加器

参考电路如图7.3.2所示,图中控制端A1、A0为两个四选一数据选择器所共用,前面冠以“1”的为一个数据选择器的输入和输出端,冠以“2”的为另一个数据选择器。

A、B为被加数和加数,C0为低位来的进位,S为和,C1为向上一位的进位。

请按表7.3.1测试其功能(用图7.3.2中的电平指示电路来显示输出)。

图7.3.2由双四选一数据选择器构成的全加器

表7.3.1全加器功能测试表

输入

输出

A

B

C0

S

C1

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

实验三555定时器应用电路

一、实验目的

1.熟悉555定时器的工作原理。

2.掌握利用555定时器组成各种脉冲电路的方法。

二、所用器件

555集成定时器的管脚排列如图7.4.1所示。

三、设计要求

1.用555定时器设计一多谐振荡器,输出频

率为1kHz的方波。

2.用555定时器设计一单稳电路,暂稳态维

持时间约为0.7ms,考虑如何将该时间变为100ms。

图7.4.1555定时器的管脚图

四、实验内容及步骤

1.

施密特电路

由555定时器构成的施密特触发电路如图7.4.2所示。

在输入端加入正弦波(或三角波),用示波器的两个通道同时观察输入和输出的波形。

此时示波器的输入必须使用直流耦合方式。

测量两个触发电平,并计算回差电压。

此时若输出无波形,请检查输入信号的幅度,幅度必须大于

(为什么?

请在报告中说明)。

用示波器观察555定时器7脚的电压波形,与输出波形比较。

2.多谐振荡器图7.4.2施密特触发电路

图7.4.3(a)为用555电路组成的多谐振荡器,用示波器观察振荡器输出uo和电容上电压uC的波形,测量出输出脉冲的幅度Uom、周期T、频率f、占空比D,并与理论计算值比较。

测量uC的最小值和最大值,注意:

必须使用示波器的直流耦合方式。

该电路应保留,为后边单稳态电路提供输入。

3.单稳电路

用555定时器构成的单稳电路如图7.4.3(b)所示,ui为触发输入信号,可由多谐振荡器(图7.4.2(a))的输出引来。

用示波器同时观察ui和uC及ui和uo的波形,测出暂稳态的维持时间tw,并与理论计算值比较。

(a)(b)

图7.4.3555定时器构成的多谐振荡和单稳电路

实验四中规模计数器

一、实验目的

1.掌握中规模计数器74LS161和74LS90的功能。

2.熟悉中规模计数器的使用方法。

3.学会中规模计数器的变通应用方法。

二、所用器件

可预置的同步中规模2/16进制加法计数器74LS161和2-5分频异步2/10进制计数器74LS90,它们的管脚排列如图7.6.1所示。

图7.6.174LS90和74LS161的管脚图

三、设计要求

1.设计74LS90和74LS161功能的测试方法。

2.利用74LS161的预置数功能实现余三编码十进制计数器。

四、实验内容及步骤

1.74LS161的功能测试

按照表7.6.1测试74LS161的各项功能,并将结果填入表中。

表7.6.174LS161功能表

功能

输入

输出

CP

EP

ET

D

C

B

A

QD

QC

QB

QA

清零

0

×

×

×

×

×

×

×

×

预置

1

0

×

×

D

C

B

A

保持

1

1

×

×

×

×

计数

1

1

1

1

×

×

×

×

测试时,用实验中用数码管来指示计数器的输出,用电平指示电路指示进位信号RCO的有无,然后参考下列步骤进行测试。

(1)清“0”功能。

将

置为0态(直接接地即可),其他端任意(可暂时悬空),观察LED是否显示“0”。

(2)预置数功能。

令

=1(接VCC)、

=0时,将A、B、C、D置为几种不同的状态,加入手动单脉冲,观察显示的数据是否与预置的数相同。

(3)

计数和保持功能。

令

=

=EP=ET=1,将图7.4.3中手动单脉冲电路的输出接至CP,按动轻触开关,观察计数过程,在实验报告中画出状态转换图;同时注意观察何时出现进位信号。

在计数器的输出为某一状态时将EP或ET改接低电平,然后加手动脉冲,观察所发生的现象。

2.74LS161接成余三码十进制计数器

可参考图7.6.2所示电路,CP接手动单脉冲,观察电路的状态变化过程。

可以让电路从“0”态开始计数(利用

端先清零),加入手动单脉冲,直至计数器的状态出现循环为止。

3.74LS90功能测试图7.6.2余三码十进制计数器

按照表7.6.2测试74LS90的各项功能,并将结果填入表中。

表7.6.274LS90的功能表

功能

输入

输出

R01

R02

S91

S92

CPA

CPB

QD

QC

QB

QA

清零

1

1

×

×

×

×

置9

0

0

1

1

×

×

二分频

0

0

0

0

×

五分频

0

0

0

0

×

十进制计数器

0

0

0

0

QA

测试时,用用数码管来指示计数器的输出,然后参考下列步骤进行测试。

(1)清“0”功能。

将R01和R02置为“1”(直接接+5V即可),其他端任意(可暂时悬空),观察数码管是否显示“0”。

(2)置“9”功能。

令R01=R02=0,将S91和S92置为“1”(直接接+5V即可),观察显示的数据是否为“9”。

(3)二分频。

令R01=R02=S91=S92=0时,将图7.4.3中手动单脉冲电路的输出接至CPA,按动轻触开关,观察计数过程。

(4)五分频。

令R01=R02=S91=S92=0时,将图7.4.3中手动单脉冲电路的输出接至CPB,按动轻触开关,观察计数过程。

(5)十进制计数器。

令R01=R02=S91=S92=0时,将图7.4.3中手动单脉冲电路的输出接至CPA,CPB接QA,按动轻触开关,观察计数过程。

然后CPA接连续脉冲(从信号发生器获得),用示波器分别观察QA、QB、QC、QD对应CPA的波形,并用示波器的存储功能将五个波形全部显示在屏幕上。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电路 实验 要求

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx