实验调试中出现的问题.docx

实验调试中出现的问题.docx

- 文档编号:6726495

- 上传时间:2023-01-09

- 格式:DOCX

- 页数:10

- 大小:446.80KB

实验调试中出现的问题.docx

《实验调试中出现的问题.docx》由会员分享,可在线阅读,更多相关《实验调试中出现的问题.docx(10页珍藏版)》请在冰豆网上搜索。

实验调试中出现的问题

实验调试中出现的问题

一.Modelsim实验调试的问题

1.编译过程中的问题

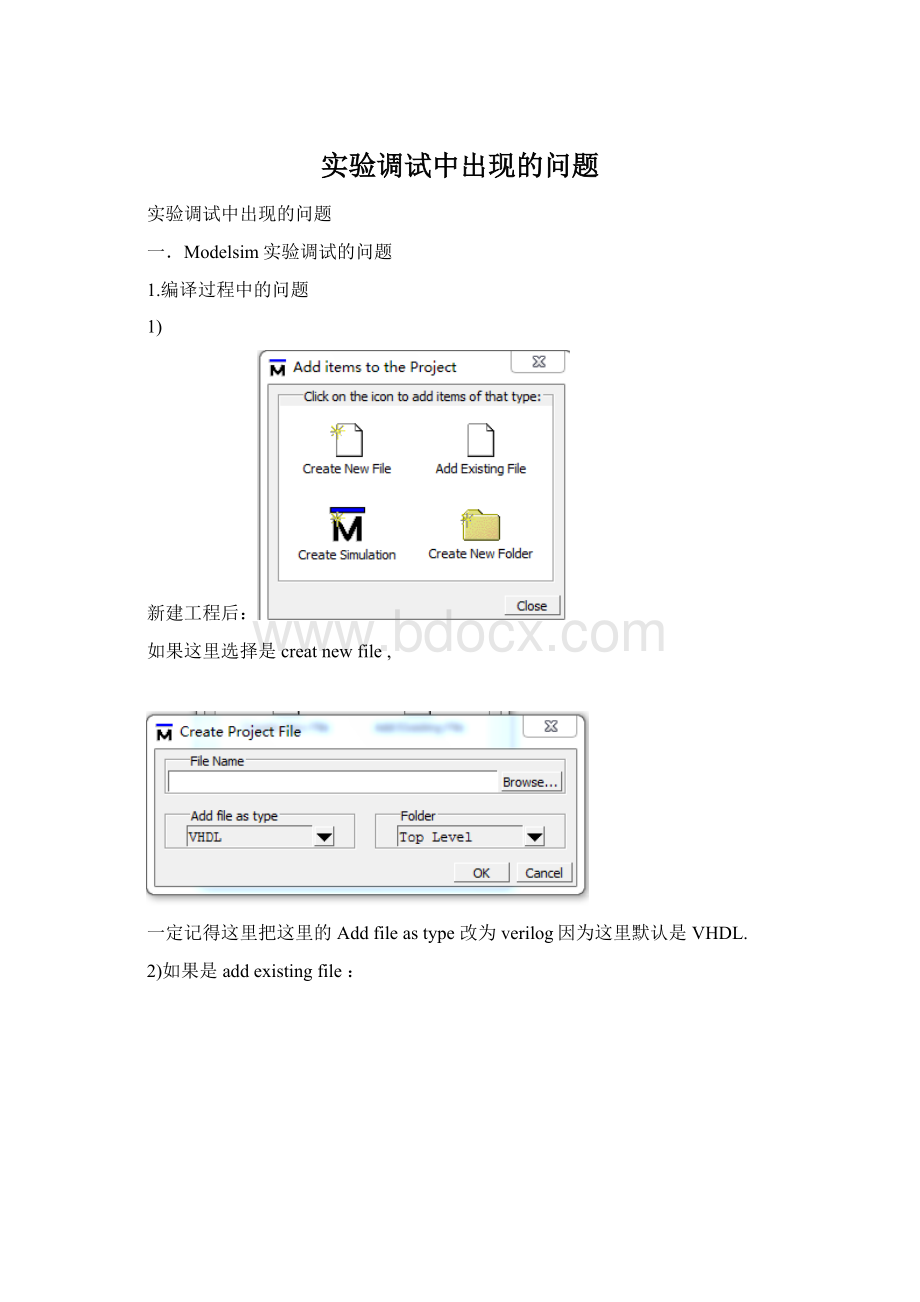

1)

新建工程后:

如果这里选择是creatnewfile,

一定记得这里把这里的Addfileastype改为verilog因为这里默认是VHDL.

2)如果是addexistingfile:

要把所有的工程文件,包括仿真文件放在projectlocation里面。

或者在下面的选项卡中:

选择copytoprojectdirectory!

!

注意了:

由于我们用的软件都是自己破解的,所有,有时候即便选择了copytoprojectdirectory有时候编译还是会出错,所有我们还是自己把工程文件,v拷贝到我们的工程目录中吧。

。

。

。

2.仿真中出现的问题:

当编译成功之后我们就可以进行仿真了

1)在仿真的时候有些版本的modelsim仿真出来的波形是直线

原因是

我们要注意把Optimization中的enableoptimization的选项取消了:

2)当我们编译成功之后在仿真的过程中,还会经常碰到这样的错误:

“#Errorloadingdesign”

解答:

loadingdesign的问题就是你对每个模块编译后的内容,也就是你在work库里出现的东西提示你加载设计错误,就是说明你加载的东西在work库里没有,这的问题的原因有两个:

(1)testbench没有写好

(2)在modelsim编译的时候相关的文件没有添加到modelsim中。

所以我们的对应的解决办法也有两个:

A.虽然我们编译通过了,但是可能有些字符拼写错误。

B.我们可以关掉软件,再重新打开重新编译,重新仿真。

3)仿真时遇到如图所示的情况:

不能看到全局时,可以通过工具栏里

这两个符号进行调节,结果如图:

上面问题虽然解决了,但是result结果却让人头疼,根本看不清是多少,此时,可以通过如下步骤把他修改成十进制数字,

效果如下图所示:

是不是可以看得很清楚了。

还可以修改字体的大小和颜色,通过如下步骤:

全选所有信号,右键选择“properties”,出现对话框(右边的图),可以在“View”栏里选择颜色,在“Format”栏选择字体大小,默认的是17,我们改成37之后,效果如图:

可以看得更加清楚。

二.synplify实验调试中出现的问题

1.第一个大问题就是大部分同学,不明确synplify到底是干什么的,在新建工程之后,当添加文件时竟然都把testbench也加入了工程中,导致run不通过!

解答:

Synplify、SynplifyPro和SynplifyPremier是Synplicity(Synopsys公司于2008年收购了Synplicity公司)公司提供的专门针对FPGA和CPLD实现的逻辑综合工具,Synplicity的工具涵盖了可编程逻辑器件(FPGAs、PLDs和CPLDs)的综合,验证,调试,物理综合及原型验证等领域。

2.synplify不能综合状态机的“default”状态:

编码风格中要求对case语句的使用要做到取值完全覆盖,用case来判断状态机的状态,然而用synplify综合时出warning:

OTHERSclauseisnotsynthesized,这里什么没有综合的原因是什么?

FSM分两大类:

米里型和摩尔型,组成要素有输入(包括复位),状态(包括当前状态的操作),状态转移条件,状态的输出条件,图1为状态机结构图。

设计FSM的方法和技巧多种多样,但是总结起来有两大类:

第一种,将状态转移和状态的操作和判断等写到一个模块中。

另一种是将状态转移单独写成一个模块,将状态的操作和判断等写到另一个模块中(在Verilog代码中,相当于使用两个“always”block)。

其中较好的方式是后者。

其原因如下:

首先FSM和其他设计一样,最好使用同步时序方式设计,好处不再赘述。

而状态机实现后,状态转移是用寄存器实现的,是同步时序部分。

状态的转移条件的判断是通过组合逻辑判断实现的,之所以第二种比第一种编码方式合理,就在于第二种编码将同步时序和组合逻辑分别放到不同的程序块中实现。

这样做的好处不仅仅是便于阅读、理解、维护,更重要的是利于综合器优化代码,利于用户添加合适的时序约束条件,利于布局布线器实现设计。

显式的FSM描述方法可以描述任意的FSM(参考Verilog第四版P181有限状态机的说明)。

两个always模块。

其中一个是时序模块,一个为组合逻辑。

时序模块设计与书上完全一致,表示状态转移,可分为同步与异步复位。

同步:

always@(posedgeclk)

if(!

reset)

…………

异步:

always@(posedgeclkornegedgereset)

if(!

reset)

…………

组合逻辑用case语句,sensitivelist包括当然状态(currentstate)和输入(a,b,c…)。

对于状态机的输出可以通过寄存器寄存一下,消除毛刺,这将另外需要一个always块,也就是状态机三个always块的写法。

编码风格:

1)参数定义用parameter

状态的定义用parameter定义,不推荐使用`define宏定义的方式,因为‘define宏定义在编译时自动替换整个设计中所定义的宏,而parameter仅仅定义模块内部的参数,定义的参数不会与模块外的其他状态机混淆。

2)时序电路中一定要使用”<=”非阻塞赋值方式

Verilog的非阻塞行赋值模拟的是实际硬件中串行寄存器的行为,排除了很多潜在的竞争冒险。

在使用非阻塞赋值的时候,很多设计者采用"intra-assignmenttimingdelay"(在非

3)Synplify中状态机设计:

可以在Synplify中添加在state定义时添加如下约束属性来限定状态机的编码:

reg[2:

0]state/*synthesissyn_encoding="onehot"*/;

Synplify中包含一个强大的FSM编辑器,可以产生在时间和面积上均得到优化的状态机设计,但这将忽略一些状态机中未定义的状态(invalidstate),如果必须在状态机进入了未定义的状态后能自动回到有效状态,可以在状态机生成时添加一个安全属性(safe),使得到达无效状态时能回到初始状态,这对电路的时间和面积产生很小的影响:

reg[2:

0]state/*synthesissyn_encoding="safe,onehot"*/;

这种方法可能与源代码中实际描述的不一致,对于大多数设计来说这不会产生问题,但如果必须与源代码中描述的状态机流程图相吻合,可以通过约束属性关掉FSM编辑器:

reg[4:

0]state/*synthesissyn_preserve=1*/;但这将严重影响电路的时间和面积特性。

2.synplify不能综合package库文件所以不要自己写一个用户库文件(),也有可能软件的原因,synplify忽略自定义库文件呢。

3.在生成technologyview的时候,一般生成的图片都比较大,如下所示,用截图工具一次截不完,其实这个软件自带有截图工具,很好用的。

选择File—>creatimage,就可以使用自带截图工具,结果如下图

可以选择保存位置和格式。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 实验 调试 出现 问题

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx