数字电子技术总复习3.docx

数字电子技术总复习3.docx

- 文档编号:6681626

- 上传时间:2023-01-08

- 格式:DOCX

- 页数:27

- 大小:371KB

数字电子技术总复习3.docx

《数字电子技术总复习3.docx》由会员分享,可在线阅读,更多相关《数字电子技术总复习3.docx(27页珍藏版)》请在冰豆网上搜索。

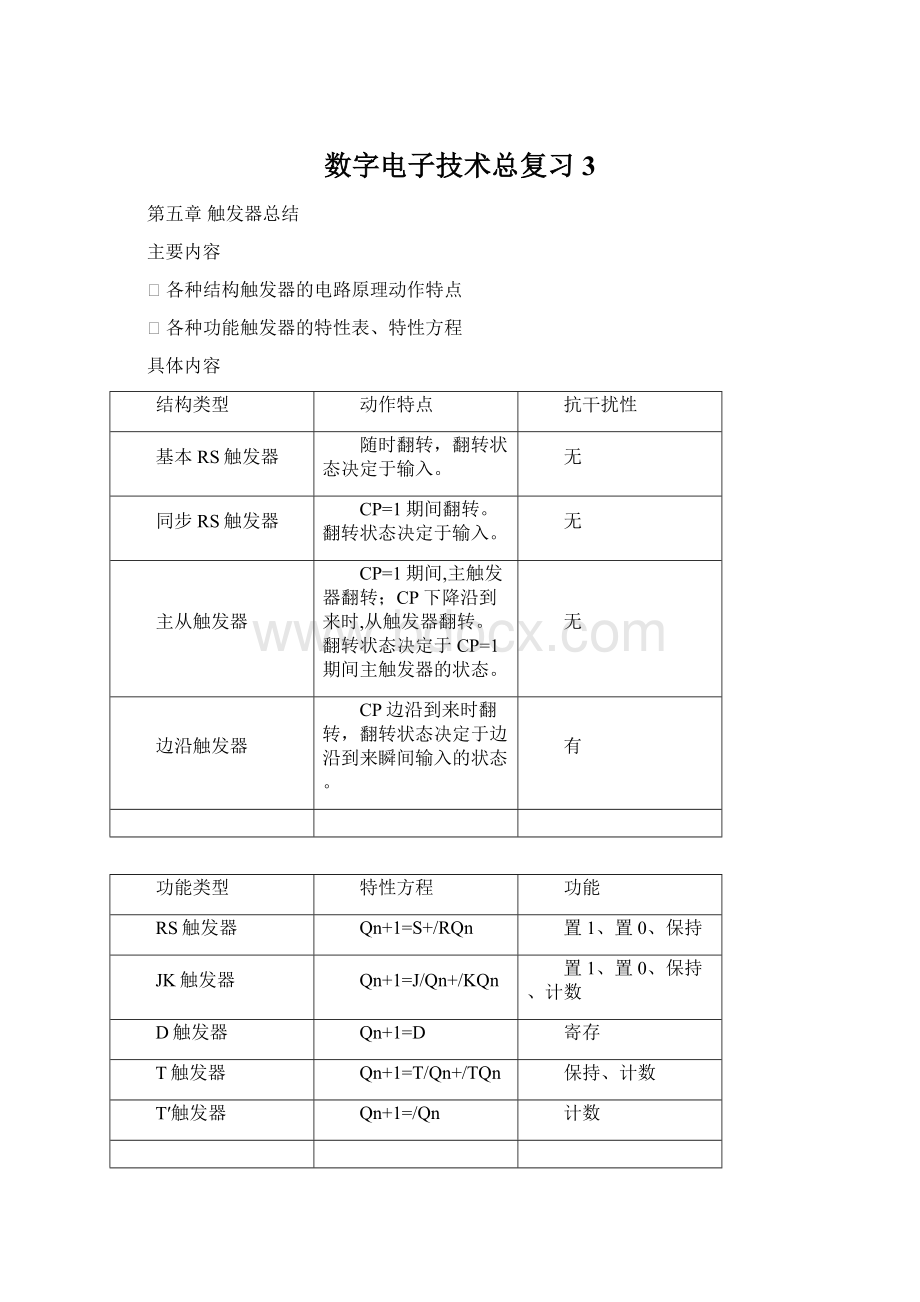

数字电子技术总复习3

第五章触发器总结

主要内容

Ø各种结构触发器的电路原理动作特点

Ø各种功能触发器的特性表、特性方程

具体内容

结构类型

动作特点

抗干扰性

基本RS触发器

随时翻转,翻转状态决定于输入。

无

同步RS触发器

CP=1期间翻转。

翻转状态决定于输入。

无

主从触发器

CP=1期间,主触发器翻转;CP下降沿到来时,从触发器翻转。

翻转状态决定于CP=1期间主触发器的状态。

无

边沿触发器

CP边沿到来时翻转,翻转状态决定于边沿到来瞬间输入的状态。

有

功能类型

特性方程

功能

RS触发器

Qn+1=S+/RQn

置1、置0、保持

JK触发器

Qn+1=J/Qn+/KQn

置1、置0、保持、计数

D触发器

Qn+1=D

寄存

T触发器

Qn+1=T/Qn+/TQn

保持、计数

T′触发器

Qn+1=/Qn

计数

如不作特别说明,在做习题时一律按边沿触发器的动作特点处理,若特别指明触发器结构,则按相应特点处理。

重点掌握

1.掌握各种触发器的动作特点

2.掌握各种触发器的功能

3.掌握各种触发器的特性方程、特性表

4.会分析触发器构成的电路(写出驱动方程,状态方程,输出方程,画波形)

思考题

1.N个触发器可以构成能寄存 B 位二进制数码的寄存器。

A.N-1 B.N C.N+1 D.2N

2.在下列触发器中,有约束条件的是 C 。

A.主从JKF/F B.主从DF/F C.同步RSF/F D.边沿DF/F

3.一个触发器可记录一位二进制代码,它有 C个稳态。

A.0 B.1 C.2 D.3 E.4

4.对于T触发器,若原态Qn=0,欲使新态Qn+1=1,应使输入T= BD 。

A.0 B.1 C.Q D.

5.对于JK触发器,若J=K,则可完成 C 触发器的逻辑功能。

A.RS B.D C.T D.Tˊ

6.欲使JK触发器按Qn+1=Qn工作,可使JK触发器的输入端 ABDE。

A.J=K=0 B.J=Q,K=0 C.J=1,K=Q` D.J=Q,K=0 E.J=0,K=Q`

7.描述触发器的逻辑功能的方法有ABCD 。

A.状态转换真值表B.特性方程C.状态转换图D.状态转换卡诺图

8.为实现将JK触发器转换为D触发器,应使 A 。

A.J=D,K=D` B.K=D,J=D` C.J=K=D D.J=K=D`

参考答案

1. B2. C3. C4. BD5. C6. ABDE7.ABCD8.A

思考题

1.触发器有两个互补的输出端Q、Q`,定义触发器的1状态为 ,0状态为 ,可见触发器的状态指的是 端的状态。

2.一个基本RS触发器在正常工作时,不允许输入R=S=1的信号,因此它的约束条件是 RS=0 。

3.在一个CP脉冲作用下,引起触发器两次或多次翻转的现象称为触发器的 空翻 ,触发方式为 主从 式或 边沿 式的触发器不会出现这种现象。

参考答案

1.Q=1、Q`=0 Q=0、Q`=1 Q2.RS=03.空翻 主从式 边沿式

思考题

画出下图所示时序电路在一系列CP信号作用下,Q1、Q2、Q3的输出电压波形。

触发器采用下降沿触发,初始状态为Q=0。

思考题

电路如图题所示,已知CP和A的波形,画出触发器Q0、Q1及输出VO的波形。

设触发器的初始状态均为0。

图题

Q0、Q1及输出VO的波形见图解。

图解

思考题

电路如图题所示,已知CP和X的波形,试画出Q0和Q1的波形。

设触发器的初始状态均为0。

图

解:

分析电路:

由

,J0=K0=1,得:

,此触发器构成计数状态。

又知

,当X=0时,

,当X=1时,

。

依据以上分析画出波形如图解5.12所示。

画图时要注意:

1.本题的两个触发器是下降沿触发的边沿触发器,所以Q0,Q1均在CP的下降沿翻转。

2.触发器的输出次态取决于下降沿触发前一瞬间的J、K,下降沿触发之后J、K的改变不会影响输出。

第六章时序电路总结

主要内容

Ø时序逻辑电路的分析方法

Ø常用的时序逻辑电路

Ø时序逻辑电路的设计方法

重点掌握

1.掌握同步、异步概念,掌握同步置数(清零)、异步置数(清零)的概念及特点

2.了解寄存器和移位寄存器的组成原理。

3.掌握移位寄存器74LS194的功能和使用方法

4.了解同步二进制计数器、十进制计数器,异步二进制计数器、十进制计数器的组成原理

5.掌握74LS161、74LS160、74LS191、74LS190、74290计数器的功能及使用方法(符号、真值表、管脚功能)

6.掌握任意进制计数器的构成方法及特点

7.掌握同步时序电路的分析方法

8.了解异步时序电路的分析方法

9.掌握同步时序逻辑电路的设计方法,会设计简单的时序电路

具体内容

寄存器

移位寄存器

组成原理

D触发器

①组成原理

D触发器,

或

②常用芯片

74LS194

直接清零,双向移位,保持,串行输入,并行输入,串行输出,并行输出

同步计数器

异步计数器

加法计数

二进制计数器

十进制计数器

二进制计数器

十进制计数器

1组成原理

T触发器,共CP

T′触发器

②常用芯片

二进制加法计数器74LS161

直接清零,同步预置数,保持,加法计数,进位

1组成原理

二进制修改十进制

2常用芯片

十进制加法计数器74LS160

直接清零,同步预置数,保持,加法计数

组成原理

T′触发器

(下降沿翻转)

①组成原理

二进制修改十进制

②常用芯片

二-五-十进制计数器74LS290

二、五、十进制计数,直接置零,直接置9,

减法计数

组成原理

T触发器,共CP

T′触发器

组成原理

T′触发器

(下降沿翻转)

可逆计数

单时钟

双时钟

①组成原理

由加法计数器和减法计数器合并而成,由加减控制端控制加减计数

②常用芯片

二进制加减计数器74LS191

异步预置数,保持,加减计数

十进制加减计数器74LS190

异步预置数,保持,加减计数

组成原理

由加法计数器和减法计数器合并而成,由时钟端控制加减计数

N进制

↓

M进制

M M>N 1复位法: 利用清零端,减去N-M个状态 ②置位法: 利用置数法,减去N-M个状态 级联+复位法、置位法 思考题 1.把一个五进制计数器与一个四进制计数器串联可得到 D 进制计数器。 A.4 B.5 C.9 D.20 2.下列逻辑电路中为时序逻辑电路的是 C 。 A.变量译码器 B.加法器 C.数码寄存器 D.数据选择器 3.N个触发器可以构成最大计数长度(进制数)为 D 的计数器。 A.N B.2N C.N2 D.2N 4.五个D触发器构成环形计数器,其计数长度为 A 。 A.5 B.10 C.25 D.32 5.同步时序电路和异步时序电路比较,其差异在于后者 B。 A.没有触发器 B.没有统一的时钟脉冲控制 C.没有稳定状态 D.输出只与内部状态有关 6.一位8421BCD码计数器至少需要 B 个触发器。 A.3 B.4 C.5 D.10 7.8位移位寄存器,串行输入时经 D个脉冲后,8位数码全部移入寄存器中。 A.1 B.2 C.4 D.8 8.某电视机水平-垂直扫描发生器需要一个分频器将31500HZ的脉冲转换为60HZ的脉冲,欲构成此分频器至少需要 A 个触发器。 A.10 B.60 C.525 D.31500 参考答案 1. D2. C3. D4. A5.B6. B7.D8.A 思考题 1.寄存器按照功能不同可分为两类: 移位 寄存器和 数码 寄存器。 2.数字电路按照是否有记忆功能通常可分为两类: 组合逻辑电路 、 时序逻辑电路 。 3.由四位移位寄存器构成的顺序脉冲发生器可产生 4 个顺序脉冲。 4.时序逻辑电路按照其触发器是否有统一的时钟控制分为 同步时序电路和 异步 时序电路。 参考答案 1. 移位 数码2. 组合逻辑电路 时序逻辑电路3. 44同步 异步 思考题 在图中所示的时序电路中,X为控制信号,Q1、Q2为输出信号,CP为一连续脉冲。 (1)画出其状态转换图。 说明电路的功能。 (2)说明电路的功能。 (1)状态方程为 (2)当X=0时,按二进制加法计数。 当X=1时,按二进制减法计数。 状态转换图: 思考题 图示电路是可变模值计数器。 试分析当控制变量X为1和为0时电路分别是几进制计数器。 解: X=1时: 当Q3Q2Q1Q0=1011 是11进制计数器 X=0时: 当Q3Q2Q1Q0=1001 是9进制计数器 思考题 试用4位同步二进制计数74LS161接成九进制计数器,可以加必要的门电路,74LS161的功能表如下: 附表174161功能表 CP EP ET D3 D2 D1 D0 Q3Q2Q1Q0 × × 0 × × × × × × × × 0000 ↑ 1 × 0 × × A B C D ABCD × 1 1 0 × × D0 × × × 保持 × 1 1××× × 0 × × × × ↑ 1 × 1 1 1 × × × × 计数 思考题 由集成四位二进制同步步计数器74161和8选1数据选择器74LS151组成的电路如图所示。 试按要求回答: (1)74161组成几进制计数器电路; (2)画出计数状态转换图; (3)写出输出Y的序列信号的一个周期; 解: (1)74161组成十进制计数器电路 (2)计数状态转换图如下 (3)F的序列周期取决于计数器高三位Q3Q2Q1的周期, 所以010*******,0101111101 思考题 用集成计数器160和8选1数据选择器设计信号发生器,使之在一系例CLK信号作用下周期性输出序列信号“0010110111”的系列信号。 例题、用D触发器和门电路设计一个11进制计数器,并检查能否自启动 解: 用四个维持阻塞型D触发器设计 (用下降沿触发的JK触发器,设计一个按自然序进行计数的同步七进制加法计数器) 思考题 用下降沿触发的D触发器设计同步时序电路,电路状态图如下图所示。 (要求写出设计过程) 000001011 100110111 解: 状态方程: 驱动方程: 输出方程: (用下降沿触发的JK触发器,设计一个按自然序进行计数的同步七进制加法计数器) 第六章脉冲波形的产生和整形总结 主要内容 Ø施密特触发器的原理、应用和参数 Ø单稳态触发器的原理、应用和参数 Ø多谐振荡器的原理、应用和参数 Ø555的结构、原理和应用 具体内容 电路 功能特点 几种电路形式 参数 分析方法 应用 施密特触发器 输入信号上升时和下降时的转换电平不同。 门电路构成的电路 集成施密特触发器 VT+,VT-,VT 整形 单稳态触发器 在输入触发脉冲的作用下,输出一定脉宽的脉冲 微分型电路 积分型电路 输出脉冲宽度tW 分析电路工作过程,画出波形,找出控制电压; 画出充放电等效电路,确定三要素; 计算时间 定时延迟 多谐 振荡器 输出周期性矩形脉冲 对称式 非对称式 施密特触发器加积分电路 振荡周期T 脉冲发生 555定时器①构成施密特触发器,将阈值端和触发端接在一起;②构成单稳态触发器: 触发器脉冲接触发端,电源和阈值端接电阻,阈值端和地之间接电容,放电管输出接阈值端;③构成多谐振荡器: 先接成施密特触发器,再加积分电路,注意反馈应从放电管输出端引回,并接上拉电阻。 重点掌握 1.掌握施密特触发器的工作原理及应用(会分析工作原理,会计算VT+、VT-、ΔVT参数,会分析其整形作用) 2.掌握微分型、积分型单稳态触发器的工作原理及应用(会分析工作原理,会画波形) 3.掌握多谐振荡器(对称、非对称、施密特构成)的工作原理及应用(会分析工作原理,会画波形) 4.掌握555定时器的内部结构,掌握由555定时器构成的施密特触发器、单稳态触发器、多谐振荡器的工作原理及参数计算(会分析电路、画波形、计算参数) 思考题 1.脉冲整形电路有 BC 。 A.多谐振荡器B.单稳态触发器C.施密特触发器D.555定时器 2.多谐振荡器可产生 B 。 A.正弦波 B.矩形脉冲 C.三角波 D.锯齿波 3.555定时器可以组成 ABC 。 A.多谐振荡器B.单稳态触发器C.施密特触发器D.JK触发器 4.用555定时器组成施密特触发器,当输入控制端CO外接10V电压时,回差电压为 B 。 A.3.33V B.5V C.6.66V D.10V 5.以下各电路中, B 可以产生脉冲定时。 A.多谐振荡器 B.单稳态触发器 C.施密特触发器 D.石英晶体多谐振荡器 参考答案 1.BC2.B3.ABC4.B5.B 思考题 1.施密特触发器具有 回差 现象,又称 电压滞后 特性;单稳触发器最重要的参数为 脉宽 。 2.常见的脉冲产生电路有 多学振荡器 ,常见的脉冲整形电路有 单稳态触发器 、 施密特触发器 。 3.为了实现高的频率稳定度,常采用 石英晶体 振荡器;单稳态触发器受到外触发时进入 暂稳态 态。 参考答案 1. 回差 电压滞后 脉宽 2. 多谐振荡器 单稳态触发器 施密特触发器 3. 石英晶体 暂稳态 思考题 在图9.24用555定时器接成的施密特触发器电路中,试求: (1)当VCC=12V,而且没有外接控制电压时,VT+、VT-及ΔVT值。 (2)当VCC=9V、外接控制电压VCO=5V时,VT+、VT-、ΔVT各为多少? 思考题 图题8.4为一通过可变电阻RW实现占空比调节的多谐振荡器,图中RW=RW1+RW2,试分析电路的工作原理,求振荡频率f和占空比q的表达式。 图题8.4 思考题五. 集成定时器CC7555的电路如图5.1(a)所示。 1.用该集成定时器及在规格为100kΩ,200kΩ,500kΩ的电阻,0.01μF,0.1μF,1μF电容器中选择合适的电阻和电容,设计一个满足图5.1(b)所求波形的单稳态触发器。 2. 用该集成定时器设计一个斯密特触发器,画出斯密特触发器的电路图。 当输入为图5.2所示的波形时,画出斯密特触发器的输出u0波形 (a)(b) 图5.1 1.要实现的单稳态触发器用框图表示如下: (8分图4分R、C参考各2分) 2.斯密特触发器如图,波形如右图(7分)图4分波形3分 第七章半导体存储器总结 主要内容 Ø各种半导体存储器的原理和特点 Ø存储器的扩展 Ø用存储器实现组合逻辑电路 具体内容 各种存储器及其特点 只读存储器ROM 在正常工作时 只能读不能写; 掉电不丢失 掩模ROM 由集成芯片厂家写入数据,不可更改 PROM 由用户一次性写入,不可更改 EPROM 可紫外线擦除,可写入。 EEPROM 可电擦除,可写入。 快闪存储器 可电擦除,可写入,集成度高。 随机存储器RAM 可随机读写; 掉电丢失 静态RAM 速度快,集成度低 动态RAM 速度慢,集成度高 存储器扩展: 位扩展,将地址线、片选线、读写线对应并接。 字扩展,将地址线、数据线、读写线对应并接,高位地址线经译码器输出接各片片选端,原地址线作低位地址。 用ROM实现组合逻辑: 列出真值表,地址线接输入变量,数据线接输出变量,根据真值表确定存储矩阵的点阵图。 重点掌握 1.了解各种存储器的结构及工作原理 2.掌握各种存储器的特点 3.掌握存储器的扩展方法 4.掌握用ROM实现组合逻辑电路的方法 思考题 1.一个容量为1K×8的存储器有 BD 个存储单元。 A.8 B.8K C.8000 D.8192 2.要构成容量为4K×8的RAM,需要 D 片容量为256×4的RAM。 A.2 B.4 C.8 D.32 3.寻址容量为16K×8的RAM需要 C 根地址线。 A.4 B.8 C.14 D.16 E.16K 4.随机存取存储器具有 A 功能。 A.读/写 B.无读/写 C.只读 D.只写 5.欲将容量为256×1的RAM扩展为1024×8,则需要控制各片选端的辅助译码器的输入端数为 B 。 A.4 B.2 C.3 D.8 6.只读存储器ROM在运行时具有 A 功能。 A.读/无写B.无读/写 C.读/写 D.无读/无写 7.只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容 D 。 A.全部改变B.全部为0 C.不可预料 D.保持不变 8.PROM的与陈列(地址译码器)是 B 。 A.全译码可编程阵列 B.全译码不可编程阵列 C.非全译码可编程阵列 D.非全译码不可编程阵列 参考答案 1. BD2. D3. C4. A5. B6.A7.D8.B 思考题. 图6.1是一个16×4位的ROM,A3A2A1A0为地址输入,D3D2D1D0的数据输出。 若将D3、D2、D1、D0视为A3、A2、A1、A0的逻辑函数,试写出D3、D2、D1、D0的逻辑函数式。 图6.1 思考题 用16×4位EPROM实现下列各逻辑函数,画出存储矩阵的连线图。 解: 16×4位EPROM有四个地址输入端和四个数据输出端,可以实现四输入变量、四输出变量的逻辑函数。 1.将逻辑函数展开为ABCD四变量逻辑函数的最小项表达式: 2.画出存储矩阵的连线图: ABCD四输入变量由EPROM的地址端输入,Y1Y2Y3Y4四输出变量由EPROM的数据输出端引出。 EPROM的与门阵列是固定的,或门阵列是可编程的,根据以上各式对或门阵列编程: 表达式中包含的最小项,在或门阵列相应的位置上画点,否则不画。 具体连线图如图解7.6所示。 此电路即可实现本题要求的逻辑函数。 图解7.6 第八章数模、模数转换电路总结 主要内容 D/A转换器的原理和特点 A/D转换器的原理和特点 具体内容 1、A/D和D/A在数字系统中的作用与分类。 2、D/A转换器: 权电阻网络DAC,倒T型电阻网络DAC,权电流型DAC,具有双极型输出的DAC。 DAC的转换精度与速度。 3、A/D转换器: 基本原理,转换步骤,取样定理,取样—保持电路,直接ADC,间接ADC。 ADC的转换精度与速度。 重点掌握 1.几种典型转换电路的基本工作原理, 2.输入量和输出量之间的定量关系、主要特点, 3.转换精度和转换速度的概念与表示方法。 思考题 1.一个无符号8位数字量输入的DAC,其分辨率为 位。 A.1 B.3 C.4 D.8 2.一个无符号10位数字输入的DAC,其输出电平的级数为 。 A.4 B.10 C.1024 D.210 3.4位倒T型电阻网络DAC的电阻网络的电阻取值有 种。 A.1 B.2 C.4 D.8 4.将一个时间上连续变化的模拟量转换为时间上断续(离散)的模拟量的过程称为 。 A.采样 B.量化 C.保持 D.编码 5.用二进制码表示指定离散电平的过程称为 。 A.采样 B.量化 C.保持 D.编码 6.将幅值上、时间上离散的阶梯电平统一归并到最邻近的指定电平的过程称为 。 A.采样 B.量化 C.保持 D.编码 7.以下四种转换器, 是A/D转换器且转换速度最高。 A.并联比较型 B.逐次逼近型 C.双积分型 D.施密特触发器 参考答案 1. D2. CD3. B4. A5. D6. B7.A 思考题 在10位二进制数D/A转换器中,已知其最大满刻度输出模拟电压Vom=5V,求最小分辨电压VLSB和分辨率。 解最小分辨电压: 5mV,分辨率: 。 思考题 在某双积分型A/D转换器中,计数器为十进制计数器,其最大计数容量为(3000)D。 已知计数时钟频率fcp=30kHz,积分器中R=100kΩ,C=1μF,输入电压vI的变化范围为0~5V。 试求: (1)第一次积分时间T1; (2)求积分器的最大输出电压|VOmax|; (3)当VREF=10V,第二次积分计数器计数值λ=(1500)10时,输入电压vI的平均值为多少? 解: (1)第一次积分时间是固定的,它应该是计数器计满(3000)D时所对应的时间: (2)第一次积分时: 当t=T1=0.1s时,得Vo的最大值|VOmax|。 (3)由第一次积分得: 第二次积分: T=T2时,Vo=0,得: 将T2=λTCP代入,得: 思考题. 由555定时器,三位二进制加计数器,理想运算放大器A构成如图所示电路。 设计数器初始状态为000,且输出低电平VOL=0

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 电子技术 复习

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx