调制直接数字频率合成器系统中英文.docx

调制直接数字频率合成器系统中英文.docx

- 文档编号:6445595

- 上传时间:2023-01-06

- 格式:DOCX

- 页数:22

- 大小:173.92KB

调制直接数字频率合成器系统中英文.docx

《调制直接数字频率合成器系统中英文.docx》由会员分享,可在线阅读,更多相关《调制直接数字频率合成器系统中英文.docx(22页珍藏版)》请在冰豆网上搜索。

调制直接数字频率合成器系统中英文

中文翻译1:

调制直接数字频率合成器系统

DDS(直接数字频率合成)总的介绍:

在探讨许多复杂的相位连续的调制技术中,对模拟电路中输出波形的控制已经越来越困难。

在这些设计中,使用非线性数字式设计消去电路板需要的调整额外输出和温度。

一种适合这个目标的数字式设计就是直接数字频率合成器(DDS)。

一个DDS系统仅仅使用一个恒定参考时钟输入和将该时钟分解为指定的量化数位频率输出或者对参考时钟频率取样。

这种形式频率控制使得DDS系统成为需要精确频率扫描比如雷达尖叫声或者快速频率计数器的理想系统。

根据数字输入控制字以控制输出频率,DDS系统可以用来当作一个允许精确频率连续改变相位的锁相环(PLL)。

根据后面的说明,我们知道DDS系统还可以使用输入数字相位控制字来控制输出载波的相位。

用数字式控制载波相位,很容易产生一个高频谱密度的相位调制载波。

本文主旨是给读者一个基本的DDS设计和寄生输出响应的知识。

本文将展示一个运行于45MHz的快速现场可编辑逻辑器件。

DDS系统框图:

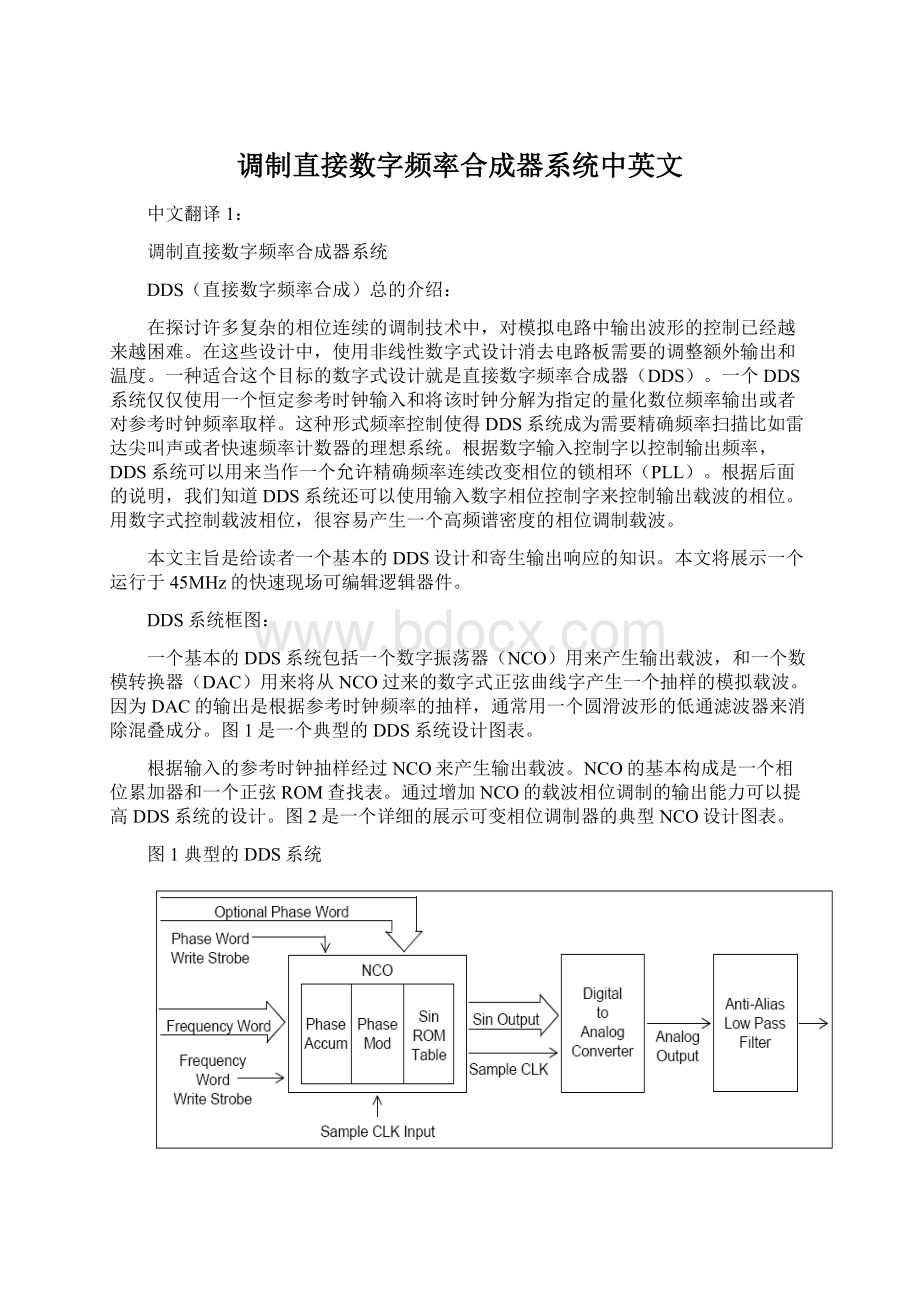

一个基本的DDS系统包括一个数字振荡器(NCO)用来产生输出载波,和一个数模转换器(DAC)用来将从NCO过来的数字式正弦曲线字产生一个抽样的模拟载波。

因为DAC的输出是根据参考时钟频率的抽样,通常用一个圆滑波形的低通滤波器来消除混叠成分。

图1是一个典型的DDS系统设计图表。

根据输入的参考时钟抽样经过NCO来产生输出载波。

NCO的基本构成是一个相位累加器和一个正弦ROM查找表。

通过增加NCO的载波相位调制的输出能力可以提高DDS系统的设计。

图2是一个详细的展示可变相位调制器的典型NCO设计图表。

图1典型的DDS系统

图2典型的NCO设计

为了更好的理解NCO设计的各种功能,首先考虑仅包括一个相位累加器和一个正弦ROM查找表的基本NCO设计。

与欧拉公式(

)图解比较就能最好地去理解这两个表的NCO设计的功能。

欧拉公式的图解如图3所示,是一个单位向量绕着实轴和虚平面的中心以Wrad/s的速度转圈。

这个频率控制字是最后一个抽样相位值通过一个N位加法器的连续地累加而成。

加法器的输出是参考抽样时钟通过一个N位寄存器的抽样。

当累加器达到N位最大值的时候,累加器翻转然后继续。

画出抽样累加器的值对时间的关系正如图3所示的一个锯齿波。

这里Troll是旋转的相位累加量,Fout是DDS系统输出频率,Fclk是时钟采样频率,FW(N-1:

0)是输入的总量,FW(N-1:

0)/2N是输入间隔量。

然后相位累加器的抽样输出用来在一个正弦量化值表里进行查找。

抽样相位到正弦量化的转化可以看作是真实的或者虚拟的成分及时地影射。

因为相位累加器的比特位数决定了频率调整的步进,一个典型的相位累加器的大小是24到32位。

由于正弦ROM表的大小是跟寻址范围直接成比例的,因此,不是所有相位累加器的24或32位都用来作为正弦ROM表的地址。

仅是相位累加器的高Y(Y〈N)位是用来作为正弦ROM表的地址,Y通常不必要等于正弦ROM表的输出量位D。

图3欧拉公式表征图解

DDS设计事项

因为一个NCO输出基于一个数字表示的相位和正弦波量化形式的载波,所以设计者可以完全的控制输出载波的频率、相位和幅度。

通过加入一个相位端口和一个相位加法器到一个基本的NCO设计中,NCO的输出载波当M等于相位端口数和M小于或等于Y(用来作为正弦ROM表的地址位数)时可以被M矩阵相位调制。

假如系统设计需要幅度调制如QAM,可以加入一个量化端口来调整正弦ROM表的输出。

注意到这个端口没有在图2里表示出来以及这个特色没有在简单的快速逻辑FPGA设计中论证。

最后,频率是调制是一个基本的NCO设计给出的。

因为频率控制字是跟抽样时钟是同步装载到DDS的,频率的转化是相位连续的。

虽然DDS系统给设计者完全地控制复杂的调制合成,但是在一个非线性数字格式的正弦相位和量级的表示却是复杂的新设计。

在取样任何的连续时间信号时,必须考虑取样原理和量子化误差。

为了理解DDS系统中取样理论的效果,最好看一下时间和频率域的DDS合成过程。

就象上面规定的,通过以指定的速率累积的形式由NCO产生一个正弦波然后用一个相位的值来定位一个正弦调制ROM表的值。

因此,NCO本质上用一个正弦波和用NCO的上升或下降沿输出参考取样时钟对其取样。

图4表示在时间和频率域里NCO的处理。

注意到这个表示并非量子化假设。

基于频率控制字的装载,NCO在一个时期内提供一批幅度的输出值。

这个正弦曲线的频率域表示在指定的频率里是一个推动的作用。

NCO在NCO参考时钟速率下输出这个正弦曲线的离散数字取样。

在时间域里,NCO输出是一个取样时钟边缘闸门乘于正弦波形式产生的一个推动序列正弦振幅的作用。

在频率域里,参考时钟的取样产生一系列在K倍的NCO时钟频率脉冲(当K=...-1,2,1,2....)。

当在时间域里取样时钟乘于正弦曲线,正弦曲线频率域成分和取样时钟需要卷积来产生NCO输出频率域表示的NCO输出。

频率域的结果是在正弦曲线基本频率的脉冲作用和别的脉冲作用发生在K倍的NCO时钟频率加上或减去基本频率。

基本的和别的成分发生在:

K*Fclk-Fout

K*Fclk+Fout

当K=...-1,0,1,2.....和K=0是NCO正弦曲线基本频率。

Fout是指定的NCO正弦曲线输出频率

Fclk是NCO参考时钟频率

图4NCO输出的时域和频域表示

DDS系统中的DAC提取NCO的输出值并转化他们的值为模拟电压。

图4显示出时间和频率域DAC过程开始于NCO的输出的表示。

DAC输出是一个抽样和保持那些NCO数字幅度控制字和转换那些值为一个模拟电压和保持那些值为一个抽样时钟周期的电路。

DAC过程的时域结构是NCO抽样输出值和一个抽样周期脉冲的卷积。

抽样脉冲的频率域结构是一个sin(x)/x功能和在抽样时钟频率的第一个零。

因为时域是卷积的,频率域就是相当于相乘。

这个乘法过程使得NCO输出有一个sin(x)/x包络。

这个在DAC输出的衰减在下面计算出来而且一个抽样输出频谱如图5所示:

图5DAC输出的时域和频域表示

Atten(F)=20log[(sin(pF/Fclk)/pF/Fclk)]

当F是输出频率,Fclk是抽样时钟频率。

根据取样理论,实际的值量子化为数字形式必须考虑一个DDS系统的性能分析。

一个DDS系统的假的响应是主要由两个量子化参量确定的。

这些参量是相位累加器的相位量子化和ROM正弦曲线表和DAC的量子化量级。

如上所示,相位累加器只有高Y比特是用来寻址ROM表。

值得注意的是,仅用高Y位引入一个相位截短。

当一个频率控制字包含一个非零的值在低(N-Y-1:

0)位是装载到DDS系统的,低非零位累加到高Y位和使得产生一个相位截短。

相位的截短出现的频率可以根据以下计算:

Ftrunc=FW(N-Y-1:

0)/2N-Y*Fclk.

一个相位的截短会周期性(以Ftrunc速率)相位调制输出载波提前2π/

来补偿频率控制字间隔多于

。

相位的跳转由相位截短位累加在基波周围产生突刺。

这些突刺位于基频的正和负截短频率,突刺的大小是20log(

)dBc。

一个相位截短突刺输出的例子如图5所示。

在一个典型的NCO设计里,正弦ROM表会保持一个1/4正弦波(0,π/2)的量级。

ROM表是通过把所有可能的相位值地址和映射到实际正弦波大小的近似D比特来产生的。

因此,最大的输出误差为-1/2LSB(假设当突刺为-20log(

)dBc的最坏情况时)。

类似于NCO的ROM表,一个DAC也同样是这样量子化数字值为模拟值的。

一个DAC输出的模拟电压取决于输入的数字值。

当设计NCO正弦ROM表时,一种方法是根据经验好于通过理解ROM表和DAC之间的交互作用而在DAC线性得出一些数据。

DAC的量化曲线数字输入对应模拟输出的DAC量化曲线可以看作是理想线性的。

微分线性和积分线性这两个线性参数通常是用来衡量DAC性能。

微分线性是指输出的步进大小为比特到比特。

一个DAC必须编码一个最大的1LSB微分线性。

当输入码增加,DAC的输出必须相应增加。

假如DAC电压的增加不是对应于一个增加的输入数字值,可以说DAC是缺码的。

因此,一个有大于1LSB微分线性的10比特DAC可以精确到9或者更小的比特。

精确输出的比特数量会导致DDS当dl是微分线性的比特数量时的虚假的性能-20log(

)。

积分线性是一个DAC的总的线性性能对一个理想的线性直线的一个衡量。

那条直线图当DC偏置可能是DAC的最大或者最小时可以看作“最好的直线”,或者那条直线可以穿过输出的最大和最小值的结束点。

超出输出范围时一个DAC会有一个特有的弯曲特性曲线。

根据曲线的形状和对称度(半个DAC输出的周期对称),就可以产生DDS基本输出频率的输出“和”。

当这些“和”接近和超过耐奎斯特频率,Fclk/2,这些“和”就成为样本之下和反映到重要的边带,0到Fclk/2。

这个问题可以通过设置NCO的输出到Fclk/4加上一个轻微的偏移量来说明。

第三谐波将倒减去3折轻微的偏移量基波和二次谐波相交耐奎斯特频率的2折偏移量,留下一个反射图象在边缘。

一个典型的频率建立的过程如图5。

另外DAC将产生谐波失真的性质是任意输出波形的对称的分解,例如一个不同的上升和下降时间。

这些性质通常可以由电路板的DAC的外部元件来修正,例如一个RF变压器,电路板设计问题,衰减点等。

英文原文1:

ModulatingDirectDigitalSynthesizerSystem

DDSOverview

Inthepursuitofmorecomplexphasecontinuousmodulationtechniques,thecontroloftheoutputwaveformbecomesincreasinglymoredifficultwithanalogcircuitry.Inthesedesigns,usinganon-lineardigitaldesigneliminatestheneedforcircuitboardadjustmentsoveryieldandtemperature.AdigitaldesignthatmeetsthesegoalsisaDirectDigitalSynthesizerDDS.ADDSsystemsimplytakesaconstantreferenceclockinputanddividesitdownatoaspecifiedoutputfrequencydigitallyquantizedorsampledatthereferenceclockfrequency.ThisformoffrequencycontrolmakesDDSsystemsidealforsystemsthatrequireprecisefrequencysweepssuchasradarchirpsorfastfrequencyhoppers.Withcontrolofthefrequencyoutputderivedfromthedigitalinputword,DDSsystemscanbeusedasaPLLallowingprecisefrequencychangesphasecontinuously.Aswillbeshown,DDSsystemscanalsobedesignedtocontrolthephaseoftheoutputcarrierusingadigitalphasewordinput.Withdigitalcontroloverthecarrierphase,ahighspectraldensityphasemodulatedcarriercaneasilybegenerated.

ThisarticleisintendedtogivethereaderabasicunderstandingofaDDSdesign,andanunderstandingofthespuriousoutputresponse.Thisarticlewillalsopresentasampledesignrunningat45MHzinahighspeedfieldprogrammablegatearrayfromQuickLogic.

DDSBlockDiagram

AbasicDDSsystemconsistsofanumericallycontrolledoscillator(NCO)usedtogeneratetheoutputcarrierwave,andadigitaltoanalogconverter(DAC)usedtotakethedigitalsinusoidalwordfromtheNCOandgenerateasampledanalogcarrier.SincetheDACoutputissampledatthereferenceclockfrequency,awaveformsmoothinglowpassfilteristypicallyusedtoeliminatealiascomponents.Figure1isabasicblockdiagramofatypicalDDSsystemdesign.

ThegenerationoftheoutputcarrierfromthereferencesampleclockinputisperformedbytheNCO.ThebasiccomponentsoftheNCOareaphaseaccumulatorandasinusoidalROMlookuptable.AnoptionalphasemodulatorcanalsobeincludeintheNCOdesign.ThisphasemodulatorwilladdphaseoffsettotheoutputofthephaseaccumulatorjustbeforetheROMlookuptable.ThiswillenhancetheDDSsystemdesignbyaddingthecapabilitiestophasemodulatethecarrieroutputoftheNCO.Figure2isadetailedblockdiagramofatypicalNCOdesignshowingtheoptionalphasemodulator.

FIGURE1:

TypicalDDSSystem.

FIGURE2:

TypicalNCODesign.

TobetterunderstandthefunctionsoftheNCOdesign,firstconsiderthebasicNCOdesignwhichincludesonlyaphaseaccumulatorandasinusoidalROMlookuptable.ThefunctionofthesetwoblocksoftheNCOdesignarebestunderstoodwhencomparedtothegraphicalrepresentationofEuler’sformula

.ThegraphicalrepresentationofEuler’sformula,asshowninFigure3,isaunitvectorrotatingaroundthecenteraxisoftherealandimaginaryplaneatavelocityofωrad/s.Plottingtheimaginarycomponentversustimeprojectsasinewavewhileplottingtherealcomponentversustimeprojectsacosinewave.ThephaseaccumulatoroftheNCOisanalogous,orcouldbeconsidered,thegeneratoroftheangularvelocitycomponentωrad/s.Thephaseaccumulatorisloaded,synchronoustothereferencesampleclock,withanNbitfrequencyword.

ThisfrequencywordiscontinuouslyaccumulatedwiththelastsampledphasevaluebyanNbitadder.TheoutputoftheadderissampledatthereferencesampleclockbyanNbitregister.WhentheaccumulatorreachestheNbitmaximumvalue,theaccumulatorrollsoverandcontinues.PlottingthesampledaccumulatorvaluesversustimeproducesasawtoothwaveformasshownbelowinFigure3.

WhereTrollisthephaseaccumulatorrolloverperiodFoutistheDDSsystemoutputcarrierfrequencyFclkisthereferencesampleclockfrequencyFW(N-1:

0)isthefrequencywordinputvalueandthefrequencygranularityisFW(N-1:

0)/2N

ThesampledoutputofthephaseaccumulatoristhenusedtoaddressaROMlookuptableofsinusoidalmagnitudevalues.Thisconversionofthesampledphasetoasinusoidalmagnitudeisanalogoustotheprojectionoftherealorimaginarycomponentintime.Sincethenumberofbitsusedbythephaseaccumulatordeterminesthegranularityofthefrequencyadjustmentsteps,atypicalphaseaccumulatorsizeis24to32bits.SincethesizeofthesinusoidalROMtableisdirectlyproportionaltotheaddressingrange,notall24or32bitsofthephaseaccumulatorareusedtoaddresstheROMsinusoidaltable.OnlytheupperYbitsofthephaseaccumulatorareusedtoaddressthesinusoidalROMtable,whereY FIGURE3Euler’sEquationRepresentedGraphically DDSDesignConsiderations SinceanNCOoutputsacarrierbasedonadigitalrepresentationofthephaseandmagnitudeofthesinusoidalwaveform,designershavecompletecontroloverfrequency,phase,andevenamplitudeoftheoutputcarrierByaddingaphaseportandaphaseaddertothebasicNCOdesign,theoutputcarrieroftheNCOcanbeMarrayphasemodulatedwhereMequalsthenumberofphaseportbitsandwhereMislessthanorequaltotheYnumberofbitsusedtoaddressthesinusoidalROMtable.ForsystemdesignsthatrequireamplitudemodulationsuchasQAM,amagnitudeportcanbeaddedtoadjustthesinusoidalROMtableoutput.NotethatthisportisnotshowninFigure2andthatthisfeatureisnotdemonstratedinthesampleQuickLogicFPGAdesign.Finally,frequencymodulationisagivenwiththebasicNCOdesign.Thefrequencyportcandirectlyadjustthecarrieroutputfrequency.SincefrequencywordsareloadedintotheDDSsynchronoustothesampleclock,frequencychangesarephase

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 调制 直接 数字 频率 合成器 系统 中英文

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx