数字电子技术教案.docx

数字电子技术教案.docx

- 文档编号:6407302

- 上传时间:2023-01-06

- 格式:DOCX

- 页数:30

- 大小:243.48KB

数字电子技术教案.docx

《数字电子技术教案.docx》由会员分享,可在线阅读,更多相关《数字电子技术教案.docx(30页珍藏版)》请在冰豆网上搜索。

数字电子技术教案

第3章逻辑门电路

实现一些基本运算关系的电路,称为“门电路”。

它是构成数字电路的基本单元。

在门电路中,输入反映“条件”,输出反映“结果”。

入、出之间是逻辑关系。

在逻辑设计中,主要使用集成逻辑器件,分通用逻辑器件和编程逻辑器件。

TTL系列和COMS系列最为常见。

3.1半导体二极管和三极管的开关特性

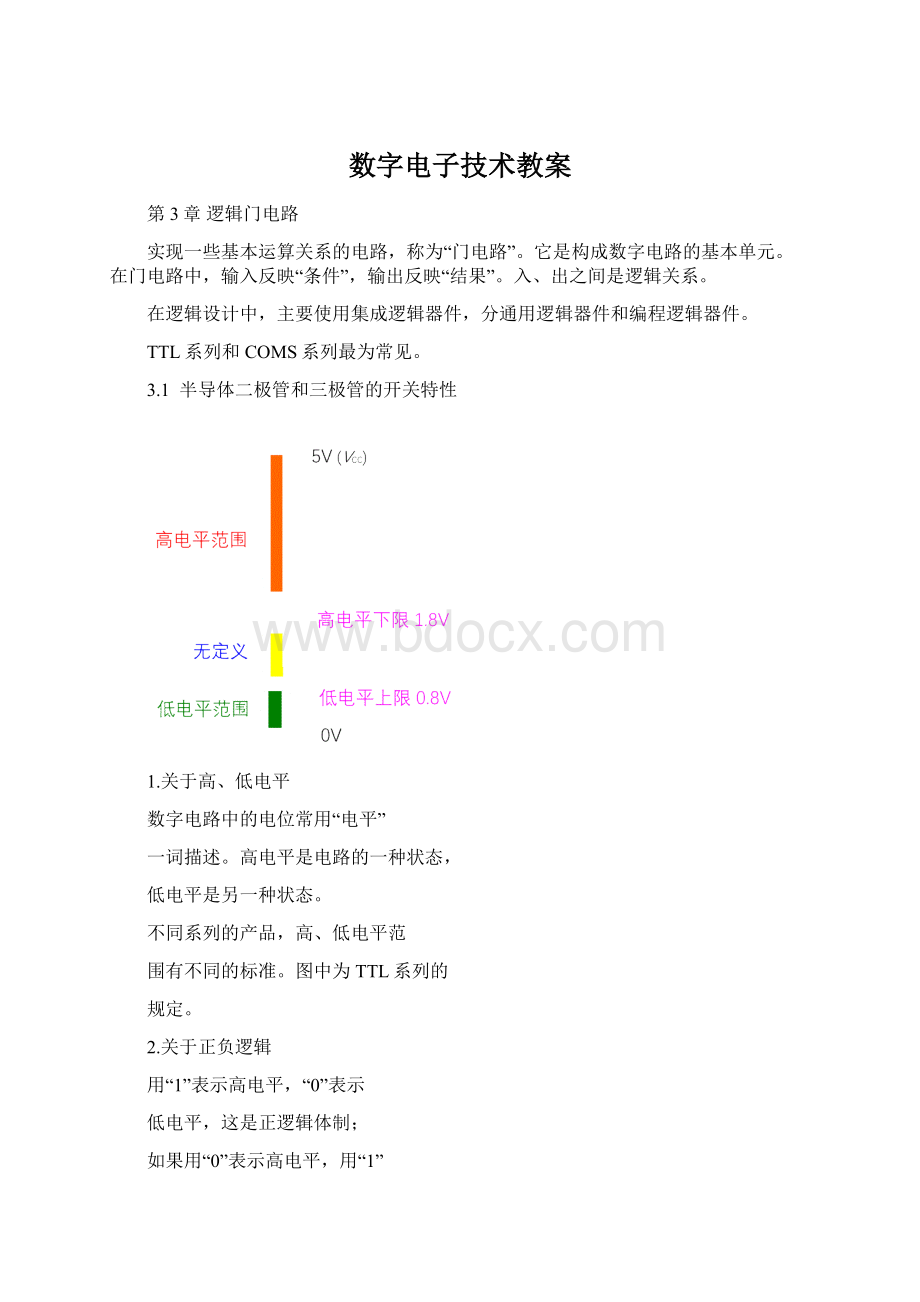

1.关于高、低电平

数字电路中的电位常用“电平”

一词描述。

高电平是电路的一种状态,

低电平是另一种状态。

不同系列的产品,高、低电平范

围有不同的标准。

图中为TTL系列的

规定。

2.关于正负逻辑

用“1”表示高电平,“0”表示

低电平,这是正逻辑体制;

如果用“0”表示高电平,用“1”

表示低电平,就是负逻辑体制。

同一个电路,可采用正逻辑体制,也可采用负逻辑体制,还可以同时采用正、负逻辑,称为混合逻辑。

今后不加说明,一律采用正逻辑体制。

3.1.1理想开关的开关特性

一、静态特性

S可由二极管、三极管或MOS管实现

①断开

②闭合

二、动态特性

①开通时间:

(断开—闭合)

②关断时间:

闭合—断开

普通开关:

静态特性好,动态特性差

半导体开关:

静态特性较差,动态特性好

3.1.2半导体二极管的开关特性

二极管具有单向导电性。

导通条件:

VD>+0.7V,如同一个具有约0.7V压降的闭合开关。

截止条件:

VD<死区电压,ID≈0,如同开关断开一样。

动态情况,二极管的工作速度问题:

截止到导通:

电荷积累需要时间(产生扩散运动),可以忽略。

导通到截止:

电荷存储效应产生反向恢复时间tre。

(存储的电荷要消散,也需要一定时间,此瞬间有较大的瞬态反向电流。

)

二极管的动态电流波形见下图。

3.1.3晶体三极管的开关特性

1.四种工作状态

放大状态:

发射结正偏,集电结反偏;

截止状态:

发射结反偏,集电结反偏;

饱和状态:

发射结正偏,集电结正偏;

倒置状态:

发射结反偏,集电结正偏。

在数字电路中,三极管主要工作在开关

状态,因而不是截止就是饱和。

Rc

Rb

T

+VCC

ui

uo

IB

IC

截止时,c-e间呈现数百千欧的电阻,如同开关断开。

饱和时,c-e间呈现数百欧的电阻,如同开关闭合。

偶尔也会出现倒置状态。

2.工作状态的判定(依据:

结偏置情况。

)

①根据三个极的电位情况判定,常用于实验测定。

②根据三极管的电流关系判定,常用于解题过程。

截止:

UBE≤0.5V(硅管),IB≤0,IC=0,此时UCE=VCC

放大:

UBE≈0.7V(硅管),IB>0,IC=βIB,此时UCE=VCC-ICRC

饱和:

UBES≈0.7V(硅管),IB≥IBS,IC<βIB,此时UCE=UCES≈0.3V

其中:

IBS

(为临界饱和电流)

例3.1.1电路见上图。

VCC=5V,RB=30kΩ,RC=1kΩ。

试求ui=0V和3V时,uo=?

设①β=100;②β=50;③分析电路参数对三极管工作状态的影响。

解:

①ui=0V时,UBE≤0.5V,T处于截止状态,UCE≈VCC=5V。

ui=3V时,T导通,基极电流IB

≈0.077(mA)

基极临界饱和电流:

IBS

=

≈0.047(mA)

由于IB≥IBS,故T处于饱和状态。

UCE=UCES≈0.3V

0

t

ui

ton

0

t

iC

0

t

uO

toff

②β=50时,IBS

=

≈0.094(mA)

由于IB≤IBS,故T处于放大状态。

IC=βIB=50×0.077=3.85(mA)

UCE=VCC-ICRC=5-3.85×1=1.15(V)

③根据IB≥IBS,

即

≥

可知:

增大ui、β、RC,减小VCC、RB

有利于三极管饱和。

3.三极管的动态特性

电荷的建立与消散需要一定时间,

影响了三极管的开关速度。

集电区积累的过量电荷消散时间较长,因而关断时间长,是影响开关速度的主要因素。

3.2 基本逻辑门电路

3.2.1 二极管与门电路

VCC(+5V)

D1

D2

R

2.8kΩ

VA

VB

VF

IIL

IIH

0V

6V

1.工作原理

①VA=VB=UIL=0V

D1、D2都导通,VF=UOL=0.7V。

②VA=UIH=6V,VB=UIL=0V

D2导通,使VF=0.7V,D1截止。

(VB=UIH=6V,VA=UIL=0V情况类似。

)

③VA=VB=UIH=6V

D1、D2都截止,VF=UOH=5V。

结论:

输入有低出低,全高出高。

2.两个参数

①输入低电平电流IIL

IIL=

=1.5(mA)若两个管同时导通,则平分该电流。

②输入高电平电流IIH

二极管截止时,只有反向饱和电流,约数十微安,为分析方便取IIH=10μA。

3.2.2二极管或门电路

1.工作原理

①VA=VB=UIL=0V

D1、D2都截止,VF=UOL=0V。

②VA=UIH=6V,VB=UIL=0V

D1导通,使VF=5.3V,D2截止。

(VB=UIH=6V,VA=UIL=0V情况类似。

)

③VA=VB=UIH=6V

D1、D2都导通,VF=UOH=5.3V。

结论:

输入有1出1,全0出0。

二极管或门电路请自己分析。

3.2.3晶体三极管非门电路

1.三极管非门

①输入为低电平

T截止,输出为高电平。

此时,D导通,uO=3+0.7=3.7(V)

D为嵌位二极管,与(+3V)电源

组成嵌位电路,将输出高电平嵌位在约

3.6V上(理论值为3.7V),便于同后面

的门电路连接。

②输入为高电平

VT饱和导通,输出为低电平,uO≈0.3V。

设UIL=3.6V,则IB≈(3∕1.5)=2mA,ICS≈(5∕1)=5mA。

可见,只要β>2.5,就有IB>IBS=(ICS∕β)。

实现了“入低出高,入高出低”的非门功能。

2.负载能力分析

当门电路的输出端与其它门电路连接时,后级的这些门电路就是前级门电路的负载。

负载的大小当然指电流的大小,有两种情况:

凡是负载电流流进门电路输出端的叫灌电流负载;

凡是负载电流流出门电路输出端的叫拉电流负载。

①灌电流负载

T饱和时,UCES≈0.3V,IL从外电路流入

集电极,使IC增加:

IC=IRC+I灌。

随着I灌的增大,会有两个问题:

Ø破坏IB>(IC∕β)这一条件,使T退出

饱和,输出低电平被抬高;

Ø可能使IC=IRC+I灌>ICM,超过管子的承

受能力,烧坏管子。

所以,对I灌一定要加以限制。

为不破坏T的饱和条件,应保证:

IB≥(IC∕β)。

即:

βIB≥IRC+I灌→I灌≤βIB+IRC

可见,最大灌电流负载能力为:

I灌max=βIB+IRC

当灌电流超过I灌max时,会使T退出饱和,输出低电平抬高,破坏了“有1出0”的逻辑功能。

为管子安全,还要保证IC=I灌max+IRC<ICM。

带灌电流负载只考虑输出为低电平时的情况。

在ICM允许时,饱和程度越深,电路带灌电流负载能力越强。

②拉电流负载

T截止时,IC≈0,IRC=I拉,UOH=VCC-RCI拉

I拉过大,会导致UOH降低,严重时,会破坏

“有0出1”之功能。

为使UOH不低于UOHmin

I拉max=

从上式知,减小RC有利于提高拉电流的负载能力。

但不利于提高灌电流的负载能力。

带拉电流负载仅考虑输出为高电平时的情况。

门电路的负载能力要同时考虑I灌和I拉,取其中较小的。

门电路的负载能力指带同类门的个数,称扇出系数N。

3.3 TTL逻辑门

数字集成电路按所用半导体器件不同,分为双极型(TTL)和单极型(MOS)两大类。

TTL系列是世界上生产历史最长、数量最多的数字集成电路。

由于不断进行结构改进和性能提高,使TTL集成电路在众多的系列品种面前仍保持盛况不衰。

目前,以CT4000系列为主流,与国际SN54LS∕74LS000对应,兼有低功耗和较高速的特点。

本节以与非门为例,简单介绍TTL系列数字集成电路的特点。

3.3.1 TTL与非门工作原理

IB1

T4

VCC(+5V)

T5

T3

T2

T1

R1

R2

R3

R5

R4

3k

750

360

100

3k

F(UO)

A

B

C

1.电路组成

输入级:

T1、R1;

其主要作用是:

①提高开关速度;

②完成“与”运算。

中间级:

T2、R2、R3;

输出相位相反的两路信号,

分别控制T3、T5的工作状

态。

输出级:

T3、T4、T5、R4、R5;其主要作用是:

①提高负载能力;②完成“非”运算。

2.工作原理

①输入有低:

0.3V

≈1.33(mA)

ICS1=ICBO2≈0,T1为深度饱和,UCES2≈0.1(V)

UB2≈0.1+0.3=0.4(V),T2、T5截止。

VCC经R5使T2、T5导通,所以

UO=VCC-IB3R2-VBE3-VBE4≈5-0.7-0.7=3.6(V)→即输出为高电平。

②输入全高:

3.6V

T4

VCC(+5V)

T5

T3

T2

T1

R1

R2

R3

R5

R4

3k

750

360

100

3k

F(UO)

A

B

C

3.6V

0.7V

1.4V

2.1V

IB1

IB2

IC2

IR2

IB3

1V

0.3V

IB5

VCC经R1使T1集电结、

T1、T2发射结正向导通,这

三个正向导通的PN结把VB1

嵌制在约2.1V左右。

因输入为3.6V,故T1

的所有发射结反偏,集电

结正偏,T1处于“倒置工

作状态”。

(集电结、发射

结颠倒用的“放大”状

态,β约0.01左右。

)

由于T2饱和导通,UC2=UB3=0.7+0.3=1(V),这个结果使T2微导通,T4截止。

由于T4截止,使IC5≈0,故T5导通后便进入深度饱和状态。

所以UO=UOL=UCES5≈0.3(V)→即输出为低电平。

综上,该电路实现了与非门的功能。

T4为T5的有源负载,相当于T5的集电极电阻,当T5饱和时,T4截止,呈现很大的电阻,有利于带灌电流负载;当T5截止时,T4导通,等效电阻较小,又有利于带拉电流负载。

这种T4、T5轮流导通的输出方式称“AD”输出。

3.3.2 TTL与非门的主要参数

对使用者来说,内部工作原理可以不用关心,但逻辑功能、电气特性和主要参数必须要了解,以便正确合理地使用。

1.输出高电平UOH

定义:

任何一个输入端接规定的低电平时,输出端的电平。

意义:

反映逻辑功能、与其它电路接口的依据。

指标:

UOH≥3V(典型值3.6V,最小值2.4V。

)

2.输出低电平UOL

定义:

输入端全部接高电平时,与非门输出端的电平。

意义:

反映逻辑功能、与其它电路接口的依据。

指标:

UOL≤0.35V(典型值0.3V,最大值0.4V。

)

3.开门电平UON

定义:

在额定负载下,使输出达到标准低电平时的最小输入电平。

意义:

反映输入高电平时的抗干扰能力。

指标:

UON≤1.8V

4.关门电平UOFF

定义:

使输出上升到额定高电平的时的输入电平。

意义:

反映输入低电平时的抗干扰能力。

指标:

UOFF≥0.8V

以上是输入输出高、低电平的参数。

为了更好地理解反映抗干扰能力的参数,先简单介绍一下电压传输特性。

UO∕V

4

3

2

1

0

UI∕V

1

2

3

4

T2开始导通

T5开始导通

T5开始饱和

UIL

UOFF

UNL

UON

UIH

UNH

额定高电平的90%

额定

高电平

UOH

UOL

&

UO

V

UI

+5V

5.低电平噪声容限UNL

定义:

保证UOH不低于额定值90%的条件下,允许迭加在UIL上的最大正向干扰电压。

由上图可见:

UNL=UOFF-UIL

6.高电平噪声容限UNH

定义:

保证UO=UOL的条件下,允许叠加在UIL上的最大负向干扰电压。

由上图可见:

UNH=UIH-UON

UNL、UNH都是说明门电路抗干扰能力的参数,其值越大,抗干扰能力越强。

7.输入低电平电流IIL(也称为输入短路电流)

定义:

一个输入端接地,其它输入端悬空,流过接地输入端的电流。

意义:

关系到带同类门负载的个数,反映了R1的工艺质量。

(是灌入前级门输出端的电流。

)

指标:

IIL<1.6mA

8.输入高电平电流IIH(也称为输入交叉漏电流)

定义:

任意输入端接高电平,其余输入端接地,流进接高电平输入端的电流。

意义:

是从前级门输出端拉出的电流,关系到带同类门负载的个数。

指标:

IIH≤40μA

为减轻前级门的负担,本门的IIL、IIH小好。

9.输出低电平电流IOL

定义:

UO=UOL时,允许负载(后级门)灌入输出端的极限电流。

意义:

IOL反映吸电流能力。

其值大,带灌电流负载能力强。

规定:

IOLmax=16mA

10.输出高电平电流IOH

定义:

UO=UOH时,允许负载(后级门)拉出输出端的极限电流。

意义:

IOH反映带拉电流负载的确能力。

规定:

IOHmax=0.4mA

为提高带负载能力,本门的IOL、IOH大好。

11.扇出系数NO:

定义:

电路带同类门的个数。

意义:

说明带负载能力。

通过7、8、9、10指标算出:

输出低电平时:

NOL=

=10.7(个)

输出高电平时:

NOH=

=20(个)

取较小的整数,故扇出系数NO=10个

指标:

普通门NO≥8个,功率门NO≥16个或24个。

12.平均传输时间tpd

定义:

tpd=

意义:

反映工作速度。

指标:

普通门tpd<40ns,

高速门tpd<5ns。

*13.空载导通电源电流ICCL(或空载导通功耗)

定义:

电路处于空载导通状态下的电流。

意义:

反映电路本身的功耗(PON=VCCICCL)

指标:

ICCL≤10mA

*14.空载截止电源电流ICCH(或空载截止功耗)

定义:

电路处于空载截止状态下的电流。

意义:

反映电路本身的功耗(POFF=VCCICCH)

指标:

ICCH≤5mA

3.3.3其他类型的TTL集成门电路

1.TTL集电极开路门OC门

(1)“线与”的概念

把几个门电路的输出端直接连在一起,

使新的输出起到原几个输出的“与”作用,

叫做“线与”,也称“隐与”。

采用“线与”,可以在不增加门电路的基

础上增加逻辑功能。

但是,普通的TTL与非

门不能接成线与形式。

因为:

当门电路输出有高有低时,有很大

的电流由截止门流向饱和门。

这不仅使UOL被

抬高,而且功耗大,易烧坏截止门。

(2)OC与非门

注意:

使用时必须外接一个

上拉电阻。

上拉电阻的作用是:

用来构成所需要的输出电平;

选择原则是:

既能保证UOH的需要,又能满足UOL的需要。

上拉电阻的计算:

①UO为高电平时

IRL=nIOH+mIIH

为保证UO≥UOH,RL不能太大。

应有:

VCC-RLIRL≥UOH

所以:

RL≤

或者:

RLmax=

②UO为低电平时

最不利的情况是只有一个门导通为低

电平,这时所有电流都灌入该门,为保证

门不被烧坏,必须限制电流IOL≤ILM。

取

IOL=ILM(尽限应用),有

IRL=ILM-mIIL

为保证UO≤UOL,RL不能太小。

应有:

VCC-RLIRL≤UOL

所以:

RL≥

综上所述,RL的取值范围为:

≥RL≥

(3)主要应用

①实现“与或非逻辑”;②用作电平转换;③直接驱动指示灯、继电器等。

&

A

B

&

RL

VCC

&

TTL

F

OC

MOS

2.三态门(TS)

除工作时电路的输出有高、低电平两个状态外,还有“禁止状态”,或称“高阻状态”。

EN=1时,处于工作状态,其功能是Z=

EN=0时,T5截止。

D导通后又使UC2≈1V,故T4也截止,即

输出端“悬空”,处于高阻状态。

(另一种:

=0时,为工作状态;

=1时,成高阻状态。

见上图。

)

主要用途:

能向一条导线上轮流传送几个不同的数据或控制信号。

工作条件:

任何时间里,只许一个门处于工作状态,所以要求:

3.3.4 TTL电路使用常识

1.产品系列

国产的TTL集成电路共有五个系列:

T1000标准系列(对应国外的SN54∕74系列);

T2000高速系列(对应国外的SN54H∕74H系列);

T3000肖特基系列(对应国外的SN54S∕74S系列);

T4000低功耗肖特基系列(对应国外的SN54LS∕74LS系列);

T000系列。

T000又分两个子系列:

中速系列(与T1000类似)和高速系列(与T2000类似)。

2.多余输入端的处理

对与非门:

①通过电阻接电源或直接接电源

②同有用端并联

③悬空(相当于逻辑1),容易受到干扰。

对或非门:

①同有用端并联

②接地(相当于逻辑0)。

3.开门电阻RON和关门电阻ROFF

①RON的定义:

保证“与非门”开启,UO为低电平的

条件下,允许的RI最小值。

由:

UI

UI≈

RI≥UON

得RI≥1.45kΩ

(T2导通时,IRI=IB1-IB2变小,按

上式算出的值比实际值小。

)

典型值:

RON≈2kΩ

②ROFF的定义:

保证UO不低于额定值90%的条件下,允许的RI最大值。

由UI≈

≤UOFF得:

RI≤686Ω。

典型值:

ROFF≈700Ω

当RI<ROFF时,与非门关闭,UO=UOH

当RI>RON时,与非门开启,UO=UOL

R

&

A

B

LED

4.带灌电流负载能力强于拉电流负载能力

接发光二极管等负载时注意。

3.4MOS集成门电路

以MOS管作为开关元件的门电路叫MOS门电路。

MOS门电路的种类很多,以CMOS电路表现出很强的竞争力。

在数字集成电路中,其产值和产量所占的比例仅次于TTL集成电路。

CMOS电路的主要特点:

静态功耗低;电压范围宽;抗干扰能力强;温度稳定性好;抗辐射能力强;成本低;电路简单,故集成度高;输入阻抗高,故扇出系数大。

其缺点是:

工作速度不如TTL高、动态功耗随工作频率的升高而增大。

吸、放电流较小。

目前,国产的CMOS门电路有两个系列:

C000系列(工作电压7~15V)和CC4000系列(工作电压3~18V)。

CC4000系列与国外CD4000、MD14000系列对应,可以直接代换。

3.4.1NMOS门电路

MOS是MOS数字集成电路的基本单元,学习它的工作原理,是研究MOS数字集成电路的基础。

1.MOS管的结构

增强型结构耗尽型结构

MOS管的图形符号

N沟道增强型P沟道增强型N沟道耗尽型P沟道耗尽型

衬底的连接:

N沟道总接电路中最低电位,P沟道总接电路中最高电位。

3.MOS管的开关作用

MOS管属于电压控制器件。

D、S之间的导电沟道,受G、S之间电压的控制。

对增强型:

|UGS|≥UT,D、S之间存在导电沟道,相当于开关闭合,

|UGS|<UT,D、S之间导电沟道消失,相当于开关断开。

对耗尽型:

|UGS|≥UP,D、S之间(原始)导电沟道消失,相当于开关断开,

|UGS|<UP,D、S之间存在(原始)导电沟道,相当于开关闭合。

3.NMOS反相器

由两只增强型MOS管组成(叫E/EMOS反相器)。

T1为驱动管;

T2为负载管。

由于G、D接在一起,故总有

UGS-UDS=0<UT,即T2靠近D极附近有夹断区,

始终工作于饱和区。

称饱和型有源负载。

UOH=VDD-UT

UOL=

≈1V要求RON2>>RON1。

4.NMOS与非门

①与非门②或非门③与或非门

集成度较高,但未解决动态、静态之间的矛盾,电源利用率也低。

uO

ui

O

0.5VDD

0.5VDD

A

E

B

C

D

3.4.2CMOS反相器

1.CMOS非门(反相器)(互补型)

工作管TN仍用N沟道增强型MOST;

负载管TP则用P沟道增强型MOST。

①工作原理

取VDD>UTN+|UTP|

A为低电平:

UI≈0V<UT,TN截止,但

|UGSP|≈VDD>|UTP|。

故TP导通,UOH≈VDD;(电源利用率高)A为高电平:

UI≈VDD,TN导通,

而|UGSP|≈0,故TP截止,UOL≈0。

(不取决于沟道电阻的分压)接近于理想开关。

②特性分析

A区:

ui<UTN,TN截止,TP饱和;

B区:

ui>UTN附近,TN开始向饱和进军,TP要退出饱和,uO开始下降;

C区:

ui继续增大到约0.5VDD后,TN、TP都导通,此时有较大的直通电流;

D区:

TP趋于截止,TN趋于饱和;

E区:

TP截止,TN饱和。

③CMOS门电路的特点:

不足之处:

工艺复杂,成本较高,集成度低(电路中间需隔离区)。

3.4.3其他类型的CMOS门电路

1.CMOS与非门

电路图如图所示,功能表如表所示

+VDD

TN1

F

TP1

TN2

TP2

A

B

2.CMOS或非门

CMOS门电路为互补型,故一个工作管必跟一个负载管;工作管串并联时,负载管就并串联。

电路图如图所示,功能表如表所示

3.OD门

输出部分做成漏极开路形式,

满足较大灌电流负载的需要。

图中的与非缓冲∕驱动器,

在输出低电平时,允许灌入约

50mA的电流。

可以用作驱动发

光二极管、电平转换等。

4.CMOS传输门和模拟开关

传输门相当于一个开关,若将前级电路的输出经传输门送到后级电路,则可以由命令脉冲来控制信息的传递。

C=1,(

)时,TN、TP至少

有一个导通,故uo≈ui。

例如:

设CMOS的开启电压为

∣UT∣=3V,控制电平为10V。

当C=1(

=0)时,则:

ui在0~3V时,TN通、TP止;

ui在3~7VTN、TP都通;

ui在7~10V时,TN止、TP通。

所以,只要ui在0~10V(VDD)范围内变化,都能传输到输出端。

当C=0(

=1)时,TN、TP都截止,相当于开关断开。

1

TG

C

ui

uo

C

ui

uo

CMOS传输门的输入输出可以

互换,导通电阻仅数百欧,断开时

大于109欧,是一个较为理想的开

关器件。

它同非门组合能构成许多

复杂的逻辑电路,如触发器、数据

选择器等。

右图是传输门与反相器组合的

一个模拟开关。

5.CMOS三态门

在CMOS反相器的基础上增加一些控制门而成。

左图:

=1(设高电平为VDD),TP1、TN2都截止,中间(由TN1、TP2组成)的反相器上不通电源,下不接地,F端处于悬空状态。

=0,TP1、TN2都导通,中间的反相器正常工作。

右图:

EN=0,TN2截止,TP也截止,F端处于悬空状态。

(与非门被封锁,A端的状态送不到反相器的输入端。

)

EN=1,TN2导通,与非门解除封锁,由TN1、TP组

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 电子技术 教案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx