数字式频率计的设计.docx

数字式频率计的设计.docx

- 文档编号:6173432

- 上传时间:2023-01-04

- 格式:DOCX

- 页数:24

- 大小:108.36KB

数字式频率计的设计.docx

《数字式频率计的设计.docx》由会员分享,可在线阅读,更多相关《数字式频率计的设计.docx(24页珍藏版)》请在冰豆网上搜索。

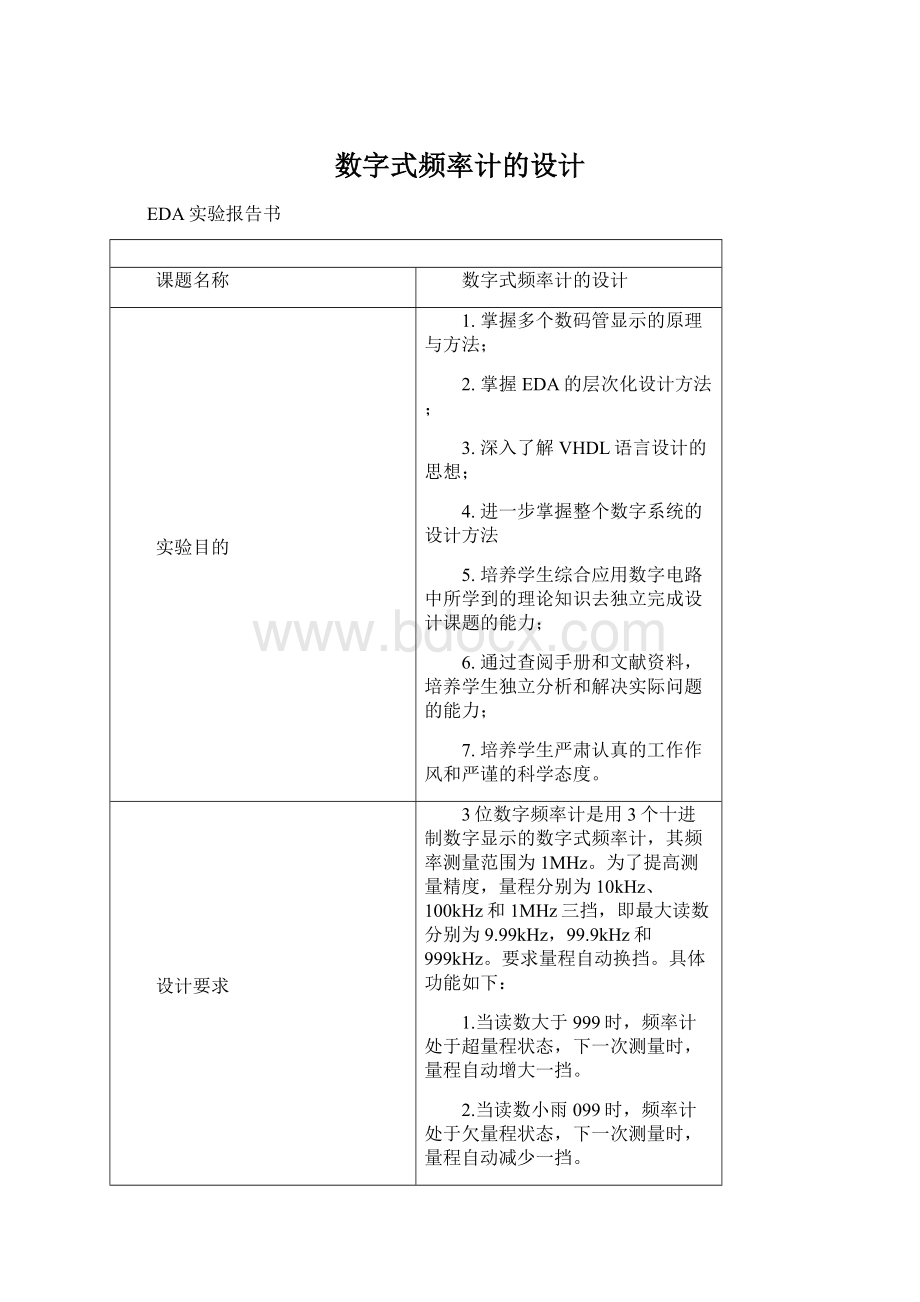

数字式频率计的设计

EDA实验报告书

课题名称

数字式频率计的设计

实验目的

1.掌握多个数码管显示的原理与方法;

2.掌握EDA的层次化设计方法;

3.深入了解VHDL语言设计的思想;

4.进一步掌握整个数字系统的设计方法

5.培养学生综合应用数字电路中所学到的理论知识去独立完成设计课题的能力;

6.通过查阅手册和文献资料,培养学生独立分析和解决实际问题的能力;

7.培养学生严肃认真的工作作风和严谨的科学态度。

设计要求

3位数字频率计是用3个十进制数字显示的数字式频率计,其频率测量范围为1MHz。

为了提高测量精度,量程分别为10kHz、100kHz和1MHz三挡,即最大读数分别为9.99kHz,99.9kHz和999kHz。

要求量程自动换挡。

具体功能如下:

1.当读数大于999时,频率计处于超量程状态,下一次测量时,量程自动增大一挡。

2.当读数小雨099时,频率计处于欠量程状态,下一次测量时,量程自动减少一挡。

3.当超出频率测量范围时,显示器显示溢出。

4.采用记忆显示方法,即测量过程中不显示数据,待测量过程结束以后,显示测频结果,并将此结果保持到下次测量结束。

显示时间不少于1秒。

5.小数点位置随量程变化自动移位。

6.增加测周期功能,就是当时钟频率低于0.99kHz的时候,显示的数值变成周期,以毫秒为单位。

设计思路

数字频率计的关键组成部分包括测频控制信号发生器、计数器、锁存器、译码驱动电路、分频电路和显示电路,其原理框图如下图所示。

设计原理图及源程序

原理图

频率计源文件

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDFREIS

PORT(RESET:

INSTD_LOGIC;

CLK1K:

INSTD_LOGIC;--1K时钟信号

TESTSIGNAL:

INSTD_LOGIC;--测试信号输入端

DISPLAY1:

OUTSTD_LOGIC_VECTOR(0TO3);

DISPLAY2:

OUTSTD_LOGIC_VECTOR(0TO3);

DISPLAY3:

OUTSTD_LOGIC_VECTOR(0TO3);--3个7段译码器输出

UNIT:

OUTSTD_LOGIC;--表示是周期还是频率的信号灯

DOT:

OUTSTD_LOGIC_VECTOR(2DOWNTO0));--小数点

ENDENTITYDFRE;

ARCHITECTUREONEOFDFREIS

TYPESTATEIS

(START,JUDGE,COUNT1,COUNT2TO89,COUNT90,COUNT91TO98,COUNT99,COUNT100);

SIGNALMYFRE:

STATE;

SIGNALFRECOU:

INTEGERRANGE0TO99;--用于状态机中的计数器,计数值从0~99

SIGNALENFRE:

STD_LOGIC;--代表时基的脉冲信号

SIGNALFLAG:

STD_LOGIC_VECTOR(2DOWNTO0);

--标志信号,1表示10KHZ测频挡,2表示100KHZ测频挡,3表示1MHZ测频挡,0表示测周期挡,4表示溢出

SIGNALKEEPCOU1:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALKEEPCOU2:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALKEEPCOU3:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALTTCLK:

STD_LOGIC;--输入计数器的时钟信号即时基

SIGNALTTSIG:

STD_LOGIC;--输入计数器的测试信号

COMPONENTDISPLAYIS--引用7段译码器

PORT(DATA_IN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

DATA_OUT:

OUTSTD_LOGIC_VECTOR(0TO6)

);

ENDCOMPONENT;

COMPONENTFREQUENCYIS--–引用计数器

PORT(TRESET:

INSTD_LOGIC;

TCLK,TSIG:

INSTD_LOGIC;

TKEEP1:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

TKEEP2:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

TKEEP3:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCOMPONENT;

BEGIN

CTRDOT:

PROCESS(FLAG)--控制小数点显示的进程,标志FLAG为敏感量

BEGIN

CASEFLAGIS

WHEN"000"=>DOT<="000";

WHEN"001"=>DOT<="100";

WHEN"010"=>DOT<="010";

WHEN"011"=>DOT<="001";

WHENOTHERS=>DOT<="111";

ENDCASE;

ENDPROCESSCTRDOT;

CTRFRE:

PROCESS(RESET,CLK1K)--用于产生时基的状态机

BEGIN

IFRESET='1'THEN

FRECOU<=0;ENFRE<='0';FLAG<="001";MYFRE<=START;

ELSE

IFCLK1K'EVENTANDCLK1K='1'THEN

CASEMYFREIS

WHENSTART=>FRECOU<=0;ENFRE<='0';FLAG<="011";MYFRE<=JUDGE;

WHENJUDGE=>

IFFLAG="000"THEN--如果标志为0,即频率计处于测周期挡

IFKEEPCOU3="0000"ANDKEEPCOU2="0000"ANDKEEPCOU1="0000"THEN

FLAG<="001";ENFRE<='1';

ELSEFLAG<="000";

ENDIF;

ELSIFFLAG="100"THEN--如果标志为4,即处于溢出挡

IFKEEPCOU3="1010"THEN

FLAG<="100";

ELSEFLAG<="011";

ENDIF;

ELSIFFLAG="010"THEN--如果标志为2,即处于100KHZ挡

IFKEEPCOU3<"0001"THEN

FLAG<=FLAG-1;

ENFRE<='1';

ELSIFKEEPCOU3="1010"THEN

FLAG<=FLAG+1;

ELSEFLAG<=FLAG;

ENDIF;

ELSIFFLAG="001"THEN--如果标志为1,即处于10KHZ挡

IFKEEPCOU3<"0001"THEN

FLAG<=FLAG-1;

ELSIFKEEPCOU3="1010"THEN

FLAG<=FLAG+1;

ELSEFLAG<=FLAG;

ENFRE<='1';

ENDIF;

ELSE--如果标志为3,即处于1MHZ挡

IFKEEPCOU3<"0001"THEN

FLAG<=FLAG-1;

ELSIFKEEPCOU3="1010"THEN

FLAG<=FLAG+1;

ELSEFLAG<=FLAG;

ENDIF;

ENDIF;

MYFRE<=COUNT1;--处于计数状态1的时候

WHENCOUNT1=>

IFFLAG="001"ORFLAG="000"THEN

ENFRE<='1';

ELSEENFRE<=ENFRE;

ENDIF;

FRECOU<=1;

MYFRE<=COUNT2TO89;

WHENCOUNT2TO89=>--处于计数状态2~89的时候

IFFRECOU=88THEN

FRECOU<=89;

MYFRE<=COUNT90;

ELSEFRECOU<=FRECOU+1;

MYFRE<=COUNT2TO89;

ENDIF;

WHENCOUNT90=>--处于计数状态90的时候

IFFLAG="010"THEN

ENFRE<='1';

ELSEENFRE<=ENFRE;

ENDIF;

FRECOU<=90;

MYFRE<=COUNT91TO98;

WHENCOUNT91TO98=>--处于计数状态91~98的时候

IFFRECOU=97THEN

FRECOU<=98;

MYFRE<=COUNT99;

ELSEFRECOU<=FRECOU+1;

MYFRE<=COUNT91TO98;

ENDIF;

WHENCOUNT99=>--处于计数状态99的时候

IFFLAG="011"ORFLAG="100"THEN

ENFRE<='1';

ELSEENFRE<=ENFRE;

ENDIF;

FRECOU<=99;

MYFRE<=COUNT100;

WHENCOUNT100=>--处于计数状态100的时候

FRECOU<=100;

ENFRE<='0';

MYFRE<=JUDGE;--状态转移到判断状态

WHENOTHERS=>NULL;

ENDCASE;

ENDIF;

ENDIF;

ENDPROCESSCTRFRE;

CTRTT:

PROCESS(RESET,FLAG)--用于控制计数器输入的进程

BEGIN

IFRESET='1'THEN

TTCLK<='0';TTSIG<='0';UNIT<='0';--异步置位使得输入信号都为0

ELSE

IFFLAG=0THENTTCLK<=CLK1K;TTSIG<=TESTSIGNAL;UNIT<='1';

--如果标志为0即频率计处于测周期挡

ELSETTCLK<=TESTSIGNAL;TTSIG<=ENFRE;UNIT<='0';

--如果标志不为0即频率计处于测频率挡

ENDIF;

ENDIF;

ENDPROCESSCTRTT;

C1:

FREQUENCYPORTMAP(RESET,TTCLK,TTSIG,KEEPCOU1,KEEPCOU2,KEEPCOU3);

--引用计数器

DIS1:

DISPLAYPORTMAP(KEEPCOU1,DISPLAY1);

DIS2:

DISPLAYPORTMAP(KEEPCOU2,DISPLAY2);

DIS3:

DISPLAYPORTMAP(KEEPCOU3,DISPLAY3);

ENDONE

20分频源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYFREDIV20KIS

PORT(INCLK:

INSTD_LOGIC;

OUTCLK:

BUFFERSTD_LOGIC);

END;

ARCHITECTUREONE10KOFFREDIV20KIS

SIGNALCOU:

INTEGERRANGE0TO4999;

SIGNALTEMP:

STD_LOGIC;

BEGIN

PROCESS(INCLK)

BEGIN

IFINCLK'EVENTANDINCLK='1'THEN

IFCOU=4999THEN

COU<=0;TEMP<='1';

ELSE

COU<=COU+1;TEMP<='0';

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(TEMP)

BEGIN

IFTEMP'EVENTANDTEMP='1'THEN

OUTCLK<=NOTOUTCLK;

ENDIF;

ENDPROCESS;

ENDONE10K;

译码器模块

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDISPLAYIS

PORT(DATA_IN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

DATA_OUT:

OUTSTD_LOGIC_VECTOR(0TO3));--7段译码输出

ENDENTITYDISPLAY;

ARCHITECTUREONEOFDISPLAYIS

SIGNALINDATA:

STD_LOGIC_VECTOR(3DOWNTO0);--内部数值信号

BEGIN

PROCESS(DATA_IN)--输入信号作为进程的敏感量触发进程

BEGIN

INDATA<=DATA_IN;

CASEINDATAIS

WHEN"0000"=>DATA_OUT<="0000";

WHEN"0001"=>DATA_OUT<="0001";

WHEN"0010"=>DATA_OUT<="0010";

WHEN"0011"=>DATA_OUT<="0011";

WHEN"0100"=>DATA_OUT<="0100";

WHEN"0101"=>DATA_OUT<="0101";

WHEN"0110"=>DATA_OUT<="0110";

WHEN"0111"=>DATA_OUT<="0111";

WHEN"1000"=>DATA_OUT<="1000";

WHEN"1001"=>DATA_OUT<="1001";

WHENOTHERS=>DATA_OUT<="1111";

ENDCASE;

ENDPROCESS;

ENDONE;

计数器模块

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYFREQUENCYIS

PORT(TRESET:

INSTD_LOGIC;--异步复位端口

TCLK:

INSTD_LOGIC;--待测时钟输入

TSIG:

INSTD_LOGIC;--时基信号输入

TKEEP1:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);--计数值个位

TKEEP2:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);--计数值十位

TKEEP3:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));--计数值百位

ENDENTITYFREQUENCY;

ARCHITECTUREONEOFFREQUENCYIS

SIGNALTCOU1:

STD_LOGIC_VECTOR(3DOWNTO0);--内部计数值个位

SIGNALTCOU2:

STD_LOGIC_VECTOR(3DOWNTO0);--内部计数值十位

SIGNALTCOU3:

STD_LOGIC_VECTOR(3DOWNTO0);--内部计数值百位

BEGIN

CTRCOU:

PROCESS(TRESET,TCLK)--控制计数功能的进程

BEGIN

IFTRESET='1'THEN

TCOU1<="0000";TCOU2<="0000";TCOU3<="0000";

ELSE

IFTCLK'EVENTANDTCLK='1'THEN

IFTSIG='1'THEN

IFTCOU3="1010"THEN

TCOU3<="1010";--如果百位为10,百位数值不变

ELSE

IFTCOU1="1001"ANDTCOU2="1001"ANDTCOU3="1001"THEN

--如果计数值为999

TCOU1<="0000";TCOU2<="0000";TCOU3<="1010";

--则计数值百位变成10,十位、个位变成0

ELSIFTCOU1="1001"ANDTCOU2="1001"THEN

--如果百位小于9,十位为9且个位为9的时候

TCOU1<="0000";TCOU2<="0000";TCOU3<=TCOU3+1;

--百位数值加1,十位、个位清零

ELSIFTCOU1="1001"THEN

--如果百位和十位都小于9且个位为9的时候

TCOU1<="0000";TCOU2<=TCOU2+1;

--个位清零,十位数值加1

ELSETCOU1<=TCOU1+1;--其他情况就是个位数值加1

ENDIF;

ENDIF;

ELSE--–如果时基信号为0,那么判断条件无效

TCOU1<="0000";TCOU2<="0000";TCOU3<="0000";

ENDIF;

ENDIF;

ENDIF;

ENDPROCESSCTRCOU;

OPUTCTR:

PROCESS(TRESET,TSIG)--控制数值输出的进程

BEGIN

IFTRESET='1'THEN

TKEEP1<="0000";TKEEP2<="0000";TKEEP3<="0000";

ELSE

IFTSIG'EVENTANDTSIG='0'THEN

--时钟下降沿触发输出各位数值

TKEEP1<=TCOU1;

TKEEP2<=TCOU2;

TKEEP3<=TCOU3;

ENDIF;

ENDIF;

ENDPROCESSOPUTCTR;

ENDONE;

锁存源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYLOCKIS

PORT(RESET:

INSTD_LOGIC;

LOCKIN:

INSTD_LOGIC;

LOCKOUT:

OUTSTD_LOGIC);

ENDLOCK;

ARCHITECTUREBEHAVEOFLOCKIS

SIGNALINLOCK:

STD_LOGIC;

BEGIN

PROCESS(RESET,LOCKIN)

BEGIN

IFRESET='1'THEN

INLOCK<='0';

ELSIFLOCKIN'EVENTANDLOCKIN='1'THEN

INLOCK<=NOTINLOCK;

ENDIF;

ENDPROCESS;

LOCKOUT<=INLOCK;

ENDBEHAVE;

显示模块源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDISPSELIS

PORT(DISP1:

INSTD_LOGIC_VECTOR(0TO3);

DISP2:

INSTD_LOGIC_VECTOR(0TO3);

DISP3:

INSTD_LOGIC_VECTOR(0TO3);

DOT:

INSTD_LOGIC_VECTOR(2DOWNTO0);

CLK:

INSTD_LOGIC;

SEL:

BUFFERSTD_LOGIC_VECTOR(2DOWNTO0);

SEG:

BUFFERSTD_LOGIC_VECTOR(7DOWNTO0));

END;

ARCHITECTUREONEOFDISPSELIS

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFSEL="010"THENSEL<="000";

ELSESEL<=SEL+1;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(SEL,DISP1,DISP2,DISP3,DOT)

BEGIN

--CASESELIS

IFSEL="000"THEN

IFDISP1="0000"THENSEG<="00111111";

ELSIFDISP1="0001"THENSEG<="00000110";

ELSIFDISP1="0010"THENSEG<="01011011";

ELSIFDISP1="0011"THENSEG<="01001111";

ELSIFDISP1="0100"THENSEG<="01100110";

ELSIFDISP1="0101"THENSEG<="01101101";

ELSIFDISP1="0110"THENSEG<="01111101";

ELSIFDISP1="0111"THENSEG<="00000111";

ELSIFDISP1="1000"THENSEG<="01111111";

ELSIFDISP1="1001"THENSEG<="01101111";

ENDIF;

ELSIFSEL="001"THEN

IFDISP2="0000"THENIFDOT="010"THENSEG<="10111111";ELSESEG<="00111111";ENDIF;

ELSIFDISP2="0001"THENIFDOT="010"THENSEG<="10000110";ELSESEG<="00000110";ENDIF;

ELSIFDISP2="0010"THENIFDOT="010"THENSEG<="11011011";ELSESEG<="01011011";ENDIF;

ELSIFDISP2="0011"THENIFDOT="010"THENSEG<="11001111";ELSESEG<="01001111";ENDIF;

ELSIFDISP2="0100"THENIFDOT="010"THENSEG<="11100110"

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字式 频率计 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx