整理计算机组成原理复习要点.docx

整理计算机组成原理复习要点.docx

- 文档编号:6112847

- 上传时间:2023-01-03

- 格式:DOCX

- 页数:19

- 大小:1.13MB

整理计算机组成原理复习要点.docx

《整理计算机组成原理复习要点.docx》由会员分享,可在线阅读,更多相关《整理计算机组成原理复习要点.docx(19页珍藏版)》请在冰豆网上搜索。

整理计算机组成原理复习要点

按照国家规定实行审批制的建设项目,建设单位应当在报送可行性研究报告前报批环境影响评价文件。

按照国家规定实行核准制的建设项目,建设单位应当在提交项目申请报告前报批环境影响评价文件。

按照国家规定实行备案制的建设项目,建设单位应当在办理备案手续后和开工前报批环境影响评价文件。

安全评价的基本原则是具备国家规定资质的安全评价机构科学、公正和合法地自主开展安全评价。

价值=支付意愿=市场价格×消费量+消费者剩余

(四)建设项目环境影响评价资质管理

3.规划环境影响报告书的审查效力

6.提出安全对策措施建议

环境的两个特点:

2.建设项目环境影响评价文件的报批时限

1.建设项目环境影响评价文件的报批

(3)评价单元划分应考虑安全预评价的特点,以自然条件、基本工艺条件、危险、有害因素分布及状况便于实施评价为原则进行。

计算机组成原理复习要点

一、题型分布

选择题20分;填空题30分;判断题10分;计算题20/25分;简答题20/15分

二、每章重点内容

第一章概述

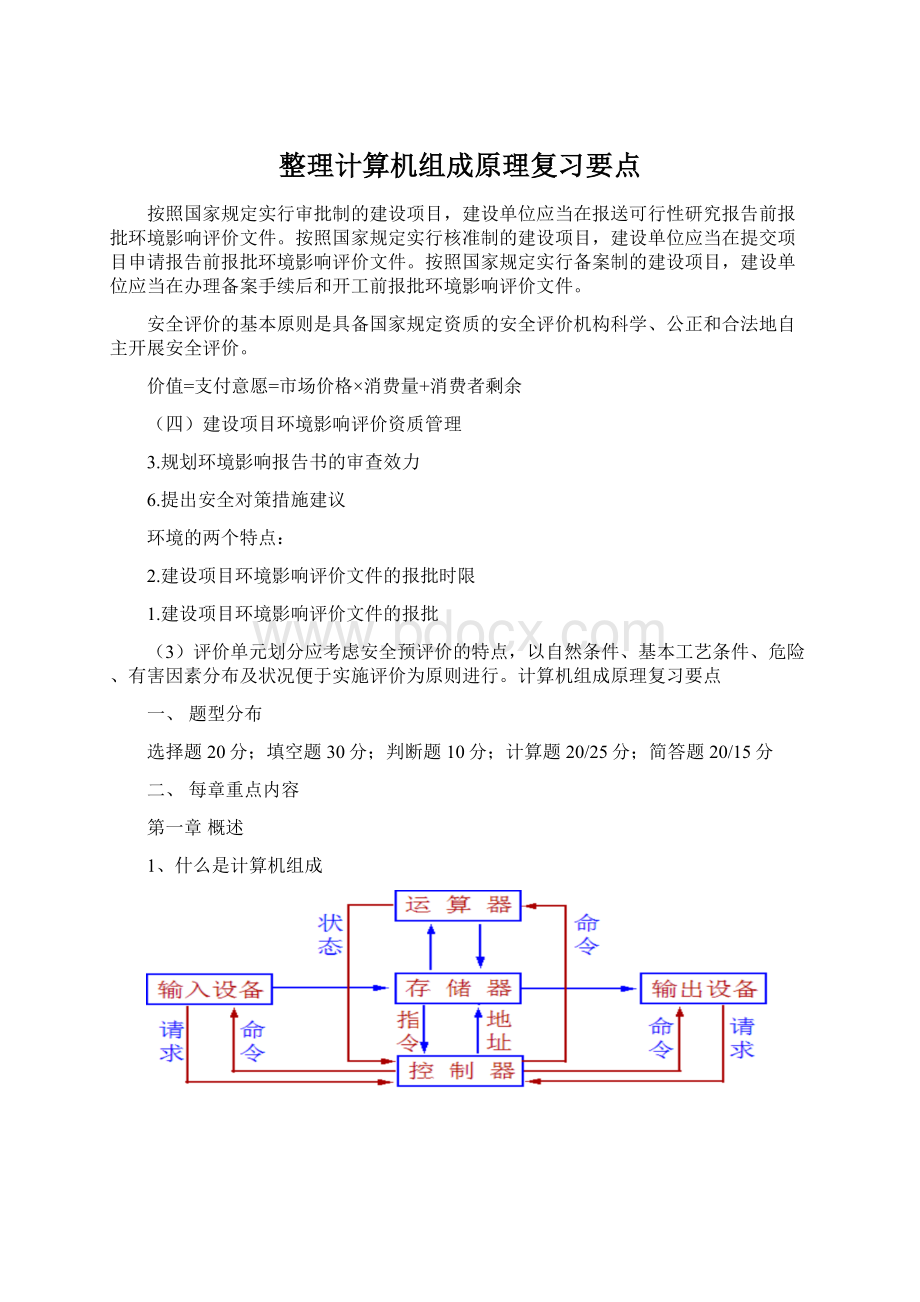

1、什么是计算机组成

2、诺依曼体系结构计算机的特点

(1)硬件由五大部份组成(运算器、控制器、存储器、输入设备、输出设备)。

(2)软件以2#表示。

(3)采用存储程序

所有的程序预先存放在存储器中,此为计算机高速自动的基础;

存储器采用一维线性结构;

指令采用串行执行方式。

控制流(指令流)驱动方式;

(4)非诺依曼体系结构计算机

数据流计算机

多核(芯)处理机的计算机

3、计算机系统的层次结构

(1)从软、硬件组成角度划分层次结构

(2)从语言功能角度划分的层次结构

虚拟机:

通过软件配置扩充机器功能后,所形成的计算机,实际硬件并不具备相应语言的功能。

第二章数据表示

1、各种码制间的转换及定点小数和定点整数的表示范围

(1)原码:

计算规则:

最高位表示符号位;其余有效值部分以2#的绝对值表示。

如:

(+0.1011)原=0.1011;(-0.1001)原=1.1001

(+1011)原=01011;(-1001)原=11001

注意:

在书面表示中须写出小数点,实际上在计算机中并不表示和存储小数点。

原码的数学定义

若定点小数原码序列为X0.X1X2...Xn共n+1位数,则:

X原=X当1>X≥0

X原=1-X=1+|x|当0≥X>-1

若定点整数原码序列为X0X1X2...Xn共n+1位数,则:

X原=X当2n>X≥0

X原=2n-X=2n+|x|当0≥X>-2n

说明:

在各种码制(包括原码)的表示中需注意表示位数的约定,即不同的位数表示结果不同,如:

以5位表示,则(-0.1011)原=1.1011

以8位表示,则(-0.1011)原=1.1011000

0的原码有二种表示方式:

小数:

(+0.0000)原=0.0000,(-0.0000)原=1.0000

整数:

(+00000)原=00000,(-00000)原=10000

符号位不是数值的一部分,不能直接参与运算,需单独处理。

约定数据位数的目的是约定数据的表示范围,即:

小数:

-1 整数: -2n (2)反码: 计算规则: 正数的反码与原码同;负数的反码是原码除最高位(符号位)外,各位求反。 如: 正数: (+0.1011)原=(+0.1011)反=0.1011; 负数: (-0.1001)原=1.1001,则(-0.1001)反=1.0110 反码的数学定义 若定点小数反码序列为X0.X1X2...Xn共n+1位数,则: X反=X当1>X≥0 X反=(2-2-n)+X当0≥X>-1 若定点整数反码序列为X0X1X2...Xn共n+1位数,则: X反=X当2n>X≥0 X反=(2n-1)+X当0≥X>-2n (3)补码: 计算规则: 正数的补码与原码同;负数的补码是反码的最低加1。 如: 正数: (+0.1011)原=(+0.1011)反=(+0.1011)补=0.1011; 负数: (-0.1001)原=1.1001 (-0.1001)反=1.0110 (-0.1001)补=1.0111 数学定义 (X)补=M+X(MODM) 其中: M表示模,即容器的最大容量。 若定点小数补码序列为X0.X1X2...Xn共n+1位数,则M=2; 若定点整数补码序列为X0X1X2...Xn共n+1位数,则M=2n+1 2、为什么计算机中数值类型的数据以补码表示 补码的符号位是数值的一部分,可以参与运算。 0的补码表示具有唯一性。 补码的表示范围比原码、反码大。 3、常见寻址方式的特点 (1)寻址方式: 获得指令或操作数的方式。 (2)指令寻址: 由程序计数提供即将要执行的指令的地址。 (3)操作数寻址: 与具体的寻址方式有关。 操作数寻址方式应说明是源操作数还是目标操作数的寻址方式。 4、采用多种寻址方式的目的(缩短指令长度,扩大寻址空间,提高编程灵活性) 缩短指令长度,扩大寻址空间,提高编程的灵活性。 5、如何减少指令中地址数的方法 采用隐地址(隐含约定)可以简化指令地址结构,即减少指令中的显地址数。 6、外设的编址方式(在任何一种方式每个外设都有一个独立的地址) (1)I/O与主存统一编址,即I/O是看作是主存的延伸。 (2)I/O与主存单独编址: I/O编址到设备级,即一个I/O只有一个地址。 I/O编址到寄存级,即一个I/O有多个地址。 7、指令系统优化的趋势(CISC、RISC) (1)CISC(复杂指令系统计算机) 从编程角度出发,希望指令系统中包含的指令尽可能多,每条指令中的操作信息尽可能多。 该类指令系统一般包含300-500指令。 为提高机器效率,采用了向量化、超标量、超长指令字等技术。 (2)指令系统的发展趋势 早期: 面向用户编程,采用CISC技术 现代: 面向系统、向高级语言靠近,采用RISC技术 (3)实际上CISC和RISC均是当前的发展(优化)趋势 第三章存储器 1、存储器的按工作原理和存取方式的分类 (1)物理原理分类: A、磁芯B、半导体存储器C、磁表面存储器D、光盘存储器E、其它存储器 (2)存取方式的划分: A、随机存取存储器(RAM)B、只读存储器(ROM)C、顺序存取存储器(SAM)D直接存取存储器(DAM) 2、存储器的三级层次结构及各层次的功能 (1)主存: 基本要求: 随机访问、工作速度快、具有一定容量; 功能: 存放当前执行的指令和数据。 (2)外存: 基本要求: 容量大、成本低、一定的速度 功能: 长期保存数据;作为主存的外援存储器。 外存也可采用多级存储结构。 (3)cache: 基本要求: 速度足够快、一定容量 功能: CPU与主存的缓冲,匹配主存与CPU的速度。 内容: 是当前主存中最活跃数据的副本。 内容形成的依据: 程序局部性原理: 时间和空间局部性。 3、静态与动态存储器间的区别、动态存储器为什么还需要刷新及刷新有分类 (1)根据信息表示方式分为: 动态存储器(DRAM): 以电容中的电荷表示信息,需动态刷新; 静态存储器(SRAM): 以双稳态信息。 (2)需动态刷新: 因为动态存储器是依靠电容上的存储电荷暂存信息,而电容上存储的电荷会逐渐减变弱所以需要刷新。 (3)刷新的分类: A、集中刷新B、分散刷新C、异步刷新。 4、校验码: 奇偶、循环校验码(CRC)计算 (1)奇/偶校验: 奇/偶校验: 使校验码中“1”的个数和为奇/偶数,主要用于主存校验。 例: 有效信息: 01101011,则 奇校验码: 011010110 偶校验码: 011010111 (2)循环校验码 A、编码原理: 现假设有: 有效信息: M;除数G(生成多项式) 有: M/G=Q+R/G 此时,可选择R作为校验位,则MR即为校验码。 B、校验原理: (M-R)/G=Q+0/G 说明: 以接收到的校验码除以约定的除数,若余数为0,则可认为接收到的数据是正确的。 例: 有效信息1101,生成多项式样1011,求循环校验码 解: 有效信息1101(k=4),即M(x)=x3+x2+x0 生成多项式1011(r+1=4,即r=3),即G(x)=x3+x1+x0 M(x)·x3=x6+x5+x3,即1101000(对1101左移三位) M(x)·x3/G(x)=1101000/1011=1111+001/1011 即1010的CRC是: 1101001 循环校验码的来源 余数与出错序号间处理存在对应模式,该模式只与只与码制和生成多项式有关,与具体的码字无关。 生成多项式满足的条件: 任一位发生错误都应使余数不为0; 不同的位发生的错误余数应不同。 用的生成多项式: CCITT: G(x)=x16+x15+x2+1 IEEE: G(x)=x16+x12+x5+1 5、存储器的扩展 (1)位扩展: 例: 2K×4芯片组成2K×8 特点: (1)片选信号连接在一起,二个芯片分别提供高低位的数据; (2)芯片的地址线直接与AB按位连接。 (2)字扩展 例: 2K×4芯片组成4K×4 特点: AB高位地址通过译码形成芯片的片选信号; AB低位地址通过译码连接芯片的低位地址; (3)综合扩展 例: 4K×4芯片组成16K×8 6、数据传输率的计算 R= (单位bps) 7、提高存储性能(速度、容量)的措施 A、双端口存储器,B、并行主存系统C、高速缓存D、虚拟存储E、相联存储技术等。 8、高速缓存的功能及替换算法 (1)高速缓存的功能: 提供的是cpu与内存的一个缓存。 (2)替换算法: 1先进先出算法(FIFO)2近期最少使用算法(LRU) p命中率= 9、Cache与内存在直接映像方式中怎样将内存地址转换为Cache地址 A、直接映像B、全相联映像C、组相联映像。 10、虚拟存储器的分类 A、页式虚存储器B、段式虚拟存储器C、段页式虚拟存储器。 第四章CPU 1、为什么会产生溢出、及溢出的解决方法、正负溢出的概念 (1)产生溢出的原因: 需表示的数据或运算结果超出了正常表示范围 (2)溢出的解决方法: 多符号位; (3)正溢出: 两个正数相加而绝对值超出允许的表示范围; (4)负溢出: 两个负数相加而绝对值超出允许的表示范围。 2、补码加减法的依据 X补+Y补=(X+Y)补和X补-Y补=X补+(-Y)补。 3、串行和并行加法的原理 串行加法原理如下: C1=G1+P1C0;其中C0=0 C2=G2+P2C1 ···· Cn=Gn+PnCn-1 ∑i=Ai⊕Bi⊕Ci-1 并行加法原理如下: C1=G1+P1C0 C2=G2+P2C1=G2+P2G1+P2P1C0 C3=G3+P3C2=G3+P3G2+P3P2G1+P3P2P1C0 C4=G4+P4C3 =G4+P4G3+P4P3G2+P4P3P2G1+P4P3P2P1C0 ···· 而∑i=Ai⊕Bi⊕Ci-1. 4、一位原码乘法的计算及运算特点 (1)数学原理: 两个原码数相乘,其乘积的符号为相乘两数符号的异或值,数值等于两数绝对值之积。 假设[X]原=X0.X1X2..Xn, [Y]原=Y0.Y1Y2..Yn,则有: [X·Y]原=(X0⊕Y0).[(X1X2..Xn)·(Y1Y2..Yn)] (2)算法: 假设X=0.X1X2..Xn,Y=0.Y1Y2..Yn,即均为正纯小数 X·Y=X·0.Y1Y2..Yn =X·(2-1Y1+2-2Y2+...+2-n+1Yn-1+2-nYn) =X·(2-nYn+2-n+1Yn-1+...+2-2Y2+2-1Y1) =(..((0+YnX)2-1+Yn-1X)2-1)+...)+Y2X)2-1)+Y1X)2--1) 根据上述计算过程,可得算法如下: A0=0 A1=(A0+YnX)2-1 A2=(A1+Yn-1X)2-1 ... An-1=(An-2+Y2X)2-1 An=(An-1+Y1X)2-1 积X·Y=An (3)运算特点 符号位和绝对值分别独立运算。 5、主机与外设间的连接方式 (1)辐射型 (2)总线型(3)通道型 6、数据传送方式 (1)以打印机为例说明中断方式数据的传输过程 (2)DMA方式的特点及应用 DMA方式的特点: 传送速率快,操作简单;应用: 高速外部设备与主存储器之间的简单批量数据传送。 中断的响应过程、区别中断处理与中断服务 7、中断的响应过程、区别中断处理与中断服务 (1)中断的响应过程 ①置位中断优先级有效触发器,即关闭同级和低级 中断: ②调用入口地址,断点入栈,相当于LCALL指令; ③进入中断服务程序。 (2)中断处理就是执行中断服务程序,从中断入口地址开始执行,直到返回指令(RETI)为止。 此过程一般包括三部分内容,一是保护现场,二是处理中断源的请求,三是恢复现场。 (3)中断服务是要完成处理的事务,用户根据需要编写中断服务程序,程序中要注意将主程序中需要保护的寄存器内容进行保护 8、控制器的功能 CPU内部控制功能的寄存器及相应的功能 硬件系统时序层次的划分及各层次次的含义 控制器的分类及各自的优缺点 指令流程(MOV和运算类双操作数指令) 微程序控制器的基本思想 9、CPU内部控制功能的寄存器及相应的功能 (1)PC: 程序计数器,用来指示指令在存储器中的存放位置。 (2)IR: 指令寄存器,用来存放当前正在执行的指令,它的输出包括操作信息、地址信息等。 (3)PSW: 程序状态寄存器,用来记录现行程序的运行状态和指示程序的工作方式。 10、硬件系统时序层次的划分及各层次次的含义 (1)指令周期: 执行一条指令所需的时间,一般由若个个机器周期(工作周期)组成,是从取指令、分指令到执行指令完所需的全部时间。 (2)工作周期: 完成一个阶段性的任务所需时间。 (3)时钟周期: 完成一个基本操作所需时间。 (4)定时脉冲: 启停控制逻辑的时钟脉冲。 (工作脉冲: 决定一个周期的长短) 11、控制器的分类及各自的优缺点 (1)组合逻辑控制 A、优点: 思路简单、可用于实现任一指令系统。 B、缺点: *控制器的核心零乱、繁琐,设计效率低,检查调试困难。 *不易扩展和修改。 (2)微程序控制 A、优点: *用规整的存储逻辑结构代替硬连逻辑,有利于设计自动化。 *易于修改与扩展,灵活,通用性强。 *适用性作素列机的控制器。 *可靠性高,易于诊断与维护。 B、缺点: *速度慢,效率低。 *由于增加了相关的微程序控制部件,成本较高。 12、指令流程(MOV和运算类双操作数指令) (1)MOV 3、DT 由目的操作数的寻址方式确定DT的指令流程: 若目的数在内存中,则将目的数的地址送到MAR;若目的数在R中,则省略。 4、ET 由源操作数、目的操作数的寻址方式及操作码共同确定ET的指令流程。 源数可在R中(SR)或内存中(SR); 目的数可在R中(DR)或内存中(DR)。 由源数和目的数的位置可以有下列四种类型: (2)双操作数指令 包括: ADD、SUB、OR、AND、EOR。 双操作数指令的FT和ST的流程与MOV指令完全相同。 下面只描述DT及ET的指令流程。 1、DT 由目的操作数的寻址方式确定DT的指令流程: 若目的数在内存中,则将目的数送到D;若目的数在R中,则省略。 2、ET 由源操作数、目的操作数的寻址方式及操作码共同确定ET的指令流程。 源数可在R中(SR)或内存中(SR); 目的数可在R中(DR)或内存中(DR)。 由源数和目的数的位置可以有下列四种类型。 其中: Rs表示源寄存器;Rd表示目的寄存器。 13、微程序控制器的基本思想 (1)机器指令由微程序解释;微程序由微指令组成,每条微指令中可包含多个微命令;微命令控制实现微操作。 (2)微指令以代码(微码)存储在ROM中,该ROM称为控制存储器(CM)。 9、I/O系统 1、总线的分类及接口的分类 (1)总线的分类 A、按据传送格式分类: 串行总线;并行总线 B、按时序控制方式分类: 同步总线;异步总线 (2)接口的分类 A、按数据传送格式划分 并行接口: 接口与系统总线及I/O间均以并行方式传送数据。 串行接口: 接口与I/O间以串行方式,而与系统总线间以并行方式传送数据。 B、按时序划分 同步接口: 与同步总线连接的接口,接口与系统总线间的数据传送由统一的时序信号(由CPU或专门的系统总线时序信号)控制。 异步接口: 与异步总线连接的接口,接口与系统总线间的传送采用异步应答的工作方式。 C、按信息的传送控制方式划分 中断接口、DMA接口、磁盘存储接口等。 ***I/O接口的基本功能 (1)寻址: 将地址信息译码为I/O或接口中的寄存器的选中信号。 (2)数据传送与缓冲(速度匹配) (3)数据格式变换、电平变换等预处理 (4)控制逻辑: 接口对主机发送的命令字进行解释,并将产生的操作命令发送给I/O; 将I/O及接口的状态信息送回CPU。 如在中断接口中有中断请求信号产生、中断屏蔽、优先排队等部件。 2、总线的概念及分时共享的含义、总线的组成 总线(Bus)是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束,按照计算机所传输的信息种类,计算机的总线可以划分为数据总线、地址总线和控制总线,分别用来传输数据、数据地址和控制信号。 总线是一种内部结构,它是cpu、内存、输入、输出设备传递信息的公用通道,主机的各个部件通过总线相连接,外部设备通过相应的接口电路再与总线相连接,从而形成了计算机硬件系统。 在计算机系统中,各个部件之间传送信息的公共通路叫总线,微型计算机是以总线结构来连接各个功能部件的。 3、PCI总线的仲裁方式 当多个设备竞争总线时,由总线仲裁器进行仲裁,在微机中就是南北桥芯片组。 仲裁方式分集中和竞争二种方式。 (1)集中式仲裁: 分配原则是: 优先级高的设备可以剥夺优先级低的设备的总线使用权。 当仲裁器接收到总线请求时,就发出总线授权信号。 设备的优先级由设备和仲裁器的逻辑距离决定。 当设备较多时,可采用分级仲裁方式。 (2)竞争式仲裁 分配原则: 优先级不同的设备同时申请总线,则分配给高优先级的设备; 先来先占用: 谁先抢占总线,只要该设备没有释放总线,则其它优先级高的设备不能强行占用总线。 4、中断接口的模型及工作过程 中断接口的模型 (1)设备选择电路 是一个译码器,用于选择接口中的某一个寄存器。 (2)命令字寄存器 用于接收CPU发送的命令字,一般用于初始化接口,如数据的输入/出方向、工作方式(R或W)等。 (3)状态字寄存器 用以记录、反映设备与接口的运行状态,作为CPU执行I/O程序的依据。 (4)数据缓冲寄存器 作为主机与I/O间数据传送的缓冲。 其容量称为缓冲深度。 若对缓冲深度要求较高,则可采用半导体存储器作为缓冲区。 (5)其它控制逻辑 接口不同,则该逻辑不同,属接口中不规整的部分,一般有如下部分: A、中断请求IRQ的产生 B、与主机间的应答逻辑 C、控制时序,包括振荡电路、分频电路。 D、面向设备的某些特殊逻辑。 如对机电性的设备所需的电机的启动、停止、正转、反转、加速,数据格式的转换,电平信号的转换等 E、智能控制器。 功能复杂的接口,常使用通用的微处理器、单片机或专用控制器等芯片,与半导体存储器构成可编程的控制器。 (6)中断控制器 现通常采用8259A芯片。 ****模型接口的抽象工作过程: (1)初始化接口与中断控制器: CPU调用程序或系统初始化时完成 (2)启动外设: 通过专门的启动信号或命令字,使接口状态为B=1、D=0。 (3)设备向中断控制器提出中断请求: 设备准备好或完成一次操作(数据传送),使接口状态为: B=0、D=1,据此形成中断请求信号IRQi。 (4)中断控制器向CPU提出中断请求: IRQi送中断控制器8259A,经屏蔽优先,向CPU发出公共请求INT,同时形成中断类型码。 (5)CPU响应: CPU经中断判优后向8259A发回响应信号INTA,CPU从DB取回中断类型码。 (6)CPU在中断周期IT执行中断隐指令操作,转入中断服务程序。 第六章I/O设备 1、键盘对按键识别方式的分类 软件扫描、硬件扫描 2、显存容量的计算 显存容量应该能保证一帧图像的存储。 下面以例说明: 例: 显示器在字符方式下: 分辨率25行×80列,颜色256种。 显示字符集有256个字符;在图形方式下分辨率1024×1024,颜色216种 解: (1)字符方式下: 256个字符集中的每个字符需8位(1B)表示,256种颜色需8位(1B)表示,则: 基本缓存: 25×80×8/8=2000B,2KB 属性缓存: 2KB×1=2KB 显存容量至少: 4KB (2)图形方式下: 颜色216种需用16位(2B)表示 显示屏上共有: 1024×1024=220个点 每个点所属性需2B表示 则所需的属性显存: 220×2B=221B=2MB 显存容量至少: 2M 注意: 在图形方式下无基本显存 三、计算题的例题 1、原码的一位乘法 见上面复习重点的第四章CPU的第4点 2、循环校验码 见上面复习重点的第三章存储器的第4点 3、将内存地址转入高速缓存 现有一个cache,其容量为1kB,其页大小为128B,若cache与内存的地址映像方式为直接映像,且内存编址方式为字节,现有一内存单元地址为1a2b3cH,若该单元数据已调入cache,试问: 该单元在cache中的地址(页号和页内地址)。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 整理 计算机 组成 原理 复习 要点

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx