代码审查记录.docx

代码审查记录.docx

- 文档编号:6095383

- 上传时间:2023-01-03

- 格式:DOCX

- 页数:6

- 大小:240.78KB

代码审查记录.docx

《代码审查记录.docx》由会员分享,可在线阅读,更多相关《代码审查记录.docx(6页珍藏版)》请在冰豆网上搜索。

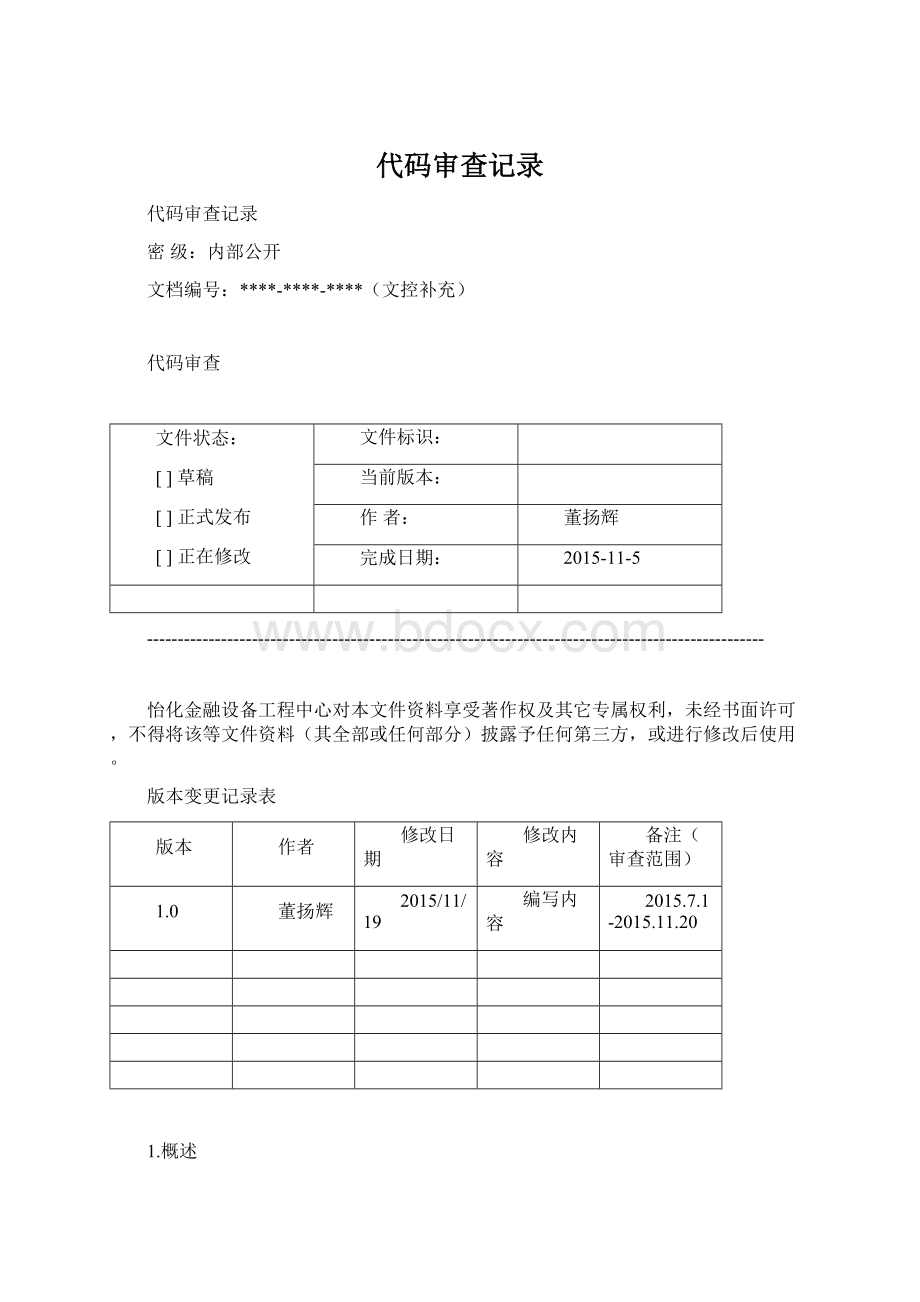

代码审查记录

代码审查记录

密级:

内部公开

文档编号:

****-****-****(文控补充)

代码审查

文件状态:

[]草稿

[]正式发布

[]正在修改

文件标识:

当前版本:

作者:

董扬辉

完成日期:

2015-11-5

----------------------------------------------------------------------------------------------------

怡化金融设备工程中心对本文件资料享受著作权及其它专属权利,未经书面许可,不得将该等文件资料(其全部或任何部分)披露予任何第三方,或进行修改后使用。

版本变更记录表

版本

作者

修改日期

修改内容

备注(审查范围)

1.0

董扬辉

2015/11/19

编写内容

2015.7.1-2015.11.20

1.概述

1.1.测试对象

由董扬辉所编写的所有代码。

时间节点为2015年7月1日至2015年11月20日。

1.2.测试目的

规范代码风格,不断提高代码质量。

包括:

(1)代码的风险评估和警告审计;

(2)代码的鲁棒性和可复用性评估;

(3)代码的易读性和可维护性;

(4)代码风格的统一;

1.3.测试流程

1.4.代码的工具测试和人工检查

(1)ISE编译环境或Codifferous

(2)资深专家

2.代码审查结果统计

2.1.风险等级

一般

2.2.代码审查结果

功能实现;可读性还需加强;代码风格还需修改。

2.3.代码审查详解

2.3.1寄存器定义不当

FPGA在上电时全局复位时钟将会实现寄存器定义时的值。

但是这种做法并不值得推荐,我们需要每个寄存器进行局部复位。

即在每个块语句复位逻辑中赋初值。

详见WP272(v1.0.1)March7,2008--< ThinkLocal,NotGlobal>>. 2.3.2不在if语句中进行过多运算 在模块中只要一个always块或例化元件中没有在前一模块中用到。 则可以将变量定义到每个块或元件的前面,便于修改。 若是在变量存在交叉现象则必须在模块的顶端定义。 2.3.9半主时钟周期信号无法作为触发信号,但能记边沿 解决 2.4.1闪退 同一assign有多个分号会导致闪退。 2.4.2多个XDC约束规则 多个XDC约束规则 第一个约束文件优先读取,然后依次读取。 2.4.3XDC语法问题 语法错误会导致后面的管脚约束全部无效,在synthetic期间导致所在的模块全部被优化。 2.4.4编译问题 set_propertySEVERITY{Warning}[get_drc_checksNSTD-1] set_propertySEVERITY{Warning}[get_drc_checksRTSTAT-1] set_propertySEVERITY{Warning}[get_drc_checksUCIO-1] 在使用强制drc报警告情况下,一些意想不到被优化的模块相关的错误报告会转化为警告,导致有时无法查到具体哪个模块在什么期间被优化。 建议在约束文件没有任何问题的情况下使用错误强制转换为警告。 2.4.5编译问题 对同一信号进行约束,最后一条的有效性高于前一条。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 代码 审查 记录

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx