时序逻辑电路.docx

时序逻辑电路.docx

- 文档编号:6078229

- 上传时间:2023-01-03

- 格式:DOCX

- 页数:34

- 大小:1.22MB

时序逻辑电路.docx

《时序逻辑电路.docx》由会员分享,可在线阅读,更多相关《时序逻辑电路.docx(34页珍藏版)》请在冰豆网上搜索。

时序逻辑电路

6时序逻辑电路

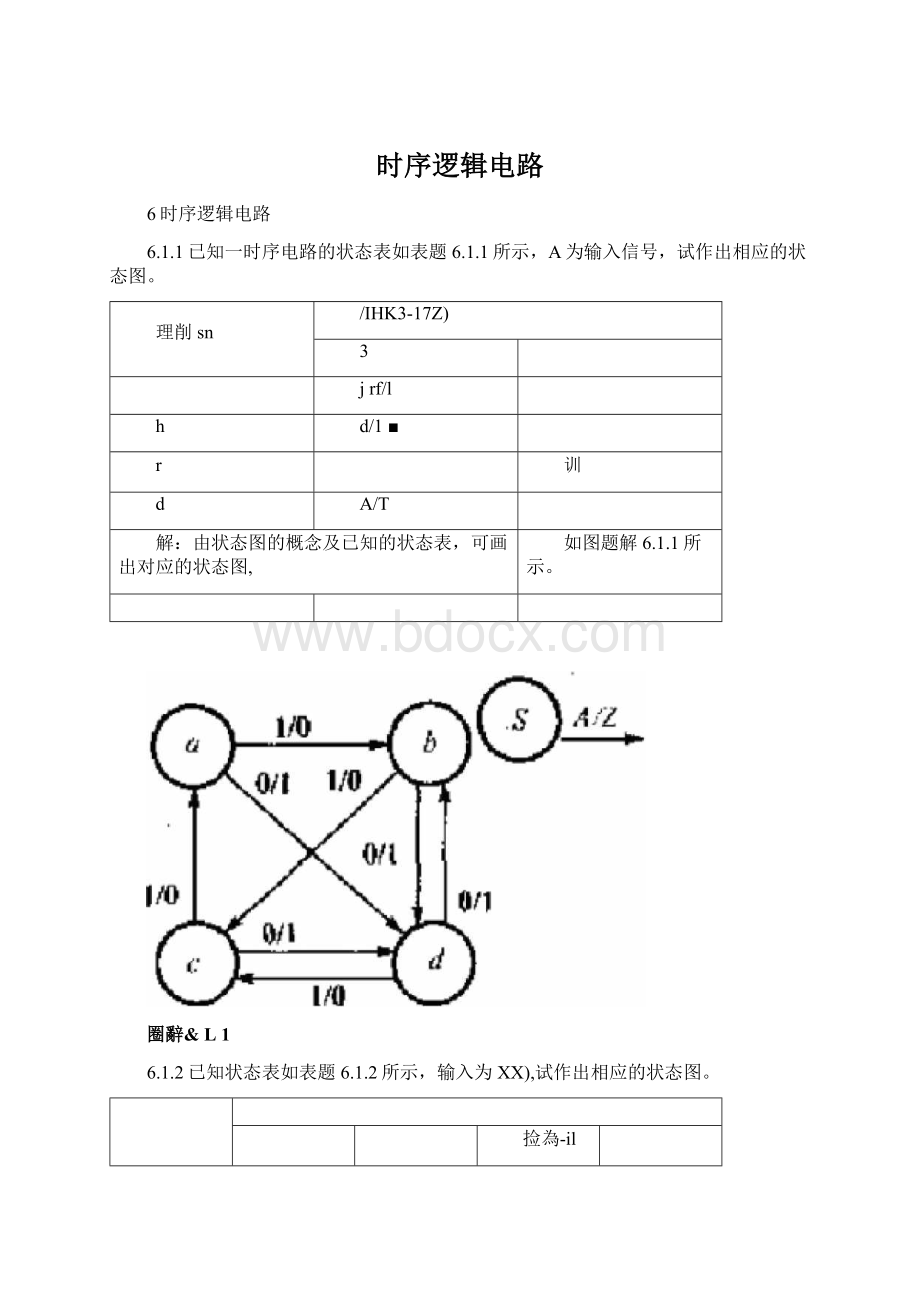

6.1.1已知一时序电路的状态表如表题6.1.1所示,A为输入信号,试作出相应的状态图。

理削sn

/IHK3-17Z)

3

jrf/l

h

d/1■

r

训

d

A/T

解:

由状态图的概念及已知的状态表,可画出对应的状态图,

如图题解6.1.1所示。

圈辭&L1

6.1.2已知状态表如表题6.1.2所示,输入为XX),试作出相应的状态图。

捡為-il

禺e

S|/l

Sj/I

sn;o

Si/1

1S./O

S3/l

Sj/i

$

L乂'

s2/o

S1/0

解:

根据表题6.1.2所示的状态表,作出对应的状态图如图题解6.1.2所示。

SO6.1.2

6.1.3已知状态图如图题6.1.3所示,试列出它的状态表。

阳龜6.1.3

解:

按图题6.1.3列出的状态表如表题解6.1.3所示。

7

01

I!

W

Sr/1

5,/J

S[

Sl/1

Si/»

Sl/O

电路将按图题解6.1.5所示的顺序改变状态,因而对应的输出序列为Z=011010。

bl

S.1.5

6.1.6已知某时序电路的状态表如表题6.1.6所示,输入A,试画出它的状态图。

如果电

路的初始状态在b,输入信号A一次是0、1、0、1、1、1、1,试求出其相应的输出。

X

1

/输出

■

1

a/0

b

fl/J

J/l

£

d

『/■

e

b/1

fl/1

解:

根据表题6.1.6所示的状态表,可直接画出与其对应的状态图,如图题解6.1.6(a)

当从初态b开始,依次输入0、1、0、1、1、1、1信号时,该时序电路将按图题解6.1.6(b)所示的顺序改变状态,因而其对应的输出为1、0、1、0、1、0、1。

6.2同步时序逻辑电路的分析

6.2.1试分析图题6.2.1(a)所示时序电路,画出其状态表和状态图。

设电路的初始状态

为0,试画出6.2.1(b)所示波形作用下,Q和Z的波形图。

fa>

解:

由所给电路图可写出该电路的状态方程和输出方程,分别为

Q「1=A二Qn

X=~AQ

其状态表如表题解6.2.1所示,状态图如图题解6.2.1(a)所示,Q和Z的波形图如图题解

6.2.1(b)所示。

LJ—UL

Ji_n__rur

Z-Ir-1

(a)

6.2.2试分析图题6.2.2(a)所示时序电路,画出其状态表和状态图。

设电路的初始状态

为0,画出在图题6.2.2(b)所示波形作用下,Q和Z的波形图。

解:

由所给电路可写出该电路的状态方程和输出方程

Qn1二zQnZQn

=(AQnAQn)Qn(AQnAQn)Qn

nn

二AQAQn

二A

Z=A二Q

其状态表如表题解622所示,状态图如图题解622(a)所示,Q和Z的波形图如图题解

622(b)所示。

季jmrLrLnrLrLrLrL『

Qr-i

Mu

=l

丄,rIrn二

”

(b)

田"2J

、A

0I

<

i1/1

1

1

0/1

cjmrmjiTLTLrLn_

3

丄u1——

nnnn,

HKLX2 6.2.3试分析图题6.2.3所示时序电路,画出状态图。 解: 由图题623所示电路写出其状态方程组和输出方程,分别为 Qi Qon仁A Z二AQ°Qi 其状态表如表题解6.2.3所示,状态图如图题解6.2.3所示。 ajmrLrLrLnrLrLTL 图解6”2,3 画出状 624分析图题624所示电路,写出它的激励方程组、状态方程组和输出方程,态表和状态图。 解: 该电路的激励方程组为 状态方程组为 q? 1二Eq: nnnnn QO11=QiQ°AQiQlQgA) 输出方程为 Z二AQ1QO 6.2.4 根据状态方程组和输出方程可列出状态表,如表题解6.2.4所示,状态图如图题解 所示。 625分析图题625所示同步时序电路,写出各触发器的激励方程、电路的状态方程组和输出方程组,画出状态表和状态图。 解: 由图题6.2.5所示电路可写出各触发器的激励方程为 Jo=AKo=AQi Ji=AQoKi=A J2=AQgQiK2—1 该电路的状态方程组为 n Q;AQMQ2 Qin1=AQ;Q;AQ;=A(Q;Qo) nn Qo1二AQoAQ? Qo=A(Q;Q°) 输出方程为 Z二AQ2 6.2.5所示,状态图如图题解 根据状态方程组和输出方程列出该电路的状态表,如表题解 6.2.5所示。 (I1U 附解6.乱5 ini MO/I 001/9 101 *11/1 0111 11D U0;l oh/q 111 O(M/1 OH/D Ill/O 626试画出图题626(a)所示时序电路的状态图,并画出对应于CP的Q、Q和输出Z 的波形,设电路的初始状态为00。 oJ"LTLTLnTLrL 解: 该电路中的激励方程组为 状态方程组和输出方程分别为 n—n Q: 1=Q1Q0 Qo-Q1& Z=Q°CP 根据状态方程组和输出方程可列出该电路的状态表,如表题解6.2.6所示,状态图如图题解 6.2.6(a)所示。 图题解6.2.6(b)所示是Q、Q及Z的波形图。 n LO Q *0 CP 11 11 CP /CP 6.3 律JTrLTLTLrLrL 2—n_i~l i—n—n_ (b), B*cits 同步时序逻辑电路的设计 6.3.1用JK触发器设计一同步时序电路,其状态如表题6.3.1所示。 *043.1 QTQo bQT/Y A-\ M 01/0 11/1 01 ifl/o Wl 1U 11/1 on 11 Wi 1■ lfl/L 解: 所要设计的电路有4个状态,需要用两个JK触发器实现。 (1)列状态转换真值表和激励表 由表题6.3.1所示的状态表和JK触发器的激励表,可列出转换真值表和对各触发器的激励信号,如表题解6.3.1所示、 (2)求激励方程组和输出方程 由表题解6.3.1画出各触发器J、K端和电路输出端Y的卡诺图,如图题解6.3.1 A or1 Y AK】 & • D i 0 fl X 1 X 0 « 1 .i i 0 ] X 1 X 0 1 t f 0 < 1 ¥ 1K i 0 1 1| a 0 0 0 X 1-X I 1 Q • i 1 1 X 0 J X 1 D i J 0 X 1 J X 1 1 u 4 0 1 X' 1 X 1 J 1 l 1 1 X 1 X 1 (a)所示。 从而,得到化简得激励方程组。 Jo=Ko=1 =A二Q0 和输出方程 丫-Q1Qo 根据激励方程组和输出方程可画出电路图,如图题解6.3.1(b)所示。 632某同步时序电路的状态图如图题632所示,试写出用D触发器设计时的最简激励方程组。 图肚6.3.2 D触发器。 解: 由图题632所示状态图可知,实现该同步时序需要用三个 (1)根据状态图列出完全的状态转换真值表,如表题解6.3.2所示。 其中,状态图中未包含的状态为不出现的状态,其次态可用无关项X表示。 (2) 画出3个触发器的激励信号0、D、D0的卡诺图。 由于D触发器的特性方程为Q计=D,所以可由状态转换真值表直接画出这3个卡诺图,如图题解6.3.2所示。 图常6.3.2 3-1 QJOf05 QT5 gg 011 0 1 Q 010 j 1 0 11G 1 4 1fl0 1 4 1 1■4 0 V J 0fl1 u 1 1 (2)由卡诺图得到最简激励方程组 n D2二Qo n D1二Q2 其状态图如图题6.3.3所示,要 6.3.3试用上升沿触发的JK触发器设计一同步时序电路, 求电路使用的门电路最少。 解: 图题633所示的状态图有00、01、10、11四个状态,可用两个上升沿触发的JK触发 器实现。 设两个触发器的输出为Q、Q0,输入信号为A,输出信号为Y。 (1)根据图题6.3.3所示状态图和JK触发器的激励表,可直接列出相应的状态转换真值表和激励信号,如表题解6.3.3所示。 A 0105 创 I1 Kj h 氐 0 0 1 e 0 0 0 X 0 X 0 0 1 1 1 1 i X X n 0 J 0 0 0 o X 1 1 X 打 1 1 i 1 i X I X D 1 即 1 i 1 n 0 X 1 X 1 1 0 1 0 0 X X 0 1 1 i 0 i X 1 0 X 1 1 1 j a 1 X 1 X I (2)画出激励信号的卡诺图,如图题解6.3.3(a)所示。 D U a : 1 11 ■1 01 *X1 11 11 X X X X 1X 1■ ■■ 1*1 1! 111 %*斗,■■ Q 0 (3) 2/ € L1 ■■■■円 1•■■4 X: 」 ■■■■■ X X X 0 0 n X. X X ..■■■I : X a (3)由卡诺图得到最简激励方程组 Jo=AQ0K1=AQ0 ]Ji=AQiKo=AQi 和输出方程 Y=AQiQiQo (4)根据激励方程组和输出方程画出逻辑电路图,如图题解633(b)所示。 *11fc-3.4(b) A 「QT⑴厂 0 Q 0 0 0 P 0 4 1 e 1 ft 0 1 0 i Q V « ) 1 0 1 a 1 0 1 0 4 0 1 0 1 0 4 L 1 1 ft X X X 1 ! 1 X X X 6.4异步时序逻辑电路的分析 641—时序电路如图题641(a)所示,试画在CP作用下,Q、Q、Q和Z端的波形,设各触发器的初态均为零。 cp-TLTLrLrLrLrr (bi 解: 图题641所示电路是异步时序电路。 (1)列出各逻辑方程组 1根据逻辑图列出各触发器时钟信号的逻辑表达式 CP)=CR=CP二Q2 (当Q2=0时,对于每个CP上升沿,CPo=CPi=1;当Q2=1时,对于每个CP下降沿, CPo丸口=1) 2输出方程 Q1 3 激励方程组 4 状态方程组 (2)列出状态表,画出状态图 根据状态方程组、输出方程及各触发器的CP表达式可列出该电路的状态表,如表题解6.4.1 所示。 具体推导方法如下: 由于CR)=cp2二CP二Q2,所以当Q=0时,对应于每个CP上升沿,cp0二cp2=1;当Q=1时,对应于每个CP下降沿,cp0二cp2=1。 而cp2对应于Q1 上升沿,即对应于Q由1变0时为1。 对表中的每一行,首先由Q: Q0推导出Q: +Qn+,然后根据Q是否从1跳变到0来确定cp2是否为1,再决定Q;十。 最后,根据Q1决定Z。 逐行 类推,得到完全状态表。 然后根据表中状态的变化顺序,画出完全状态图,如图题解 641 (a)所示。 由于输出Z值取决于Q1,故写入圆圈内。 i.4.1 cp^cPL-cpea CPt-Q; I ODl 0 1 001 州 0 J 011 100 0 O1J 1W 0 100 101 1 ] 1D3 no 1 I 11C 000 0 111 MX) 0 (3)画出波形图 可按状态图的变化顺序,画出Q、Q、Q和Z对应于图题6.4.1(b)所示CP的波形图,如图题解6.4.1(b)所示。 这里需要特别注意: 因为CP=CP=CP®Q,因此,要根据Q的逻辑值正确确定状态变化所对应的CP脉冲沿。 6.4.2分析图题6.4.2所示时序电路[CP脉冲同图题6.4.1(b)]。 存^TLTLrLrVVrL 外JTrLrLTLrLTL (b) Eg6+4.2 (1)写出各触发器的CP信号方程和激励方程。 (2)写出电路的状态方程组和输出方程。 (3)画出状态表及状态图。 (4)画出电路的时序图。 解: (1)根据逻辑图写出各触发器的CP信号表达式和激励方程组 ① 各触发器的时钟信号表达式 CP O=CP=CP( 对于每个CP上升沿,CPo=CP1=1) CP 2=Q( 对于Q上升沿,cp2=1) ② 激励方程组 Jo=Q1 Ko=1 J1-Q2Q0 K^1 (2)写出电路的状态方程组和输出方程组 ①状态方程组 n'1 Q2 q21 n・1 Q2 —n (J2Q2K2Q;)cp2Q;cp2=Q2cp2Q2ncp2 —n—n—n (J1Q1K1Q1n)cp1Q1ncp^Q2Q1Q0cp1Q1ncp1 nnnnnn— (J0Q0'K0Qo)cpoQ0cp0=Q1Q0cpo'Qocp0 ②输出方程 Z=Q2Q0 (3)列出状态表,画出状态图根据状态方程组、输出方程及各触发器始终信号cpn可列出该电路的状态表,如表题解642 所示。 具体方法如下: 由于相应于每个CP上升沿cp0=Cp2=1,所以对表中的每一行,首先由Q2Q1nQ01推导出Q;'Q01,最后确定Z。 逐行类推,得到完全状态表。 表中状态的变换 顺序为000T101T100T001T010T000,据此画出完全状态图,如图题解6.4.2(a)所示。 由于输出Z只取决于QQ,故写入圆圈内。 (4)画出电路的时序图 可按状态图的变化顺序,画出Q、Q、Q和Z对应于图题6.4.1(b)所示CP的时序图,如 图题解6.4.2(b)所示。 QlQQfl z OQQ iai 于 0 晌 01* 0 a Old ODO • 0 411 1001 a 100 ori 0 *« 0 1 UD lOfr 0 0 111 100 0 6.5 若干典型的时序逻辑集成电路 解: 当启动信号端输入一低电平时,使Si=1,这时有So=Si=1,移位寄存器74HC194执行并 仃输入功冃能,Q3Q2Q1Q0=D3D2D1D0=1110。 启动信号撤消后,由于Qo=0,经两级与非门后,使S=0,这是有SSo=O1,寄存器开始执行右移操作。 在移位过程中,因为Q、Q2、Q1、 Qo中总有一个位0,因而能够维持SS=01状态,使右移操作持续进行下去。 其尾翼情况如图题解6.5.1所示。 由图题解6.5.1可知,该电路能按固定的时序输出低电平脉冲,是一个四相时序脉冲生产电路。 )2345 CpJTJn-Ji-n_rL ©—: ~L_ £-LJ 込|_J £LJ— 图解6-5.1 6.5.2试用两片74HC194构成8位双向移位寄存器。 解: 用两片74HC194组成8位双向移位寄存器时,只需将低位芯片的Q接至高位芯片的右移串行输入端Dsr,而将高位芯片的Q。 接到低位芯片的左移串行输入端Dsl,同时把两芯 片的S、So、CPCR分别连接在一起作为相应信号输入端。 其电路如图题解 ABCD 74HCW1)' CR 6.5.3 6.5.2所示。 在某计数器的输出端观察到如图题6.5.3所示的波形,试确定该计数器的模。 「p_rLTLrLnj"LrLrLrLrL J-L 解: 由图题6.5.3所示的波形可知,该计数器计数过程中,在连续出现010、000、001、100、 011、101六个不同的状态后,又按原来顺序变换了四个状态,故计数器的模可能为6。 6.5.4试用下降沿触发的JK触发器组成4位异步二进制减计数器,画出逻辑图。 解: n位二进制异步计数器需要用n个处于工作状态的触发器组成,因此4位异 步二进制减计数器需要用4个触发器组成。 当用JK触发器组成时,首先应将各JK触发器接 成计数工作状态,即将各触发器的J、K端均接至高电平。 然后决定级间连接方式,即按照 二进制减计数规则: 当低位触发器的Q端已经为0时,再输入一个计数脉冲,Q端应翻转为 1,同时向高1位发出借位信号,使高1位触发器翻转。 因为是用下降沿触发的触发器,所以要将低位触发器的Q端接至高1位触发器的时钟输入端。 这样,当低位的Q端由0变为1 时,它的Q端由1变为0,正好作为高1位触发器的时钟信号。 按照上述步骤用下降沿触发 的JK触发器组成的4位异步二进制减计数器电路如图题解6.5.4所示。 6.5.5试用下降沿触发的D触发器组成4位异步二进制加计数器,画出逻辑图。 I 金◎aa SM&.5.5 解: 首先将4个触发器接成计数工作状态,即将各触发器的D端与其Q端相连接。 然后决 定级间连接方式,即按照二进制加计数规则: 当低位触发器的Q端已经为1时,再输入一个计数脉冲后Q端应翻转为0,同时向高1位触发器发出进位信号,使高1位翻转。 因为是用 下降沿触发的触发器,所以只要将低位触发器的Q端接至高1位触发器的时钟输入端,当低位的Q端由1变为0时,正好作为高1位触发器的时钟信号。 按照上述步骤用下降沿触发的D触发器组成的4位异步二进制加计数器电路如图题解6.5.5所示。 6.5.6试用上升沿触发的D触发器及门电路组成3位同步二进制加计数器,画出逻辑图。 解: 3位二进制计数器需要用3个触发器。 因是同步计数器,故各触发器的CP端接同一时 钟脉冲源。 (1)列出该计数器的状态表和激励表,如表题解5.5.6所示。 1 ■ - ft毒叭信号] 1硏 閉 * 4 D • ! * S 1 ■ a D 萌 L t 2 < 5 0 A 1 1 a 0 L 1 1 0 n V 1 D 0 1 G 1 5 1 挣 1 1 1 Q 6 1 1 D 1 1 1 R- f. 1 1 1 4 0 n (2) 用卡诺图化简,如图题解5.5.6(a)所示,求激励方程组。 (a) MH (3)画出该计数器的逻辑电路图,如图题解5.5.6(b)所示。 6.5.9试用上升沿触发的D触发器和门电路设计一个同步三进制计数器。 解: 这是非二进制同步计数器的设计。 三进制计数器需要2个触发器。 (1)列出状态表和激励表,如表题解6.5.9所示。 ep的験年 ◎ 现杰 QS 氏矗驱动信号 百 0 0 1 1 1 1 1 E*1 4 2 t 0 0 多余扰蕊H自动功能 0 1 X X (2)画出卡诺图,如图题解6.5.9(a)所示,化简后,得到状态方程组(即激励方程组) n QinD^QiQ0 Q01=D°二Q: (3)画出该计数器的逻辑电路图,如图题解6.5.9(b)所示。 QI0 (4)检查自启动能力。 将电路的无效状态Q=0、Q=1代入状态方程组,其次态为Q=Q=1,即电路能自动进入有效 状态11,因此,所设计的计数器能够自启动。 6.5.11试分析图题6.5.11所示电路,画出它的状态图,说明它是几进制计数器。 解: 图题6.5.11所示电路由74HCT161用“反馈清零法”构成的计数器。 设电路 使74HCT161的异步清零输入端CR由1变为0,使整个计数器回到0000状态,完成一个计数周期。 此后CR恢复为1,计数器又进入正常计数状态。 其中,1010仅在极短的时间内出 现,电路的基本状态只有0000〜1001十个状态,状态图如图题解6.5.11所示。 该电路经10个时钟脉冲完成一次循环,因此,模为M=1Q是十进制计数器。 6.5.13试分析图题6.5.13所示电路,画出它的状态图,说明它是几进制计数器。 厂丄I】丨I工CET«几°g CFP74HCT161 \r'pPL ‘ uQ,Q2Q. 「IT MW札拆13 解: 图题6.5.13所示电路是由74HCT161用“反馈清零法”构成的计数器。 设电路初态为 0000,在第10个计数脉冲作用后,Q3Q2QQ0=1010,使并行置数使能端由1变成0而有效,由于74HCT161是同步预置计数器,因此只有在第11个计数脉冲作用后,数据输入端 D3D2D1D0=0000的状态才被置入计数器,使Q3Q2QQo=0000。 电路的状态图与图解6.5.12 相同,它是一个十一进制计数器。 6.5.14 试分析图题6.5.14所示电路,画出它的状态图,说明它是几进制计数器。 解: 图题6.5.14所示电路74HCT161用“反馈清零法”构成的计数器。 设电路的初态为并行 置入的数据

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 时序 逻辑电路

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx