数字电路与逻辑设计课程设计.docx

数字电路与逻辑设计课程设计.docx

- 文档编号:5994590

- 上传时间:2023-01-02

- 格式:DOCX

- 页数:8

- 大小:662.29KB

数字电路与逻辑设计课程设计.docx

《数字电路与逻辑设计课程设计.docx》由会员分享,可在线阅读,更多相关《数字电路与逻辑设计课程设计.docx(8页珍藏版)》请在冰豆网上搜索。

数字电路与逻辑设计课程设计

数字电路与逻辑设计课程设计

一、课题:

脉宽调制电路设计制作

二、设计元器件:

ADC0809、74LS04、可调电位器各一片,74LS169二片,74HC85四片,发光二极管十只

三、1、设计要求:

用模拟信号控制脉宽调制信号的脉冲宽度,宽度由ADC0809转换为8位二进制信号,该信号与2片74LS169组成的M=256计数器的8位输出比较,从输出端产生可以调整脉宽的输出方波信号,为降低难度,方波的周期由输入开关设置。

2、提高要求:

将上述电路设计成周期可调,可能需要外加电路,视内容而定。

四、设计原来框图及设计说明

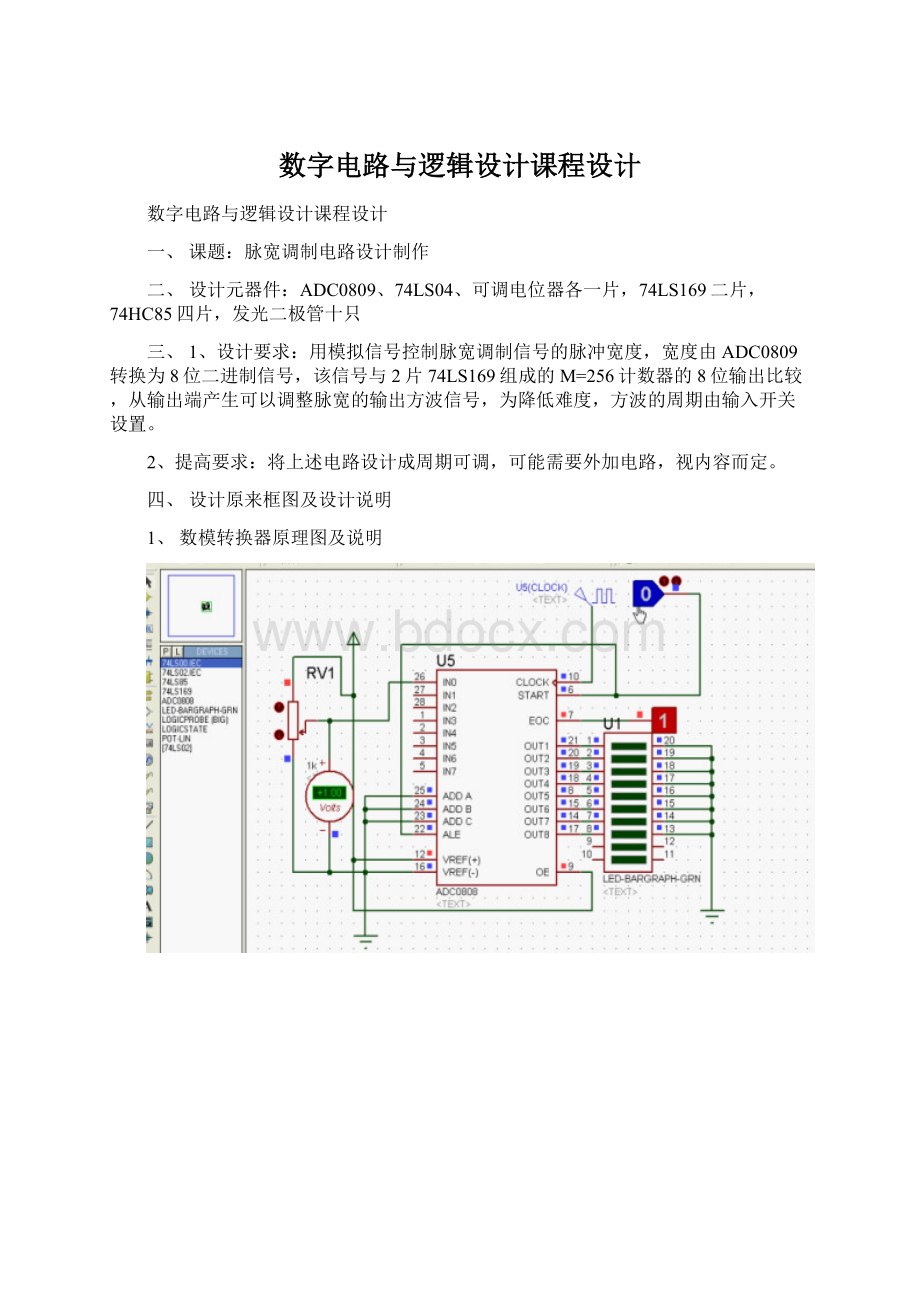

1、数模转换器原理图及说明

工作原理:

ADC0809是CMOS单片型逐次逼近式A/D转换器,它由8路模拟开关、地址锁存与译码器、比较器、8位开关树型D/A转换器、逐次逼近寄存器、三态输出锁存器等其它一些电路组成。

因此,ADC0809可处理8路模拟量输入,且有三态输出能力,既可与各种微处理器相连,也可单独工作。

输入输出与TTL兼容。

ADC0809A/D转换芯片引脚功能

ADC0809芯片有28条引脚,采用双列直插式封装:

IN0~IN7:

8路模拟量输入端。

d-1~d-8:

8位数字量输出端。

ADDA、ADDB、ADDC:

3位地址输入线,用于选通8路模拟输入中的一路.

ALE:

地址锁存允许信号,输入,高电平有效。

START:

A/D转换启动信号,输入,高电平有效。

EOC:

A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低电平)。

OE:

数据输出允许信号,输入,高电平有效。

当A/D转换结束时,此端输入一个高电平,才能打开输出三态门,输出数字量。

CLK:

时钟脉冲输入端。

要求时钟频率不高于640KHZ。

REF(+)、REF(-):

基准电压。

Vcc:

电源,单一+5V。

GND:

地。

2、其他芯片工作原理

3、脉宽调制原理图及说明

五、Proteus仿真电路

六、芯片及线路连接

说明:

1.根据仿真电路图对面包板进行布局,最上面为ADC0809,实现数模转换,第二排为两个74HC85及74LS02,第三排为两个74LS169,最后一排为两个74HC85,且所有芯片共电源、共地。

根据电路图,连接电位器并用导线将各个芯片连接。

2.在连接好数模转换器之后,连接电位器,并用万用表测量电位器电压变化是否正常。

检测无误后在八个输出端分别接8个LED灯,当ADC工作时,start结束完整脉冲后,开始输出数字信号,改变电位器位置,输出端高低变化,8盏灯亮暗也随之变化。

此时,证明数模转换器正常工作。

3.分别连接计数器及比较器。

七、总电路连接调试

在总电路连接完成之后,通电并连接数字示波器对电路进行验证。

经多次调试与修改之后,最终结果为:

当电位器处于中间约2.5V时,输出方波占空比为1,即方波高低电平宽度基本相同。

当调节电位器增大电压到最大时,波形低电平宽度逐渐减小直到近似为全为高电平;当电压逐渐减小到最小值时,波形高电平宽度逐渐减小直到近乎只有高电平。

波形变化如图所示:

八、设计中遇到问题解决及经验教训

问题:

将电路板接通电源,连接示波器,出现稳定的方波,但调节电位器改变电压时,并没有实现脉宽可调。

解决方法:

1、用万用表检测电位器电压变化正常,电位器正常工作。

2、将ADC0809八个输出端分别接8个LED灯,改变电位器位置,8盏灯一直处于高电平并没有随之亮暗变化。

且用逻辑笔检测ADC0809的EOC脚时一直处于高电平,并不能发生跳变,说明数模转换器不能正常工作。

故开始检查74LS169的工作情况,发现其中一个74LS169的一个输出端处于低电平,不能正常输出,经检测发现该芯片的16脚没有接电源,导致其不能正常输出信号反馈给ADC0809。

将16脚接上电源,整个电路正常工作。

参考文献:

《08级通信专业数电课程设计》方怡冰

《数字逻辑设计与VHDL描述》第二版

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电路 逻辑设计 课程设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx