数字逻辑实验报告四.docx

数字逻辑实验报告四.docx

- 文档编号:5937482

- 上传时间:2023-01-02

- 格式:DOCX

- 页数:12

- 大小:68.58KB

数字逻辑实验报告四.docx

《数字逻辑实验报告四.docx》由会员分享,可在线阅读,更多相关《数字逻辑实验报告四.docx(12页珍藏版)》请在冰豆网上搜索。

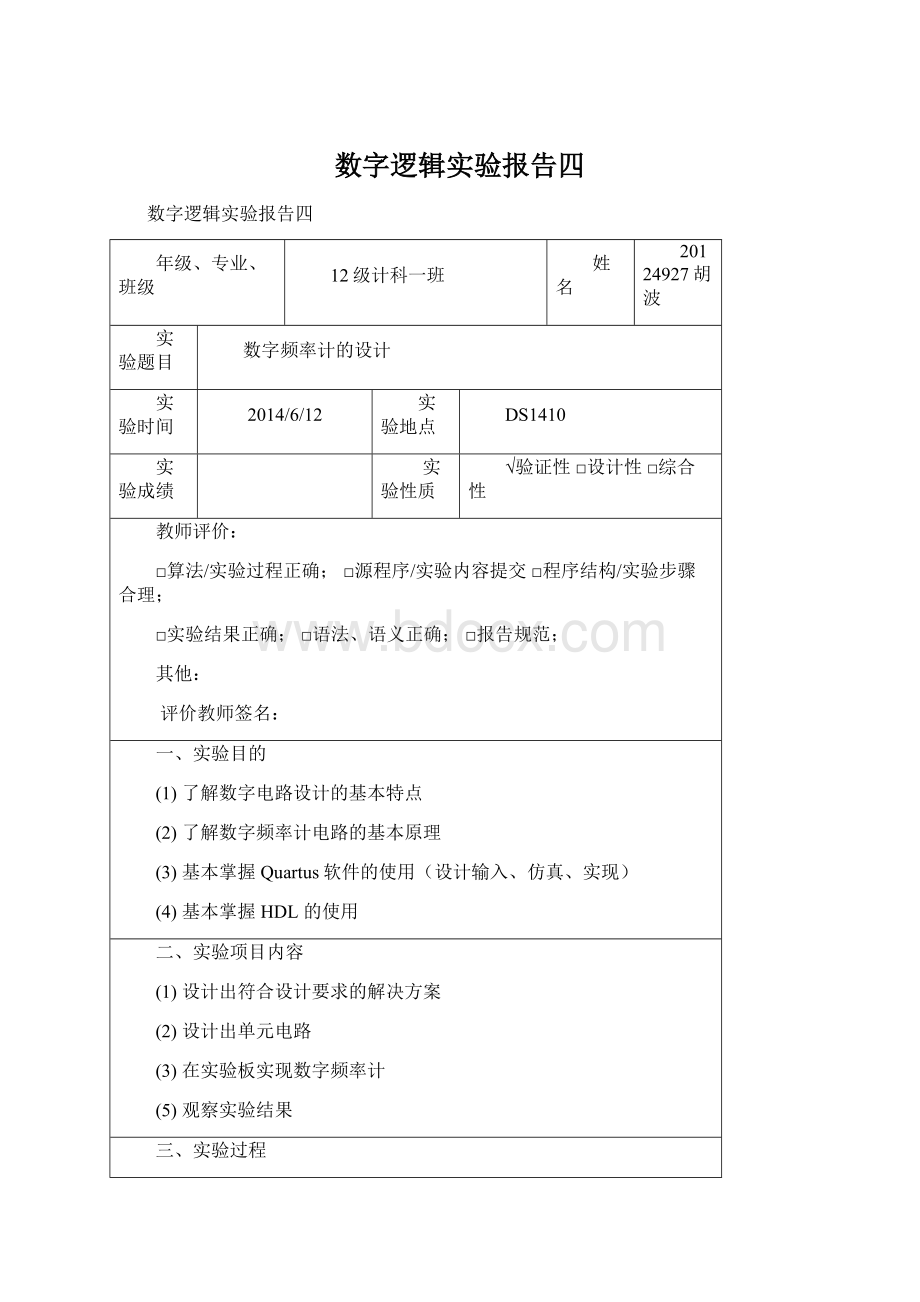

数字逻辑实验报告四

数字逻辑实验报告四

年级、专业、班级

12级计科一班

姓名

20124927胡波

实验题目

数字频率计的设计

实验时间

2014/6/12

实验地点

DS1410

实验成绩

实验性质

√验证性□设计性□综合性

教师评价:

□算法/实验过程正确;□源程序/实验内容提交□程序结构/实验步骤合理;

□实验结果正确;□语法、语义正确;□报告规范;

其他:

评价教师签名:

一、实验目的

(1)了解数字电路设计的基本特点

(2)了解数字频率计电路的基本原理

(3)基本掌握Quartus软件的使用(设计输入、仿真、实现)

(4)基本掌握HDL的使用

二、实验项目内容

(1)设计出符合设计要求的解决方案

(2)设计出单元电路

(3)在实验板实现数字频率计

(5)观察实验结果

三、实验过程

设计流程

使用软件进行可编程逻辑器件开发主要包括4个阶段:

设计输入、编译处理、验证(包括功能仿真、时序仿真、和定时分析)和器件编程,流程如图2.1所示:

根据系统设计要求,系统设计采用自顶向下的设计方法,系统的组成框图如图3.1所示,包括时基产生与测频时序控制电路模块,以及待测信号脉冲计数电路模块和锁存与译码显示控制电路模块。

(1)时基产生与测频时序控制电路模块

时基产生与测频时序控制电路的主要产生计数允许信号EN、清零信号CLR和锁存信号LOCK。

(2)待测信号脉冲计数电路模块

待测信号脉冲计数电路是对待测脉冲信号的频率进行测量,它可由4个十进制加法计数器组成,其中EN为计数选通控制信号,CLR为计数器清零信号。

在计数器清零信号CLR清零后,当计数选通控制信号EN有效时,开始对待测信号进行计数。

如果计数选通控制信号EN的宽度为1s,那么计数结果就为待测信号的频率;如果计数选通信号EN的宽度为100ms,那么待测信号的频率等于计数结果

10。

(3)锁存与译码显示控制电路模块

锁存与译码显示控制电路用于实现记忆显示,在测量过程中不刷新新的数据,直到测量过程结束后,锁存显示测量结果,并且保存到下一次测量结束。

锁存与译码显示电路的功能是对四位BCD码进行锁存,并驱动数码管。

采用VHDL语言设计一个复杂的电路系统,运用自顶向下的设计思想,将系统按功能逐层分割的层次化设计方法进行设计。

在顶层对内部各功能块的连接关系和对外的接口关系进行了描述,而功能块的逻辑功能和具体实现形式则由下一层模块来描述。

各功能模块采用VHDL语言来描述。

四、实验结果及分析

结果测试

在成功下载并运行后,评估该设计系统的实际测量效果,作对比试验,选用频率可调的函数发生器生成测试信号。

测得结果如下:

序号

输入(Hz)

输出(Hz)

1

1

1

2

10

10

3

100

100

4

1000

1000

5

536

536

附VHDL源代码

顶层电路的VHDL源程序

顶层文件pinlvji:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYPINLVJIIS

PORT(F_IN,CLK:

INSTD_LOGIC;

ENT,LOCKT,CLRT:

BUFFERSTD_LOGIC;

Z1,Z2,Z3,Z4:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDPINLVJI;

ARCHITECTUREARTOFPINLVJIIS

SIGNALENS,LOCKS,CLRS:

STD_LOGIC;

SIGNALQAS,QBS,QCS,QDS:

STD_LOGIC_VECTOR(3DOWNTO0);

COMPONENTcontroler--元件CTRL引用说明语句

PORT(CLK:

INSTD_LOGIC;

EN,LOCK,CLR:

OUTSTD_LOGIC);

ENDCOMPONENT;

COMPONENTCOUNT--元件COUNT引用说明语句

PORT(CLK,EN,CLR:

INSTD_LOGIC;

QA,QB,QC,QD:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCOMPONENT;

COMPONENTLOCK--元件LOCK引用说明语句

PORT(LOCK:

INSTD_LOGIC;

QA,QB,QC,QD:

INSTD_LOGIC_VECTOR(3DOWNTO0);

DA,DB,DC,DD:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCOMPONENT;

BEGIN

ENT<=ENS;

LOCKT<=LOCKS;

CLRT<=CLRS;

U1:

controlerPORTMAP(CLK,ENS,LOCKS,CLRS);--元件引用例示

U2:

COUNTPORTMAP(F_IN,ENS,CLRS,QAS,QBS,QCS,QDS);--元件引用例示

U3:

LOCKPORTMAP(LOCKS,QAS,QBS,QCS,QDS,Z1,Z2,Z3,Z4);--元件引用例示

ENDART;

锁存与译码显示控制模块的VHDL源程序

Lock文件:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYLOCKIS

PORT(LOCK:

INSTD_LOGIC;

QA,QB,QC,QD:

INSTD_LOGIC_VECTOR(3DOWNTO0);

DA,DB,DC,DD:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));--频率计数输出

END;

ARCHITECTUREARTOFLOCKIS

SIGNALQAL,QBL,QCL,QDL:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(LOCK)

BEGIN

IF(LOCK'EVENTANDLOCK='1')THEN--检测时钟上升沿

QAL<=QA;

QBL<=QB;

QCL<=QC;

QDL<=QD;

ENDIF;

ENDPROCESS;

DA<=QAL;

DB<=QBL;

DC<=QCL;

DD<=QDL;

ENDART;

待测信号脉冲计数器的VHDL源程序

Count文件:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCOUNTIS

PORT(CLK:

INSTD_LOGIC;--待测时钟信号

EN:

INSTD_LOGIC;--计数选通控制信号

CLR:

INSTD_LOGIC;--计数器清零信号

QA,QB,QC,QD:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));--结果输出信号

END;

ARCHITECTUREARTOFCOUNTIS

COMPONENTCB10--元件CB10引用说明语句

PORT(CLK,EN,CLR:

INSTD_LOGIC;

COUNT10:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));--计数输出信号

ENDCOMPONENT;

SIGNALCLK2:

STD_LOGIC;

SIGNALCLK3:

STD_LOGIC;

SIGNALCLK4:

STD_LOGIC;

BEGIN

CLK2<=NOTQA(3);

CLK3<=NOTQB(3);

CLK4<=NOTQC(3);

U1:

CB10PORTMAP(CLK,EN,CLR,QA);--元件引用例示

U2:

CB10PORTMAP(CLK2,EN,CLR,QB);--元件引用例示

U3:

CB10PORTMAP(CLK3,EN,CLR,QC);--元件引用例示

U4:

CB10PORTMAP(CLK4,EN,CLR,QD);--元件引用例示

ENDART;

十进制加法计数器的VHDL源程序

Cd10文件:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCB10IS

PORT(CLK,EN,CLR:

INSTD_LOGIC;

COUNT10:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));--计数输信号

ENDCB10;

ARCHITECTUREARTOFCB10IS--结构体

BEGIN

PROCESS(CLK,CLR,EN)

BEGIN

IFCLR='1'THEN

COUNT10<="0000";--计数器清零

ELSIFRISING_EDGE(CLK)THEN--检测时钟上升沿

IF(EN='1')THEN--检测是否允许计数

IFCOUNT10="1001"THEN

COUNT10<="0000";--计数值满9清零

ELSE

COUNT10<=COUNT10+'1';--允许计数

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

ENDART;

译码显示电路的VHDL源程序

Bcd7文件:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYBCD7IS

PORT(BCD:

INSTD_LOGIC_VECTOR(3DOWNTO0);--BCD输入信号

LED:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));--七段译码输出信号

END;

ARCHITECTUREARTOFBCD7IS

BEGIN

LED<="0111111"WHENBCD="0000"ELSE--对照七段字形显示译码器真值表

"0000110"WHENBCD="0001"ELSE

"1011011"WHENBCD="0010"ELSE

"1001111"WHENBCD="0011"ELSE

"1100110"WHENBCD="0100"ELSE

"1101101"WHENBCD="0101"ELSE

"1111101"WHENBCD="0110"ELSE

"0000111"WHENBCD="0111"ELSE

"1111111"WHENBCD="1000"ELSE

"1101111"WHENBCD="1001"ELSE

"0000000";

ENDART;

时基产生与测频时序控制电路模块的VHDL源程序

Controler文件:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitycontroleris

port(CLK:

instd_logic;

EN:

outstd_logic;

CLR:

outstd_logic;

LOCK:

outstd_logic

);

endcontroler;

architectureBehavioralofcontroleris

signalQ:

std_logic_vector(3downto0);

begin

process(CLK)

begin

ifCLK'eventandCLK='1'then

ifQ=x"1111"then

Q<=(others=>'0');

else

Q<=Q+1;

endif;

endif;

endprocess;

process(Q)

begin

caseQis

when"0000"=>CLR<='0';EN<='0';LOCK<='0';

when"0001"=>CLR<='1';EN<='0';LOCK<='0';

when"0010"=>CLR<='0';EN<='0';LOCK<='0';

when"0011"=>CLR<='0';EN<='1';LOCK<='0';

when"0100"=>CLR<='0';EN<='1';LOCK<='0';

when"0101"=>CLR<='0';EN<='1';LOCK<='0';

when"0110"=>CLR<='0';EN<='1';LOCK<='0';

when"0111"=>CLR<='0';EN<='1';LOCK<='0';

when"1000"=>CLR<='0';EN<='1';LOCK<='0';

when"1001"=>CLR<='0';EN<='1';LOCK<='0';

when"1010"=>CLR<='0';EN<='1';LOCK<='0';

when"1011"=>CLR<='0';EN<='1';LOCK<='0';

when"1100"=>CLR<='0';EN<='1';LOCK<='0';

when"1101"=>CLR<='0';EN<='0';LOCK<='0';

when"1110"=>CLR<='0';EN<='0';LOCK<='1';

when"1111"=>CLR<='0';EN<='0';LOCK<='0';

whenothers=>CLR<='0';EN<='0';LOCK<='0';

endcase;

endprocess;

endBehavioral;

部分程序仿真:

待测信号脉冲计数器的仿真

十进制加法计数器的仿真

感想:

本设计利用测频法的原理和VHDL语言,采用自顶向下的设计方法,实现了1Hz~10kHz测量范围的四位十进制的数字频率计,并在软件帮助下对设计项目进行的了编译和时序仿真。

实验结果表明,该系统能够满足本次设计的要求,并且具有测量误差小,可靠性高的优点。

课程设计结束了,这次设计历时近一个星期,通过这一个星期的学习,发现了自己的很多不足,发现了很多知识上的漏洞。

同时也看到了自己的实践经验还是比较缺乏,理论联系实际的能力还急需提高。

这次课程设计让我学到了很多,不仅是巩固了先前学的理论知识,而且也培养了我的动手能力,更令我的创造性思维得到拓展。

在这个过程中,我也曾经因为实践经验的缺乏失落过,也曾经仿真成功而热情高涨。

还有一点是我们做任何事情都无法缺少的,那就是细心认真。

此次设计我就深深地体会到了,由于编程的时候没有做到足够的细心,导致一串代码弄混了。

但是密密麻麻的英文字母混在一起,我始终没有发现。

最终在调试的时候,就出现了问题。

只知道出现了问题,就是不知道到问题的根源在哪里,好长时间都没有找出问题的所在。

这也让我真正的明白了,科学的严谨性,它不允许出半点差错,否则后果会是比较麻烦的。

做其他事情也一样,都需要我们付出足够的认真去对待,才能顺利的完成。

对我而言,知识上的收获重要,精神上的丰收更加可喜。

让我知道了学无止境的道理。

我们每一个人永远不能满足于现有的成就,人生就像在爬山,一座山峰的后面还有更高的山峰在等着你。

挫折是一份财富,经历是一份拥有。

这次课程设计必将成为我人生旅途上一个非常美好的回忆!

3、学生应按照要求正确地撰写实验报告:

1)在实验报告上正确地填写“实验时间”、“实验地点”等栏目。

2)将实验所涉及的源程序文件内容(实验操作步骤或者算法)填写在“实验过程或算法(源程序)”栏目中。

3)将实验所涉及源程序调试过程(输入数据和输出结果)或者实验的分析内容填写在“实验结果及分析和(或)源程序调试过程”栏目中。

4)在实验报告页脚的“报告创建时间:

”处插入完成实验报告时的日期和时间。

5)学生将每个实验完成后,按实验要求的文件名通过网络提交(上载)到指定的服务器所规定的共享文件夹中。

每个实验一个电子文档,如果实验中有多个电子文档(如源程序或图形等),则用WinRAR压缩成一个压缩包文档提交,压缩包文件名同实验报告文件名(见下条)。

6)提交的实验报告电子文档命名为:

“年级(两位数字不要“级”字)专业(缩写:

计算机科学与技术专业(计科)、网络工程专业(网络)、信息安全专业(信息)、物联网工程(物联网))班级(两位数字)学号(八位数字)姓名实验序号(一位数字).doc。

如学号为20115676、年级为2011级、专业为“计算机科学与技术”专业、班级为“02班”、姓名为“王宇”的学生,完成的第一次实验命名为:

11计科02班20115676王宇1.Doc,以后几次实验的报告名称以此类推。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 逻辑 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx