如何使用QuartusII70.docx

如何使用QuartusII70.docx

- 文档编号:5824460

- 上传时间:2023-01-01

- 格式:DOCX

- 页数:33

- 大小:1,000.78KB

如何使用QuartusII70.docx

《如何使用QuartusII70.docx》由会员分享,可在线阅读,更多相关《如何使用QuartusII70.docx(33页珍藏版)》请在冰豆网上搜索。

如何使用QuartusII70

EDA实验技术文档

含异步清0和同步时钟使能的4位加法计数器

一、实验内容与实验原理

利用QuartusII建立一个含计数使能、异步复位的4位加法计数器,并进行仿真测试和硬件测试。

由实验开发板上数字信号源Clock0提供一个输入为4Hz的时钟输入信号clk,由开发板上拨挡开关SW1控制计数使能端ena并由LED1指示,由核心板上SYS_RST按键控制复位端rst并由LED2指示,进位输出由LED3指示,计数值由数码管显示。

二、实验步骤

1、使用QuartusII建立空白工程,然后命名为cnt_4b.qbf

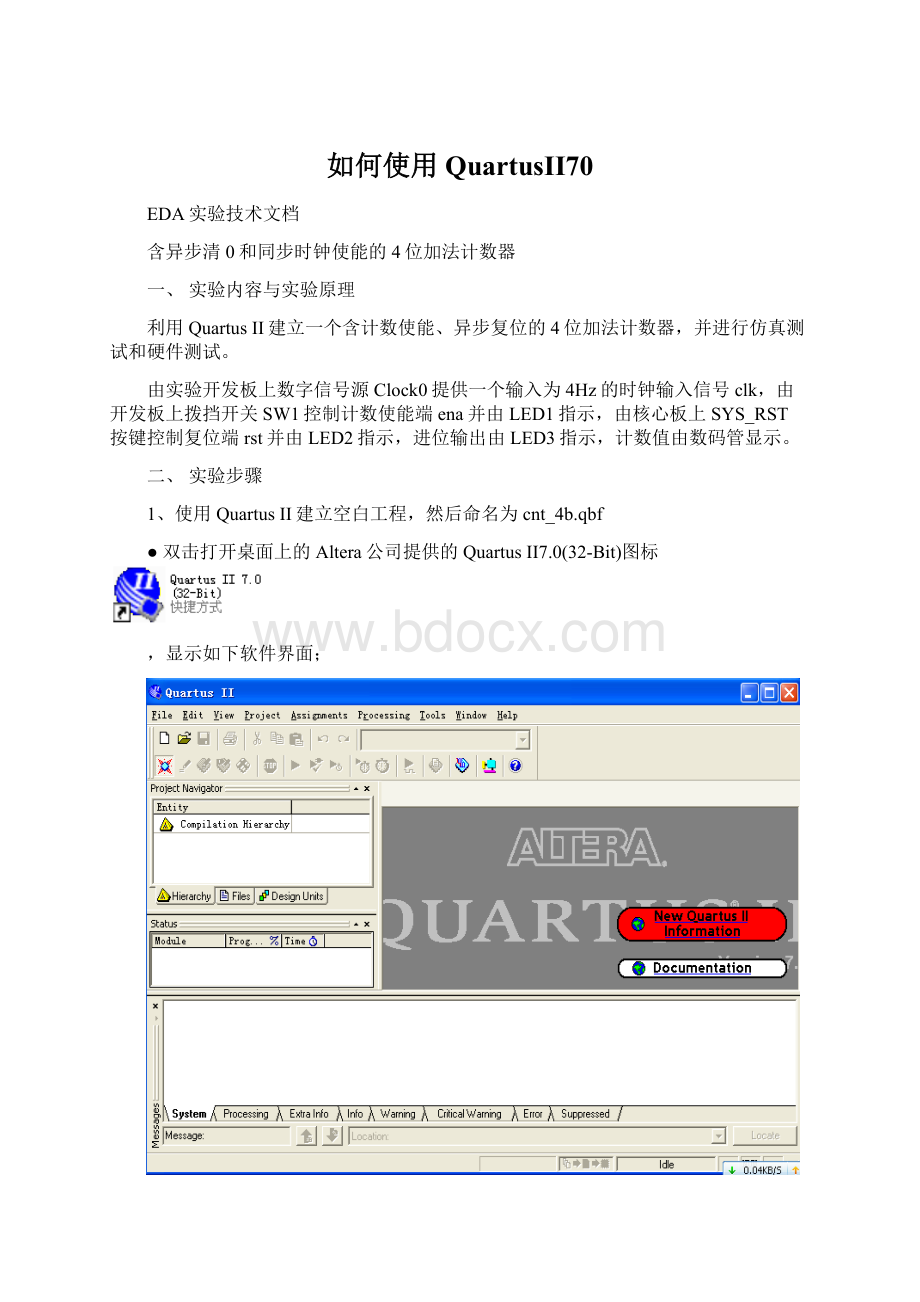

●双击打开桌面上的Altera公司提供的QuartusII7.0(32-Bit)图标

,显示如下软件界面;

●选择菜单栏中File>>NewProjectWizard来新建工程,点击后弹出新建工程向导对话框如下

分别提示完成五项工作1)项目名称与保存路径2)顶层设计实体名称3)加入已有文件和相关库4)指定目标Altera器件封装和型号5)设置项目的其他EDA工具

●单击Next进入如下图所示界面,并按图新建工程路径、名称、顶层实体

在这里,工程名与顶层文件的实体名同名为cnt_4,文件夹所在路径名和文件夹名中不能用中文,不能用空格,不能用括号(),可以用下划线_或英文字母或数字,但最好也不要以数字开头。

●单击Next进入如下图所示界面,这里是添加已有相关工程文件,这里我们是建立空白工程,所以不需要添加任何文件

●单击Next进入如下图所示界面,这一步是对所用实验核心板中FPGA器件进行设置,以确保代码顺利编译和下载。

MagicSOPC实验箱上的FPGA标配为:

Altera公司CycloneII系列的EP2C35F672。

设置相关参数如图所示。

●设置完成后,单击Next,进入如下图所示界面,这里不需要设置其他EDA工具

●再单击Next,出现如下图所示的工程信息报告对话框,提示设计者看到工程文件配置信息报告。

最后,单击Finish,完成新建工程的建立。

2、建立文本编程文件

1)新建VerilogHDL源程序文件cnt4b.v,输入程序代码并保存,(完整的程序参考清单见附录),进行综合编译。

●在第1步,已经创建好的设计工程后,在菜单栏中File>>New打开新建文本对话框如下图所示,在新建对话框中选择VerilogHDLFile,按OK就可建立一个空的VerilogHDL文件,缺省名为Verilog1.v。

●再选择菜单命令中File>>SaveAs改名为cnt4b.v,点击保存!

这里切莫将文件名默认为cnt_4b,根据笔者的经验这将造成后续建立的相对应的模块符号无法正常添加到顶层实体的图形设计文件中去。

●在cnt4b.v空白VerilogHDL程序文件中输入设计计数程序模块,输入无误后点击

图标加以保存。

详细程序文件和说明见附录1!

这里要注意保证程序的模块名应和文件名一致!

●对上述的VerilogHDL文件进行编译处理,具体操作如下:

a.如图所示,在工程向导栏窗口中的File标签中的Led.v文件单击鼠标右键,在弹出的菜单中单击SetatTop-level-Entity选项。

将cnt4b.v文件设置为顶层实体。

这一步很重要,不设置无法进行b步骤的编译与综合

b.选择菜单栏中Processing>>Start>>StartAnalysis&Synthesis进行综合编译,也可以选择工具栏上的

按钮启动编译

c.若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

若编译成功会出现如下图形:

2)再新建VerilogHDL源程序文件decl7s.v,输入程序代码并保存,(完整的程序参考清单见附录),进行综合编译。

●相应新建保存以及综合编译的步骤请参照1)新建cnt4b.v

a.新建文件名decl7s.v的空白VerilogHDL文件

b.在decl7s.v空白VerilogHDL程序文件中输入显示计数程序模块,输入无误后点击

图标加以保存。

详细程序文件和说明见附录2!

c.对decl7s.v文件进行VerilogHDL文件进行编译处理,这里同样别忘了将文件设置为顶层实体文件

至此,我们已经建立了实验所需要的加法计数模块和数码管静态显示模块!

下面我们要做到就是将文本模块程序进行“封装”!

3、从设计文件创建模块

●如下图所示,在工程向导里面的Files标签中的cnt4b.v文件单击鼠标右键,在弹出的菜单中单击CreateSymbolFilesforCurrentFile选项。

之后会弹出一对话框提示原理图文件创建成功,点“确定”按钮即可创建一个代表现行一个代表现行文件功能的符号文件(cnt4b.bsf)。

●同理,用同样的操作步骤,可以轻松的创建对decl7s.v代表的decl7s.bsf符号文件

4、波形仿真验证

这里我们将详细介绍在第3部分建立的cnt4b.v计数模块加以波形仿真验证(前仿真)

●选择在工程向导里面的Files标签中的cnt4b.v文件,将其设回顶层实体文件,然后在进行一次综合编译(笔者认为,是为了能在后续的NodeFinder对话框找到所需的引脚,而不是其他模块的引脚,这一点请格外注意!

)

●选择菜单栏中File>>New命令,打开新建文件对话框,如下图所示:

选择OtherFiles标签页从中选择VectorWaveformFile(矢量波形文件),按OK建立空的波形编辑窗口,缺省值为Waveform1.vwf.选择File>>SaveAs改名为cnt_4b.vwf并保存。

●在如下图所示的Name标签区域内双击鼠标左键,弹出添加节点对话框

●在上图中InsertNodeorBus对话框中单击NodeFinder按钮,弹出如下对话框,这里要进行三步设置

1)

Filter>>Pins:

all按List按钮

2)按>>添加所有节点

3)按OK按钮,这样就会弹出一个未经设置过的波形图

●选择Edit>>EndTime命令,弹出结束时间对话框,在Time框中输入仿真结束时间,这里我们采用默认设置(1us)

●编辑输入节点波形。

笔者认为这一步是体现实验者对实验对象计数模块理解的情况下,根据自己仿真意图,去建立输入节点的波形,然后通过功能仿真观察输出波形,比对结果。

如何建立输入节点波形?

在这里需要使用到上图最左侧的波形编辑器工具条,具体各个标签请详细参照EDA实验与实践教程

(二)P84

clk输入:

1)点击Name栏中的clk输入,这样会是其高亮度显示

2)点击波形编辑器工具条中

(时钟),弹出如右图的时钟设置窗口,这里笔者采用默认值

3)点击OK

ena输入和rst输入

分别点击Name栏中的相应输入,在波形图中,使用

工具(或者其他功能工具标签)在合适位置进行灵活设置,具体图形请参照上图。

●选择Processing>>SimulatorTool命令,弹出如下窗口,按下图进行选择设置

具体步骤如下

1)选择

2)选择仿真文件

3)点击

,若产生功能仿真网表成功,提示如下信息

4)选择上

5)按

开始仿真,若通过,提示下图信息:

6)

按此按钮打开仿真后的波形文件,仿真后得到的波形文件如下图所示:

●验证仿真结果是否与设计相符合,如果不符合,需要重新设计文件,再进行综合编译、仿真。

指导仿真结果与设计相符合为止

5、建立顶层实体文件------图形设计文件

●如图所示,选择菜单栏中File>>New打开新建对话框,在新建对话框中选择BlockDiagram/SchematicFile,按OK就可建立一个空的图形设计文件,缺省名为Block1.bdf。

●如图所示,选择菜单栏中File>>SaveAs打开将BDF文件存盘的对话框,

在这里,一定要接受默认的文件名(与顶层实体名一定要相同),并默认Addfiletocurrentprojext选项选中,以使该文件添加到工程中去。

至此,完成了顶层模块的建立,下面将VerilogHDL文件生成的模块符号文件加入到顶层模块中去!

6.建立4位加法计数器顶层模块原理图

●添加cnt4b.bsf模块到QuartusII顶层模块

b.在工程向导栏窗口中的File标签中的cnt_4b.bdf文件单击鼠标右键,在弹出的菜单中单击SetatTop-level-Entity选项。

将cnt_4b.bdf文件设置为顶层实体。

c.在cnt_4b.bdf右侧空白窗口中,任意处双击,弹出添加符号(symbol)的对话框,如下图所示:

c.单击OK,Symbol对话框被关闭,cnt_4bf符号被附在鼠标的指针上,在cnt_4b.bdf的窗口中的适当位置,放下该符号

d.选择File>>Save来保存QuartusII顶层文件cnt_4b.bdf

●添加decl7s.bsf模块到QuartusII顶层模块

添加方法请参照cnt4b.bsf模块添加方法b,c,d步骤,所不同的就是选择的模块是decl7s.bsf,放在合适的位置上。

●添加引脚和其他基本单元,组成完整的顶层模块图

如上图所示,在空白设计栏最左侧竖向排列着若干图标,即所谓的模块编辑工具栏,具体内容详见EDA实验与实践教程

(二)P58

我们这里就是使用若干模块编辑工具栏中按钮,完成顶层模块设计!

具体操作步骤如下:

a.单击模块编辑工具栏中

按钮,插入符号对话框如下图所示,这里默认选择了Repeat-insertmode,如此便可以重复插入相同功能的引脚。

b.在Name栏目中直接输入input,单击OK按钮

c.连续插入三个输入引脚,由于只需要三个输入引脚,故浮动出现第四个引脚右键单击出现选择菜单,点击Cancel即可取消,如下图所示

d.同样的方法可以添加5个输出引脚(Name栏目中输入output)、2个非门(Name栏目中输入not)、1个数字地(Name栏目中输入gnd)。

拖动引脚符号,按下图进行相应正确放置

d.在正确放置后,需要用到模块编辑工具栏中

按钮(画线)和

按钮(画总线),需要正确使用两种工具,切莫搞混乱用,否则在编译的时候会报错,尤其是需要注意在数码管位码dig[7..0]由于是8位输出引脚线,所以需要用总线连接而不能用单线!

e.双击各个引脚符号,进行相应引脚命名

f.选择菜单栏中File>>Save保存BDF文件

g.单击快捷菜单栏中

(或者按CTRL+L),开始编译!

这一步的目的笔者认为主要基于两点1)检查上述设计的cnt_4b.bdf文件2)方便后续分配FPGA引脚时会自动出现所需信号名,而不需要自己输入

7.选择目标器件并对相应的引脚进行锁定

●在这里选择的器件为Altera公司CycloneII系列的EP2C35F672C8芯片,具体操作在

单击菜单栏中Assignments>>Device,如下图所示。

进行如下操作:

1)Family>>CycloneII

2)Package>>FBGA

3)Pincount>>672

4)Speedgrade>>8

5)Availabledevice>>EP2C35F672C8项

注意:

这里其实已经在一开始建立空白工程的时候完成,所以只需要进行再次的确认和修改

●在上图点击Device&PinOptions,打开Device&PinOptions对话框。

在对话框中选择Configuration标签页按下图进行设置,即采用串行配置器件EPCS16的主动配置方式。

●在对话框中选择UnusedPins标签页按下图进行没有使用引脚的设置,按照下图设置将未使用引脚设置为高阻输入,这样上电后FPGA的所有不使用引脚后进入高阻抗状态。

笔者认为:

这一步是相当关键,它可以避免多外设连接时造成的总线冲突,不至于造成读数据错误,甚至更严重的长时间的器件过热而烧毁,所以一定要将未定义的管脚设置为ASinputtri-stated(三态输入)方式

●点击确认和OK即可退出选择器件设置完成

●本实验中各引脚的命名以及与目标FPGA器件引脚号的关系如下表,我们就根据自己核心板选择相应的引脚进行分配。

MagicSOPC部分引脚索引表

信号

引脚

信号

引脚

信号

引脚

SEG[0]

J8

DIG[0]

L6

LED1

R5

SEG[1]

M3

DIG[1]

K5

LED2

P9

SEG[2]

K6

DIG[2]

G3

LED3

P7

SEG[3]

J6

DIG[3]

G4

clock0

N2

SEG[4]

U10

DIG[4]

J3

sys_rst

AC13

SEG[5]

N9

DIG[5]

K4

ena

L25

SEG[6]

L10

DIG[6]

L3

SEG[7]

L9

DIG[7]

M4

注意:

ena信号是拨挡开关的输入,I/OBank工作电压是2.5V,所以在I/O电平也应设置为2.5。

单击菜单栏中Assignments>>Pin,如下图所示。

进行如下操作:

●根据MagicSOPC部分引脚索引表在Location栏中输入对应管脚号

●核对完成后在菜单栏中File>>close,便可以退回到主界面cnt_4b.bdf顶层文件中

至此我们已经完成了在QuartusII上的软件设计和相关设置,下一步就是全局编译了!

8.全程编译和下载程序

●点击工具栏中

,对整个工程文件进行全程编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

在编译系统过程中,状态窗口显示整个编译进行及每个编译阶段所用的时间。

在编译结果显示在CompilationReport窗口中。

在编译工程中可能产生很多警告信息,但这个不会影响设计结果!

比如在本实验中,笔者在自己的电脑上运行该编译过程39秒,产生了13个警告信息。

这些信息可以根据软件手册和提示得到一定的解决!

对话框提示”Info:

QuartusIIFullCompilationwassuccessful.0errors,13warnings”

●点击确定即可!

如上图所示

●查看编译报告

●在下载程序之前,请在实验箱上确保数字信号源(在核心板临边右侧)的JP11的短路帽是处于ON位置,JP7中CLOCK0的短路帽处于4hz位置。

这里还要特别提示CLOCK0~CLOCK3对应的排针左边由不同频率的数字信号,排针右边是连到一起的,所以每组信号源只能插一个短路帽,否则可能会损害芯片!

●下载硬件设计到目标FPGA

方式一成功编译硬件系统后,将产生cnt_4b.sof的FPGA配置文件输出。

本步骤简单介绍利用JTAG方式下载到目标FPGA器件的步骤。

a.通过Z-Blaster下载电缆连接实验箱JTAG口和主计算机,接通实验箱电源

b.在QuartusII软件中选择Tools>>Programmer,或者点击工具栏

按钮。

打开编程器窗口并自动打开配置文件(cnt_4b.sof),如下图所示。

c.确保编程器窗口左上角的HardwareSetup栏中硬件已经安装

d.选择JTAG模式

e.确保Program/Configure下的方框选中

f.单击

开始使用配置文件对FPGA进行配置,Progress栏显示配置进度。

方式二成功编译硬件系统后,将产生cnt_4b.pof的FPGA配置文件输出。

本步骤简单介绍利用AS方式下载到目标FPGA器件的步骤。

a.通过Z-Blaster下载电缆连接实验箱AS口和主计算机,接通实验箱电源

b.在QuartusII软件中选择Tools>>Programmer,或者点击工具栏

按钮。

c.确保编程器窗口左上角的HardwareSetup栏中硬件已经安装

d.选择AS模式,由于笔者之前默认的JTAG方式下载,所以需要手动添加cnt_4b.pof文件

点击

弹出

对话框选择cnt_4b.pof文件后点击打开,这样就将需要的文件添加进去(如果之前有SOF文件,需要先选中文件后按

按钮加以删除)

e.确保Program/Configure下的方框选中

f.单击

开始使用配置文件对FPGA进行配置,Progress栏显示配置进度。

这里方式一是利用JTAG方式,掉电后FPGA中的配置数据将丢失,因为配置文件存储在RAM中,下载速度相对主从AS下载较快。

方式二是利用AS方式,它可以将配置文件写入掉电保持的EPCS中,在上电时使用EPCS对FOGA进行配置。

另外,在选择下载方式前,一定要保持电源关闭,避免出现手指触碰芯片管脚!

9.实验结果与实验现象

实现现象与分析:

Ø数字信号源为4Hz状态下,计数值以这样的频率递增并在八位数码管显示0,1,2,3,4,5,6,7,8,9,A,B,C,D,F,1,2………..,每当递增至F值时,LED3灯亮,表示由进位输出。

Ø将SW1上拨到0处,显示当前值,停止计数

Ø按下核心板上RST,计数值清零,显示为0

ØRTL级图

ØTechnologyMapViewerPreprocess

三、实验心得与注意事项

1)本实现关键部分是cnt4b.v文件的设计,下面图形是笔者在做cnt4b.v文件综合编译后得到的带异步复位的4位加法计数器RTL图

现在结合计数模块的源程序加以说明:

图中间的四位锁存器,rst是异步清零信号,低电平有效;clk为时钟脉冲信号,是计数加的频率给定。

ena是计数使能信号,当为高电平的时候锁存信号。

需要说明的是:

程序计数模块中always如何产生锁存器?

always@(posedgeclkornegedgerst)

begin

if(rst==1'b0)//异步清零,低电平有效

cnt<=4'h0;

elseif(ena==1'b1)//同步使能计数,高电平有效

cnt<=cnt+1'b1;

end

仔细阅读上述代码既可以发现如下问题:

Always块,elseif语句保证了ena==1'b1(高电平)时,执行计数功能。

而没有写出ena==1'b0时的结果,那么其实,如果在给定的条件下变量没有赋值,这个变量将保持原值,也就是会说生成一个锁存器,这里的话就是当将ena==0时,cnt值保持不变,不会根据时钟信号累加!

2)

数字信号源:

能产生0.5Hz~100MHz多组数字信号源,分CLOCK0~CLOCK3四组信号输出,通过短路帽跳线分别可选择不同的时钟信号输入到FPGA,CLOCK0~CLOCK3对应的排针左边为不同频率的数字信号,排针右边是连到一起的,所以每组信号源只能插一个短路帽,否则可能会损坏芯片。

使用时要将数字信号源的电源开关JP11的短路帽跳到ON位置。

FPGA编程:

通过JTAG接口下载FPGA程序时,最好将下载器插在主板上的JTAG接口,不要插在核心板的JTAG接口上,以防插反;如果使用AS接口下载程序时,一定要断电后才能把下载器插到AS接口,确保不插反才能上电。

下载线接插最好按照以下流程:

先将10Pin的仿真下载线(连着下载器)插到FPGA的JTAG或AS接口,然后再将下载器另一端的USB线插到电脑上。

其他注意事项,见计数文档红色字体处!

附录1计数模块

modulecnt4b(clk,rst,ena,dout,cout);//模块名cnt4b

inputclk,rst,ena;//输入信号

output[3:

0]dout;//计数输出

outputcout;//进位输出

reg[3:

0]cnt;//计数器

assigncout=&cnt;//进位输出&

assigndout=cnt;//计数器输出

always@(posedgeclkornegedgerst)

begin

if(rst==1'b0)//异步清零,低电平有效

cnt<=4'h0;

elseif(ena==1'b1)//同步使能计数,高电平有效

cnt<=cnt+1'b1;

end

endmodule

●模块名一定要与所建立的文件名相一致,否则会出现编译异常!

●assign模块以及always模块之间的并行执行的关系,时序上同步!

但always模块内部由顺利执行的关系!

这也是FPGA不同与C语言的很重要的一点!

●assigncout=&cnt;对于这条语句中,用到了缩减运算符&,它是对单个操作数进行与递推运算,最后的运算结果是一位的二进制数。

笔者理解为

assigncout=&cnt相当于assigncout=((cnt[0]&cnt[1])&cnt[2])&cnt[3],这样就保证了当计数值加1到F(全1),出现进位信号高电平。

●reg[3:

0]cnt;寄存器变量只有在always块或者是initial块中能够使用,always块在仿真过程中不断重复执行,至于能否执行里面的代码取决于后面的敏感变量表的参量clk或者是rst是否发生变化

附录2

moduledecl7s(d,seg);//模块名decl7s

input[3:

0]d;//输入4位二进制码

output[7:

0]seg;//七段译码输出

reg[7:

0]seg_r;//定义数码管输出寄存器

assignseg=seg_r;//输出数码管译码结果

always@(d)

begin

case(d)//七段译码

4'h0:

seg_r=8'hc0;//显示0

4'h1:

seg_r=8'hf9;//显示1

4'h2:

seg_r=8'ha4;//显示2

4'h3:

seg_r=8'hb0;//显示3

4'h4:

seg_r=8'h99;//显示4

4'h5:

seg_r=8'h92;//显示5

4'h6:

seg_r=8'h82;//显示6

4'h7:

seg_r=8'hf8;//显示7

4'h8:

seg_r=8'h80;//显示8

4'h9:

seg_r=8'h90;//显示9

4'ha:

seg_r=8'h88;//显示a

4'hb:

seg_r=8'h83;//显示b

4'hc:

seg_r=8'hc6;//显示c

4'hd:

seg_r=8'ha1;//显示d

4'he:

seg_r=8'h86;//

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 如何 使用 QuartusII70

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx