Synopsys Design Compiler使用.docx

Synopsys Design Compiler使用.docx

- 文档编号:5800508

- 上传时间:2023-01-01

- 格式:DOCX

- 页数:9

- 大小:332.39KB

Synopsys Design Compiler使用.docx

《Synopsys Design Compiler使用.docx》由会员分享,可在线阅读,更多相关《Synopsys Design Compiler使用.docx(9页珍藏版)》请在冰豆网上搜索。

SynopsysDesignCompiler使用

SynopsysDesignCompiler使用

一、 介绍:

美国Synopsys公司发布的“DesignCompiler”软件,简称“DC”,是一种逻辑合成工具。

通过改进电路延迟时间的计算方法,缩小了逻辑合成时的时序与布局完成后的最终时序之间的偏差。

DC得到全球60多个半导体厂商、380多个工艺库的支持。

据最新Dataquest的统计,Synopsys的逻辑综合工具占据91%的市场份额。

DC是十二年来工业界标准的逻辑综合工具,也是Synopsys最核心的产品。

它使IC设计者在最短的时间内最佳的利用硅片完成设计。

它根据设计描述和约束条件并针对特定的工艺库自动综合出一个优化的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提高设计性能。

二、 要求:

由于实训没有硬性要求VHDL文件,本人挑选了已经预先做好的洗衣机时控电路,利用SynopsysDesignCompiler工具,进行优化分析,通过这一过程熟悉软件的使用。

三、 过程:

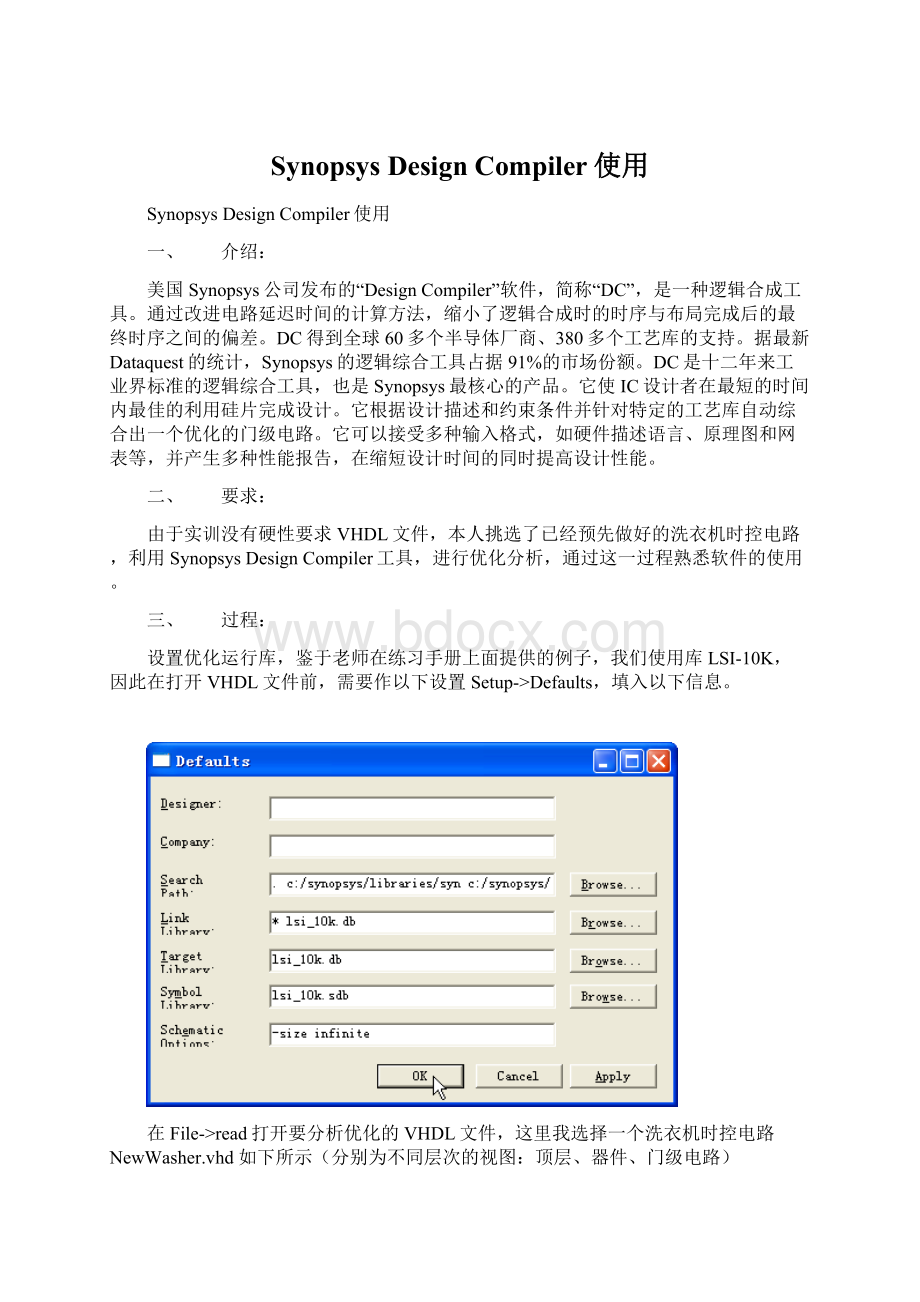

设置优化运行库,鉴于老师在练习手册上面提供的例子,我们使用库LSI-10K,因此在打开VHDL文件前,需要作以下设置Setup->Defaults,填入以下信息。

在File->read打开要分析优化的VHDL文件,这里我选择一个洗衣机时控电路NewWasher.vhd如下所示(分别为不同层次的视图:

顶层、器件、门级电路)

在Tools->DesignOptimization中设置好兼顾平衡的约束条件(左图),确定编译后,产生了右边经过优化的门级电路图。

接下来,把优化过的图形转换为VHDL文件和DB文件输出,另存到指定位置File->SaveAs

如右图,生成了新的DB文件和vhd文件。

接下来,是要设定CLK的周期,根据分析、优化、编译出来的SlackTime松弛数值和Area面积数值,选取最合适的平衡点。

首先,在门级电路中选中“CLK”(由于电路视图比较小,组合使用Ctrl+”+”来放大更方便),在Attributes->Clocks->Specify,设定周期为15ns,

然后,来到Tools->DesignOptimization,编译时,Map仍然选择Medium,点击“OK”。

这时,正当编译完成显示信息的时候,屏幕一闪,程序突然自动退出了。

头脑中马上想到的是是不是VHDL文件有问题?

数值设置不合理?

操作步骤错误?

等等一连串的问题浮了上来。

针对VHDL文件,我做了修改,并保证了在QuartusII6.0中能够正常仿真后,再来运行DC,结果依旧。

反复,尝试不同的操作步骤、参数设置等等,均告失败。

后来,问同学问老师,还是没办法得到有效的解决方法。

难道就要换别的文件来调试?

终于,在最后一天的命令行操作,给我带来头绪,如果之前的编译能够完成,只是结果没法看到,那么在DC_Shell的命令行模式下呢?

当然,过程没有那么简单,首先老师让我们参考的是“dctutorial.pdf”,里面都是英文的教程,虽说不太习惯看英文,但为了尽快解决问题,还是硬着头皮看下去。

边看边上机操作,先是熟悉List命令,然后是Help命令……一步一步慢慢看,但是始终不到重点,例如打开文件,进行编译等等。

很多时候,我们打开DesignAnalyzer的时候,很少留意后面还附带着两个窗口,其中一个就是SynopsysDesignAnalyzer-CommandWindow,如下图示:

里面显示的是鼠标点击选项时,运行的命令行,何不把它对照记录下来呢?

说干就干,花了一段周折,摸索到主要操作的命令对应如下:

熟悉了命令后,马上打开DC_Shell,如图:

经过多次尝试,DC_Shell可以连续执行已经换好行的命令,就是说可以把表格里面的命令复制粘贴到光标提示符就可以按顺序执行所有命令。

里面显示的是鼠标点击选项时,运行的命令行,何不把它对照记录下来呢?

说干就干,花了一段周折,摸索到主要操作的命令对应如下:

熟悉了命令后,马上打开DC_Shell,如图:

经过多次尝试,DC_Shell可以连续执行已经换好行的命令,就是说可以把表格里面的命令复制粘贴到光标提示符就可以按顺序执行所有命令。

四、 结论:

运行后,OptimizationComplete的提示终于显示出来,

同时还有面积Area的信息:

****************************************

Report:

area

Design:

NewWasher

Version:

2000.05-1

Date :

ThuJan1823:

42:

092007

****************************************

……

……

……

Combinationalarea:

94.000000

Noncombinationalarea:

135.000000

NetInterconnectarea:

undefined (Nowireloadspecified)

Totalcellarea:

229.000000

Totalarea:

undefined

还有松弛时间Slack的信息:

****************************************

Report:

timing

-pathfull

-delaymax

-max_paths1

Design:

NewWasher

Version:

2000.05-1

Date :

ThuJan1823:

44:

532007

****************************************

……

……

……

-----------------------------------------------------------

datarequiredtime 8.40

dataarrivaltime -8.20

-----------------------------------------------------------

slack(MET) 0.20

从上面的信息可以看到,当CLK设定为10ns的时候,Area和Slack的值分别为229、0.20,按照相同的办法,只要在命令中修改Clock的数值,就可以设定不同的周期,进而得到不同的Area值和Slack值,命令格式:

下面是多次修改CLK的周期,记录得

从左边的数据可以看到得到的小的正Slack值为0.00,说明该时控电路最快能够以7ns的周期运行。

因为在实际应用中,总是希望IC芯片运行的速度快,即CLK的值小看;同时,面积占用小,即Area的值也小,所以图表中Area=254,CLK=8时,较为合适,可以认为有效地平衡了二者。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Synopsys Design Compiler使用 Compiler 使用

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx