异步时序逻辑电路.docx

异步时序逻辑电路.docx

- 文档编号:5708678

- 上传时间:2022-12-31

- 格式:DOCX

- 页数:14

- 大小:148.51KB

异步时序逻辑电路.docx

《异步时序逻辑电路.docx》由会员分享,可在线阅读,更多相关《异步时序逻辑电路.docx(14页珍藏版)》请在冰豆网上搜索。

异步时序逻辑电路

第五章异步时序逻辑电路

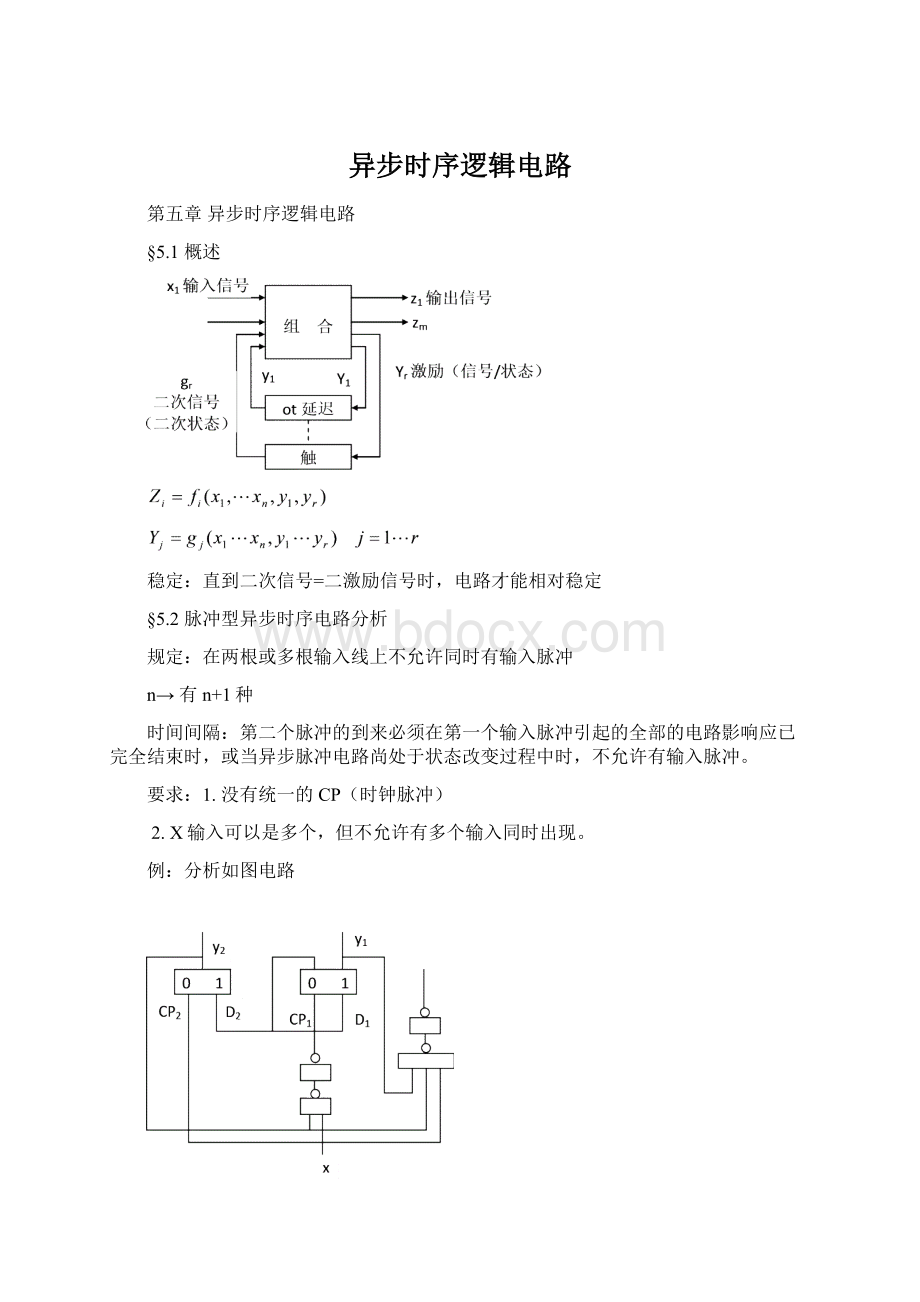

§5.1概述

稳定:

直到二次信号=二激励信号时,电路才能相对稳定

§5.2脉冲型异步时序电路分析

规定:

在两根或多根输入线上不允许同时有输入脉冲

n→有n+1种

时间间隔:

第二个脉冲的到来必须在第一个输入脉冲引起的全部的电路影响应已完全结束时,或当异步脉冲电路尚处于状态改变过程中时,不允许有输入脉冲。

要求:

1.没有统一的CP(时钟脉冲)

2.X输入可以是多个,但不允许有多个输入同时出现。

例:

分析如图电路

1.求控制、输出函数

2.状态、次态真值表

x

y2

y1

CP2

D2

CP1

D1

Z

y2n+1

y1n+1

1

0

0

1

1

00

1

0

1

0

1

0

1

1

0

10

0

0

0

1

1

1

0

1

1

01

1

0

1

1

1

1

1

1

0

11

0

1

0

0

当x=0时,CP1=CP2=0,电路状态不变。

3.状态图、状态表

x

y2y1

1

00

10/0

01

01/0

10

11/0

11

00/1

(y2n+1y0n+1/2)

此电路挂起

例2.分析如图电跃

1.求控制、输出函数

2.状态、次态真值表

y2y1

x3

x2

x1

R2

S2

R1

S1

Z

y2n+1

y1n+1

00

0

0

1

1

0

1

1

0

1

0

0

1

0

1

1

1

1

0

0

0

1

0

0

0

1

1

1

0

0

0

01

0

0

1

1

1

1

1

1

0

1

0

1

0

0

1

0

1

1

0

0

1

0

0

0

1

1

1

1

0

1

10

0

0

1

1

0

0

1

0

1

0

0

1

0

1

1

1

0

0

1

1

1

0

0

0

1

1

1

0

0

0

11

0

0

1

1

1

0

1

0

1

0

0

1

0

0

1

0

1

0

0

0

1

0

0

0

1

1

1

0

0

1

当x3=x2=x1=0时,R2=S2=R1=S1=1不变。

3.状态图、状态表

x

y2y1

x3

x2

x1

R2

00

00

00

10

0

01

01

00

01

1

10

00

11

10

0

11

01

00

10

0

(y2n+1y1n+1)

4.特性描述

x1—x2—x3序列检测器

CP当控制信号

§5.3脉冲异步时序时路设计

例.设计“x1—x2—x2”序列检测器

x

y

x1

x2

A

B/0

A/0

B

B/0

C/0

C

B/0

A/1

2.状态化简

3.状态分配

A—00B—01C—10

二进制状态表

x

Yy2y1

x1

x2

00

01/0

00/0

01

01/0

10/0

10

01/0

00/1

(yn+1/2)

4.用D触发器求控制、输出函数

x2x1

y2y1

00

01

11

10

x2x1

y2y1

00

01

11

10

x2x1

y2y1

00

01

11

10

00

d

d

d

d

00

0

0

d

0

00

d

01

d

d

d

1

01

0

0

d

1

01

d

11

d

d

d

d

11

d

d

d

d

11

d

d

d

d

10

d

0

d

0

10

0

1

d

1

10

d

1

D2=y1

CP2=x2y1+x2y2+x1y2

Z=x2y2

x2x1

y2y1

00

01

11

10

x2x1

y2y1

00

01

11

10

00

d

d

d

d

00

0

1

d

0

01

d

d

d

0

01

0

0

d

1

11

d

d

d

d

11

d

d

d

d

10

d

1

d

d

10

0

1

d

0

D1=x1

CP1=x1y1+x2y1

说明:

(1)当y2,y1=11时,因无此状态,所以均作d处理。

(2)当x2,x1=11时,不存在,因为x1,x2不能同时输入为1,所以11这一列全都作d处理。

(3)当x1,x2为00时,不此起电路变化,所以CP1,CP2的00列填0,不会产生CP,D1,D2的00列填d。

(4)若现态等于次态,即CP上填0,D上填d。

6.讨论

x1=1x2=0,设计不好挂起。

§5.4电平型异步时序电路概述

对于电平型异步时序电路一般形成由门电路带反馈组成的,输入的都是电平信号。

输出函数

激励函数

状态真值表

x1x2y

YZ

000

00

001

00

010

00

011

11

100

11

101

11

110

00

111

11

流程表是以卡诺图的形式反映激励信号,输出信号同输入信号二次信号之间的关系。

x1x2

y

00

01

11

10

x1x2

y

00

01

11

10

x

00

01

11

10

0

0/0

0/0

0/0

1/1

0

0

0

0

1

0

0

0

1

1

0/0

1/1

1/1

1/1

1

0

1

1

0

1

1

1

Y/Z

Y

Z

总态,包括输入和二次状态,可以写成(x-y)(10-0)(00-1)

t0:

(01-0)t1:

(11-0)t2:

(10-0)t2′:

(10-1)

t2′时稳定

规定:

1.电平型异步时序电路对电平输入信号有所限制,不允许两个或多个电平输入信号同时跳变。

2.一根或几根输入线上两次跳变的时间间隔不能太短,只有当第一次跳变在电路中引起的响应完全结束时,才允许第二次跳变。

如何反应流程表中的总态如何反应:

1.输入状态的改变只能引起总态在流程表上作相邻方块的水平移动,二次状态的改变只引起总态在流程表中作垂直方向的移动,仅在到达有圈的方块时电路才能稳定下来,这时才能允许输入状态的改变,即总态在作水平相邻移动。

§5.5电平型异步时序电路分析

分析步骤:

1.求激励函数、输出函数

2.列出流程表,圈定稳定状态

3.根据总态响应序列作出时间图

4.说明电路逻辑功能

例1.分析如图电路

X1x2

y0

00

01

11

10

0

0

0

0

1

1

0

1

1

Y

3.时间图

总态响应序列

时刻:

t0t1t2t3t4t5t6

总态:

01-011-010-011-101-0100-101-0

4.逻辑功能

x1-Dx2-CPZ-Q

t0-t1:

x1=0x2=1Z=0CP无效

t1-t2:

x1=1x2=1Z=0

t2-t3:

x1=1x2=0Z=1-x1

t3-t4:

x1=1x2=0Z=1

t4-t5:

x1=0x2=1Z=1

t5-t5:

x1=0x2=0Z=0-x1

例2

1.求激励、控制函数

2.画流程表

x2x1

y2y1

Y2Y1

Z2Z1

00

00

00

00

00

01

00

10

00

10

10

00

00

11

10

01

01

00

00

00

01

01

01

10

01

10

00

00

01

11

11

01

10

00

10

00

10

01

01

10

10

10

10

00

10

11

11

01

11

00

01

00

11

01

01

10

11

10

11

00

11

11

11

01

X2x1

y2y1

00

01

11

10

00

01

11

10

00

00

00

01

10

00

00

00

00

01

00

01

01

01

10

10

10

10

11

10

11

11

11

01

01

01

01

10

10

00

11

10

00

00

00

00

Y2Y1

Z2Z1

3.时间图

总态响应序列x2x1-y2y1

时刻:

t0t1t2t3t4

总态:

00-0001-0011-0010-0100-01

11-0100-00

t5t6t7t8

10-0011-1001-1100-11

10-1011-1100-10

例3

1.激励函数、控制函数

2.流程表

x2

x1

y1y2

Y1Y2

00

00

11

00

01

11

00

10

11

00

11

11

01

00

10

01

01

01

01

10

10

01

11

01

10

00

11

10

01

11

10

10

11

10

11

11

11

00

10

11

01

01

11

10

10

11

11

10

x1x2

y1y2

00

01

11

10

00

11

10

10

11

01

11

01

01

11

11

11

01

10

11

10

11

10

10

11

3.时间图

总态响应序列

时刻:

t0t1t2t3t4t5t6

总态:

01-1111-0110-0111-1101-1000-10

00-1101-0110-1111-1000-11

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 异步 时序 逻辑电路

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx