数电实验.docx

数电实验.docx

- 文档编号:5348588

- 上传时间:2022-12-15

- 格式:DOCX

- 页数:13

- 大小:16.23KB

数电实验.docx

《数电实验.docx》由会员分享,可在线阅读,更多相关《数电实验.docx(13页珍藏版)》请在冰豆网上搜索。

数电实验

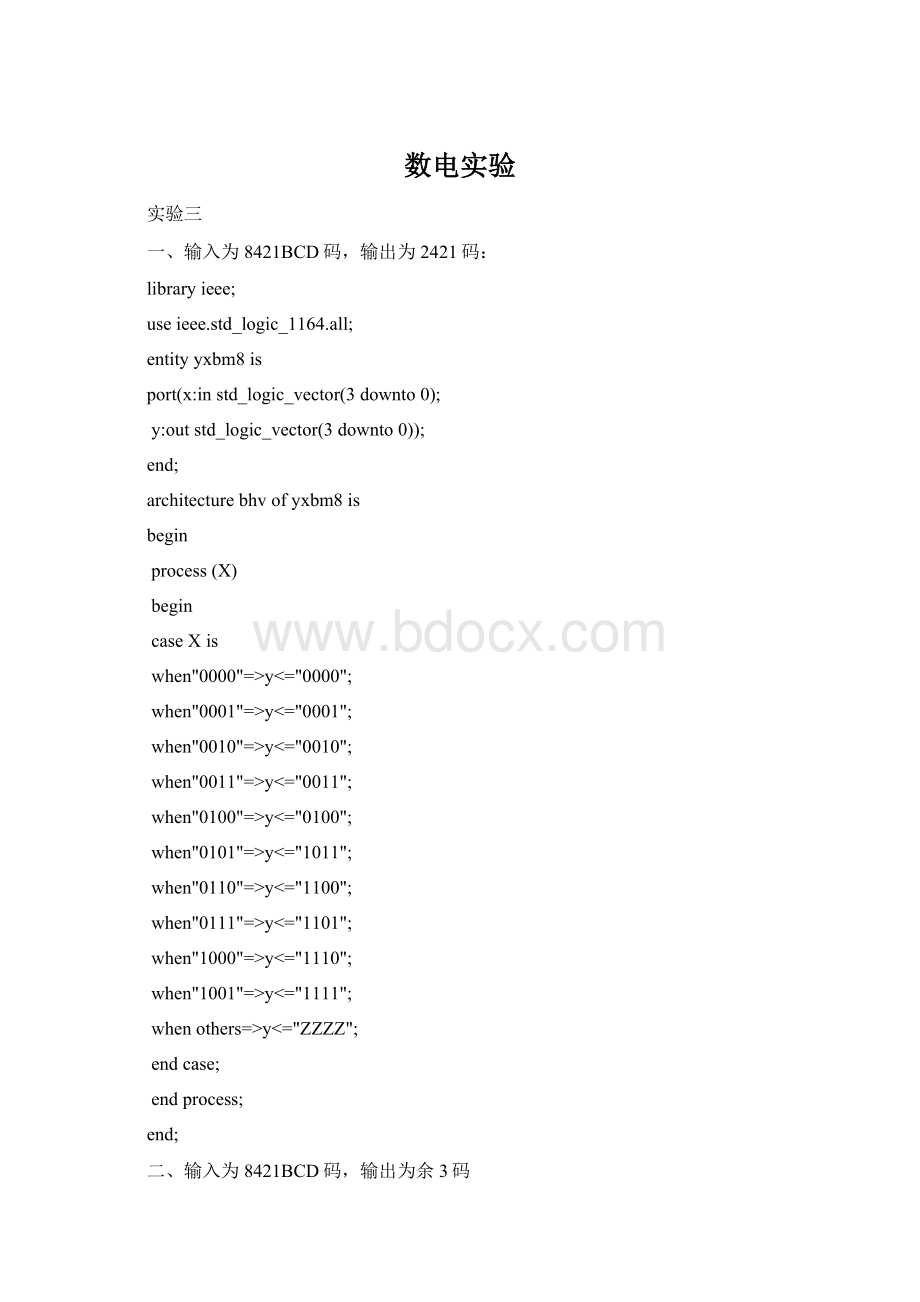

实验三

一、输入为8421BCD码,输出为2421码:

libraryieee;

useieee.std_logic_1164.all;

entityyxbm8is

port(x:

instd_logic_vector(3downto0);

y:

outstd_logic_vector(3downto0));

end;

architecturebhvofyxbm8is

begin

process(X)

begin

caseXis

when"0000"=>y<="0000";

when"0001"=>y<="0001";

when"0010"=>y<="0010";

when"0011"=>y<="0011";

when"0100"=>y<="0100";

when"0101"=>y<="1011";

when"0110"=>y<="1100";

when"0111"=>y<="1101";

when"1000"=>y<="1110";

when"1001"=>y<="1111";

whenothers=>y<="ZZZZ";

endcase;

endprocess;

end;

二、输入为8421BCD码,输出为余3码

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityyxbm9is

port(x:

inintegerrange0to9;

y:

outintegerrange0to12);

end;

architecturebhvofyxbm9is

begin

y<=x+3;

end;

三、设计一个优先编码器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityyxbm10is

port(d:

instd_logic_vector(7downto0);

y:

outstd_logic_vector(3downto0));

end;

architecturebhvofyxbm10is

begin

process(D)

begin

ifd(7)='0'then

y<="0000";

elsifd(6)='0'then

y<="0001";

elsifd(5)='0'then

y<="0010";

elsifd(4)='0'then

y<="0011";

elsifd(3)='0'then

y<="0100";

elsifd

(2)='0'then

y<="0101";

elsifd

(1)='0'then

y<="0110";

elsifd

(1)='1'then

y<="0111";

endif;

endprocess;

end;

实验四:

一、设计一个多数表决电路:

libraryieee;

useieee.std_logic_1164.all;

entityduoshuis

port(x:

instd_logic_vector(3downto0);

y:

outbit);

end;

architecturerhbofduoshuis

begin

process(X)

begin

caseXis

when"0111"=>y<='1';

when"1011"=>y<='1';

when"1101"=>y<='1';

when"1110"=>y<='1';

when"1111"=>y<='1';

whenothers=>y<='0';

endcase;

endprocess;

end;

二、设计二个二位二进制数相乘电路:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitychengfais

port(a,b:

instd_logic_vector(1downto0);

y:

outstd_logic_vector(3downto0));

end;

architecturebhvofchengfais

begin

y<=a*b;

end;

三、设计一个一位全减器电路:

Libraryieee;

Useieee.std_logic_1164.all;

Entityjianis

Port(A,B,Ci:

instd_logic;

F,Co:

outstd_logic);

End;

Architecturebhvofjianis

signalg,h,i,j:

std_logic;

Begin

g<=AxorB;

F<=gxorCi;

h<=notAandB;

i<=notAandCi;

j<=BandCi;

Co<=horiorj;

End;

实验五:

一、译码真值表

Libraryieee;

Useieee.std_logic_1164.all;

Entityqiduanis

Port(a:

instd_logic_vector(3downto0);

y:

outstd_logic_vector(6downto0));

End;

Architecturertlofqiduanis

Begin

Process(A)

Begin

CaseAis

When"0000"=>y<="1111110";

When"0001"=>y<="0110000";

When"0010"=>y<="1101101";

When"0011"=>y<="1111001";

When"0100"=>y<="0110011";

When"0101"=>y<="1011011";

When"0110"=>y<="1011111";

When"0111"=>y<="1110000";

When"1000"=>y<="1111111";

When"1001"=>y<="1111011";

When"1010"=>y<="1110111";

When"1011"=>y<="0011111";

When"1100"=>y<="1001110";

When"1101"=>y<="0111101";

When"1110"=>y<="1001111";

When"1111"=>y<="1000111";

Whenothers=>y<="ZZZZZZZ";

Endcase;

Endprocess;

End;

二、二进制数相乘的数码管显示

Libraryieee;

Useieee.std_logic_1164.all;

Entityshumaguanis

Port(a,b:

instd_logic_vector(1downto0);

y:

outstd_logic_vector(6downto0));

End;

Architecturertlofshumaguanis

Begin

Process(a,b)

Variablex:

std_logic_vector(3downto0);

Begin

x:

=a&b;

CaseXis

When"0000"=>y<="1111110";

When"0001"=>y<="1111110";

When"0010"=>y<="1111110";

When"0011"=>y<="1111110";

When"0100"=>y<="1111110";

When"0101"=>y<="0110000";

When"0110"=>y<="1101101";

When"0111"=>y<="1111001";

When"1000"=>y<="1111110";

When"1001"=>y<="1101101";

When"1010"=>y<="0110011";

When"1011"=>y<="1011111";

When"1100"=>y<="1111110";

When"1101"=>y<="1111001";

When"1110"=>y<="1011111";

When"1111"=>y<="1111011";

Whenothers=>y<="ZZZZZZZ";

Endcase;

Endprocess;

End;

实验六

一、RS触发器

Libraryieee;

Useieee.std_logic_1164.all;

Entityrsff1is

Port(r,s,cp:

inbit;

q,qb:

bufferbit);

End;

Architecturertlofrsff1is

Begin

qb<=(rnandcp)nandq;

q<=(snandcp)nandqb;

End;

二、JK触发器

Libraryieee;

Useieee.std_logic_1164.all;

Entityjkff1is

Port(j,k,clk,PRN,CLRN:

instd_logic;

q,qb:

outstd_logic);

End;

Architecturertlofjkff1is

signalq_temp,qb_temp:

std_logic;

Begin

Process(clk,PRN,CLRN)

Begin

if((PRNandCLRN)='0')then

q_temp<=notPRN;

qb_temp<=PRN;

elsif(clk'eventandclk='1')then

q_temp<=(jand(notq_temp))or(notkandq_temp);

qb_temp<=notq_temp;

endif;

endprocess;

q<=q_temp;

qb<=qb_temp;

End;

三、D触发器

Libraryieee;

Useieee.std_logic_1164.all;

Entitydff1is

Port(d,clk,PRN,CLRN:

instd_logic;

q,qb:

outstd_logic);

End;

Architecturertlofdff1is

signalq_temp,qb_temp:

std_logic;

Begin

Process(clk,PRN,CLRN)

Begin

if((PRNandCLRN)='0')then

q_temp<=notPRN;

qb_temp<=PRN;

elsif(clk'eventandclk='1')then

q_temp<=d;

qb_temp<=notq_temp;

else

q_temp<=q_temp;

endif;

endprocess;

q<=q_temp;

qb<=qb_temp;

End;

四、开关控制电路设计

Libraryieee;

Useieee.std_logic_1164.all;

Entitykaiguanis

Port(A,B,C:

instd_logic;

F:

outstd_logic);

End;

Architecturertlofkaiguanis

signalD,f0:

std_logic;

Begin

D<=AorBorC;

Process(D)

Begin

if(D'eventandD='1')then

f0<=notf0;

endif;

Endprocess;

F<=f0;

End;

实验七:

一、设计一位四位带异步清零的并入串出移位寄存器

没有

二、环形计数器

libraryIEEE;

useIEEE.std_logic_1164.all;

entityhuanxingis

port(

clk:

instd_logic;

load:

instd_logic;

d:

instd_logic_vector(3downto0);

q:

outstd_logic_vector(3downto0));

end;

architectureshft_reg_archofhuanxingis

signalTEMP:

std_logic_vector(3downto0);

begin

西安邮电学院可编程逻辑实验报告

process(clk)

begin

ifclk'eventandclk='1'then

ifload='1'then

TEMP<=d;

elsifTEMP="1000"then

TEMP<=TEMP(0)&TEMP(3downto1);

elsifTEMP="0100"then

TEMP<=TEMP(0)&TEMP(3downto1);

elsifTEMP="0010"then

TEMP<=TEMP(0)&TEMP(3downto1);

elsifTEMP="0001"then

TEMP<=TEMP(0)&TEMP(3downto1);

elseTEMP<="1000";

endif;

endif;

endprocess;

q<=TEMP;

endarchitecture;

三、8位循环移位寄存器

没有

四、节日彩灯

libraryIEEE;

useIEEE.std_logic_1164.all;

entitycaidengis

port(

clk:

instd_logic;

shift:

instd_logic;

q:

outstd_logic_vector(3downto0));

end;

architectureshft_reg_archofcaidengis

signaltemp:

std_logic_vector(3downto0);

begin

q<=temp;

process(clk)

begin

if(clk'eventandclk='1')then

ifshift='1'then

casetempis

when"0000"=>temp<="1000";

when"1000"=>temp<="1100";

when"1100"=>temp<="1110";

when"1110"=>temp<="1111";

when"1111"=>temp<="0111";

when"0111"=>temp<="0011";

when"0011"=>temp<="0001";

when"0001"=>temp<="0000";

whenothers=>temp<="0000";

endcase;

else

casetempis

when"0000"=>temp<="0001";

when"0001"=>temp<="0011";

when"0011"=>temp<="0111";

when"0111"=>temp<="1111";

when"1111"=>temp<="1110";

when"1110"=>temp<="1100";

when"1100"=>temp<="1000";

when"1000"=>temp<="0000";

whenothers=>temp<="0000";

endcase;

endif;

endif;

endprocess;

endarchitecture

实验八:

一、设计一个同步带清零、带有进位输出端的模二十四计数器

Libraryieee;

Useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

Entitycount24is

Port(clk,clr:

instd_logic;

q0,q1,q2,q3,q4,q5:

outstd_logic);

End;

Architecturertlofcount24is

Signalcount_6:

std_logic_vector(5downto0);

Begin

q0<=count_6(0);

q1<=count_6

(1);

q2<=count_6

(2);

q3<=count_6(3);

q4<=count_6(4);

q5<=count_6(5);

Process(clk)

Begin

if(clk'eventandclk='1')then

ifclr='0'then

count_6<="000000";

elsifcount_6="100011"then

count_6<="000000";

elsifcount_6="001001"then

count_6<="010000";

elsifcount_6="011001"then

count_6<="100000";

else

count_6<=count_6+'1';

endif;

endif;

Endprocess;

end;

二、三、四:

没有

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 实验

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx