电子设计自动化实验报告.docx

电子设计自动化实验报告.docx

- 文档编号:5256899

- 上传时间:2022-12-14

- 格式:DOCX

- 页数:22

- 大小:533.07KB

电子设计自动化实验报告.docx

《电子设计自动化实验报告.docx》由会员分享,可在线阅读,更多相关《电子设计自动化实验报告.docx(22页珍藏版)》请在冰豆网上搜索。

电子设计自动化实验报告

湖南工业大学理学院

实验名称

熟悉QuartusII的图形输入法

实验地点

理学楼210

实验时间

2016.10.16

实验成绩

一、实验目的及任务

掌握QuartusII的使用方法

(1)熟悉图形输入法

(2)理解编译方法

(3)了解定时仿真

二、实验内容与步骤

(1)设计一个二选一数据选择器、全加法器。

(2)根据图形输入法编译和波形仿真。

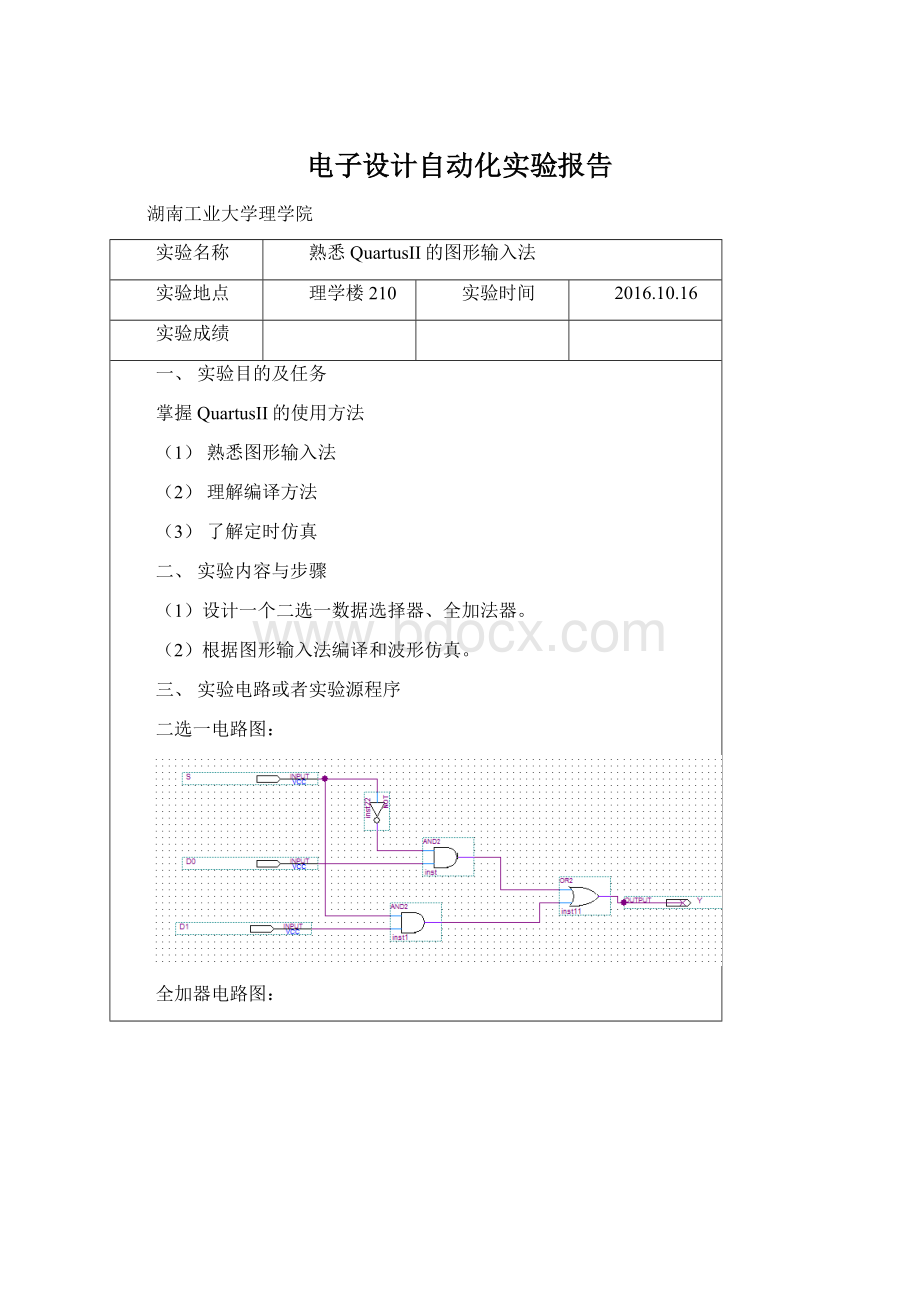

三、实验电路或者实验源程序

二选一电路图:

全加器电路图:

四、实验结果

二选一结果图:

全加器结果图:

实验名称

熟悉QuartusII的VHDL语言描述输入法

实验地点

理学楼210

实验时间

2016.10.23

实验成绩

1、实验目的及任务

(1)VHDL语言描述输入法

(2)理解编译方法

(3)熟悉波形仿真

2、实验内容与步骤

(1)设计一个4位并行奇校验发生器

(2)根据VHDL语言描述输入法编译和波形仿真

三、实验电路或者实验源程序

VHDL程序:

libraryieee;

useieee.std_logic_1164.all;

entityparity_loopis

port(a:

instd_logic_vector(0to2);

b:

instd_logic;

y:

outstd_logic);

endparity_loop;

architectureaofparity_loopis

signals:

std_logic_vector(0to3);

begin

process(a)

begin

s(0)<=b;

foriin0to2loop

s(i+1)<=s(i)xora(i);

endloop;

y<=s(3);

endprocess;

enda;

电路图:

四、实验结果

实验名称

JK触发器的设计

实验地点

理学楼210

实验时间

2016.10.31

实验成绩

一、实验目的及任务

掌握QuartusII的VHDL语言描述输入法

(1)掌握VHDL语言描述输入法

(2)掌握VHDL语言

二、实验内容与步骤

(1)设计一个JK触发器

(2)根据VHDL语言描述输入法编译和波形仿真。

输入

输出

prn

clr

clk

J

K

Q

Qb

0

1

x

x

x

1

0

1

0

x

x

x

0

1

0

0

x

x

x

x

x

1

1

上升沿

0

0

不变

不变

1

1

上升沿

0

1

0

1

1

1

上升沿

1

0

1

0

1

1

上升沿

1

1

翻转

翻转

其中预置端prn复位端clr时钟端clk

三、实验电路或者实验源程序

源程序:

四、实验结果

实验名称

6位双向移位寄存器的设计

实验地点

理学楼210

实验时间

2016.11.03

实验成绩

一、实验目的及任务

掌握QuartusII的VHDL语言描述输入法

(1)掌握VHDL语言描述输入法

(2)掌握VHDL语言

(3)理解if语句进行描述计数器。

(4)设计一个6位双向移位寄存器

2、实验内容与步骤

(1)根据VHDL语言描述输入法编译和波形仿真。

端口说明:

预置数据输入端:

predata

脉冲输入端:

clk

移位寄存器输出端:

dout

工作模式控制端:

M1,M0

左移串行数据输入:

ds1

右移串行数据输入(低位向高位):

dsr

寄存器复位端:

reset

(2)用QuartusII软件编译和波形仿真

(3)工作模式控制表:

M1M0

模式

00

保持

01

右移

10

左移

11

预加载

三、实验电路或者实验源程序

源程序:

4、实验结果

前半段

后半段

实验名称

电子钟的VHDL程序设计

实验地点

理学楼210

实验时间

2016.11.10

实验成绩

一、实验目的及任务

掌握QuartusII的VHDL语言描述输入法

(1)掌握VHDL语言描述输入法

(2)掌握VHDL语言

(3)掌握VHDL语言描述和图形设计的结合

(4)设计一个含时、分、秒的时钟

(5)用QuartusII软件编译和波形仿真

二、实验内容与步骤

(1)设计电子钟的VHDL程序

(2)根据VHDL语言描述输入法编译和波形仿真。

三、实验电路或者实验源程序

源程序:

(1)60进制(分和秒):

(2)十进制VHDL:

(3)六进制VHDL:

(4)24进制(时):

(4)电子时钟顶层文件

四、实验结果

实验名称

七段数码显示译码器设计

实验地点

理学楼210

实验时间

2016.11.24

实验成绩

一、实验目的及任务

(1)掌握使用并行下载程序

(2)掌握数码显示的原理

(3)掌握FPGA开发板的基本结构

(4)设计一个能显示1-9数字的程序,用数码管显示数字

二、实验内容与步骤

(1)设计译码器的VHDL程序(由计数器得到译码器的输入值)

(2)将VHDL程序下载到FPGA芯片中

(3)连接连线,观察数码显示的结果(共阴数码管)

3、实验电路或者实验源程序

源程序:

4、实验结果

实验名称

预置分频器实验

实验地点

理学楼210

实验时间

2016.12.01

实验成绩

一、实验目的及任务

(1)掌握使用并行下载程序

(2)掌握VHDL语言

(3)掌握分频器的设计方法

(4)设计一个预置分频器,用扬声器测试分频结果

(5)掌握if语句

二、实验内容与步骤

(1)根据VHDL语言描述输入法编译和波形仿真

(2)将VHDL程序下载到FPGA芯片中

(3)连接连线,用扬声器听不同分频数的声音

三、实验电路或者实验源程序

源程序:

四、实验结果

实验名称

交通灯控制器实验

实验地点

理学楼210

实验时间

2016.12.12

实验成绩

一、实验目的及任务

(1)掌握使用并行下载程序

(2)掌握VHDL语言

(3)掌握时序逻辑电路的设计方法

(4)设计一个交通灯控制器,用LED显示控制过程

(5)掌握使用process进程

二、实验内容与步骤

(1)根据VHDL语言描述输入法编译和波形仿真

(2)将VHDL程序下载到FPGA芯片中

(3)连接连线,模拟观察交通灯控制的过程

三、实验电路或者实验源程序

(1)顶层模块图:

(2)数码管VHDL:

(3)状态VHDL:

四、实验结果

实验心得

在刚开始学习电子设计自动化那几节课,我感觉这课程挺无聊的,各种型号、各种构造、各种下载方式搞得我眼花缭乱。

在第五章开始学习VHDL编程语法的时候,虽然听得是很仔细,却总是感觉并没有真正了解。

当开始安排实验课程之后,才对这门课程有了更为深刻的认识,这个科目是个更偏向于实践的课程,自我感觉,实验需要赶上理论课程,因为我觉得在实验中,我能更全面的了解整个FPGA工程的构造,就像是面向对象编程的思想,先抽象出一个整体,在把各个方面的东西具体化,进而全面了解整个体统,而不是先把各个整体弄出来,然后再拼装成一个整体。

事实证明,我的想法是对的。

经过第二个实验之后,我觉得我已经了解FPGA有了入门级的了解,并且书上的内容就像是查看数据手册一样,简单易懂。

但是在做实验之前,我只能像背课文一样,把每个知识点牢记于心,这样的效率和效果是极其低的。

所以,自我感觉,偏向实践类的科目不应该只是盲目的把理论课程上好,更应该在上课的同时开展实验,双管齐下,才能更有效果。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 电子设计 自动化 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx