电子科大计算机学院数字逻辑实验报告Verilog组合逻辑设计.docx

电子科大计算机学院数字逻辑实验报告Verilog组合逻辑设计.docx

- 文档编号:5234513

- 上传时间:2022-12-14

- 格式:DOCX

- 页数:24

- 大小:741.05KB

电子科大计算机学院数字逻辑实验报告Verilog组合逻辑设计.docx

《电子科大计算机学院数字逻辑实验报告Verilog组合逻辑设计.docx》由会员分享,可在线阅读,更多相关《电子科大计算机学院数字逻辑实验报告Verilog组合逻辑设计.docx(24页珍藏版)》请在冰豆网上搜索。

电子科大计算机学院数字逻辑实验报告Verilog组合逻辑设计

电子科技大学

实验报告

学生姓名:

郫县阿基王学号:

26指导教师:

唐明

一、实验项目名称:

Verilog组合逻辑设计

二、实验目的:

使用ISE软件和Verilog语言进行组合逻辑的设计与实现。

三、实验内容:

1.3-8译码器的设计和实现。

2.4位并行进位加法器的设计和实现。

3.两输入4位多路选择器的设计和实现。

实验要求如下:

1.采用Verilog语言设计,使用门级方式进行描述。

2.编写仿真测试代码。

3.编写约束文件,使输入、输出信号与开发板的引脚对应。

4.下载到FPGA开发板,拨动输入开关,观察Led灯的显示是否符合真值表。

四、实验原理:

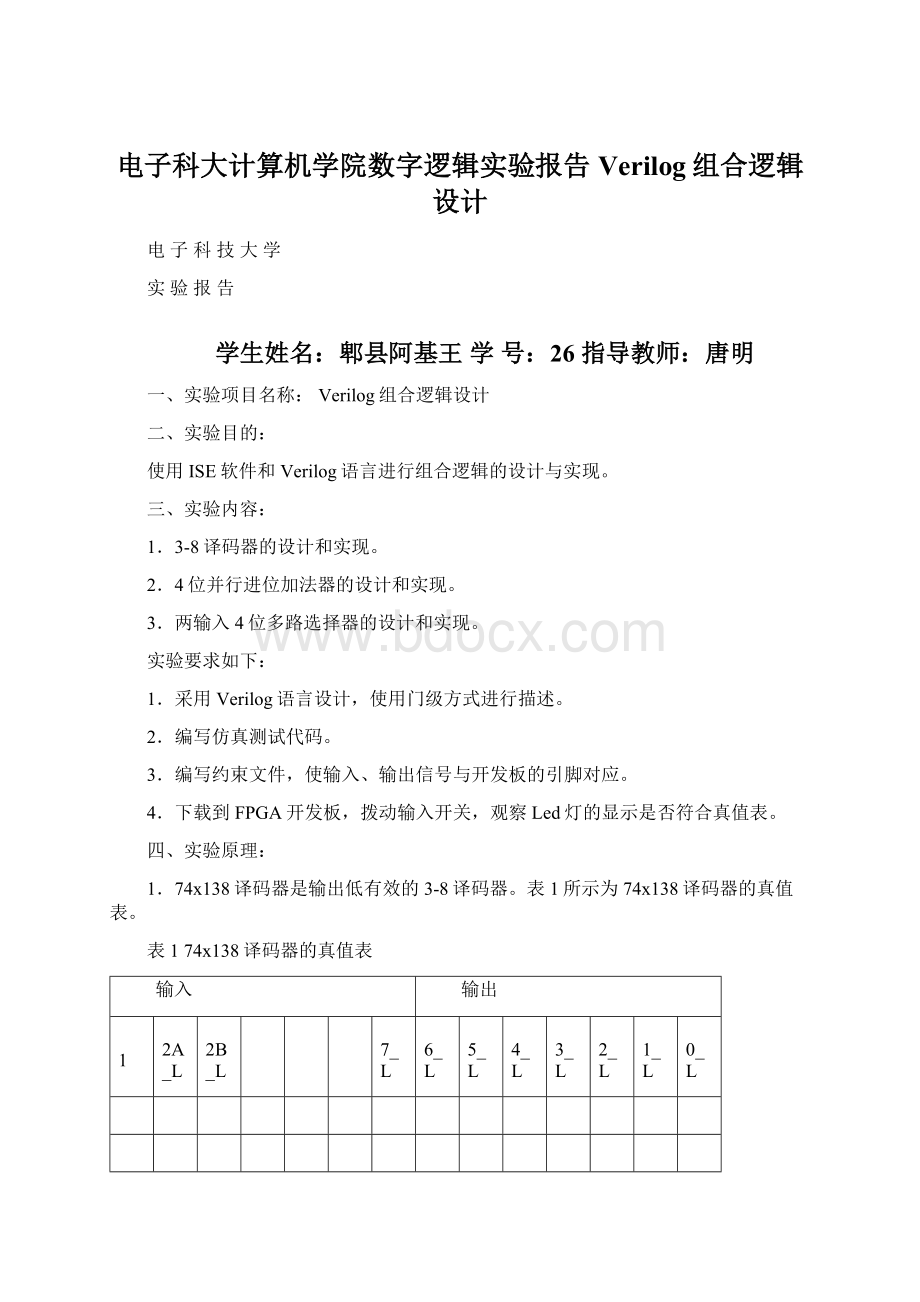

1.74x138译码器是输出低有效的3-8译码器。

表1所示为74x138译码器的真值表。

表174x138译码器的真值表

输入

输出

G1

G2A_L

G2B_L

C

B

A

Y7_L

Y6_L

Y5_L

Y4_L

Y3_L

Y2_L

Y1_L

Y0_L

0

x

x

x

x

x

1

1

1

1

1

1

1

1

x

1

x

x

x

x

1

1

1

1

1

1

1

1

x

x

1

x

x

x

1

1

1

1

1

1

1

1

1

0

0

0

0

0

1

1

1

1

1

1

1

0

1

0

0

0

0

1

1

1

1

1

1

1

0

1

1

0

0

0

1

0

1

1

1

1

1

0

1

1

1

0

0

0

1

1

1

1

1

1

0

1

1

1

1

0

0

1

0

0

1

1

1

0

1

1

1

1

1

0

0

1

0

1

1

1

0

1

1

1

1

1

1

0

0

1

1

0

1

0

1

1

1

1

1

1

1

0

0

1

1

1

0

1

1

1

1

1

1

1

根据3-8译码器的真值表,可得输出的函数表达式为

根据上述函数表达式,可画出逻辑电路图为。

图13-8译码器的逻辑电路图

2.数据选择器的逻辑功能是根据地址选择端的控制,从多路输入数据中选择一路数据输出。

因此,它可实现时分多路传输电路中发送端电子开关的功能,故又称为复用器(Multiplexer),并用MUX来表示。

表22输入1位多路选择器的真值表

数据输入

选择控制S

输出Y

D0

D1

0

0

0

0

0

1

0

0

1

0

0

1

1

1

0

1

0

0

1

0

0

1

1

1

1

0

1

0

1

1

1

1

2选1数据选择器的真值表如表1所示,其中,D0、D1是2路数据输入,S为选择控制端,Y为数据选择器的输出,根据真值表可写出它的输出函数表达式为:

如果输入再加上低有效的输入使能端,则输出的表达式变为

根据上述函数表达式,可画出2输入4位多路选择器的逻辑电路图为。

图22输入4位多路选择器的逻辑电路图

2.1位全加器的真值表如下

表31位全加器的真值表

输入变量

输出变量

A

B

Ci

Ci+1

S

0

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

1

0

1

0

0

0

1

1

0

1

1

0

1

1

0

1

0

1

1

1

1

1

0

1

1

1

0

根据真值表,输出表达式为:

对于4位并行加法器,可以按入下公式进行设计

图3所示为4位并行进位加法器框图,本实验中用Verilog语句来描述。

图34位并行进位加法器

五、实验器材(设备、元器件):

PC机、WindowsXP、Anvyl或Nexys3开发板、XilinxISE14.7开发工具、DigilentAdept下载工具。

六、实验步骤:

实验步骤包括:

建立新工程、原理图或代码输入、设计仿真、输入输出引脚设置、生成流代码与下载调试。

七、关键源代码:

1.在ISE设计中可以直接输入如下3-8译码器的代码

moduledecoder_74x138(

G1,G2A_L,G2B_L,

C,B,A,

Y7_L,Y6_L,Y5_L,Y4_L,Y3_L,Y2_L,Y1_L,Y0_L);

inputG1,G2A_L,G2B_L;

inputC,B,A;

outputY7_L,Y6_L,Y5_L,Y4_L,Y3_L,Y2_L,Y1_L,Y0_L;

wireG1_L;

wireG;

wireA_L,B_L,C_L;

wireA_H,B_H,C_H;

not(G1_L,G1);

nor(G,G1_L,G2A_L,G2B_L);

not(A_L,A);

not(B_L,B);

not(C_L,C);

not(A_H,A_L);

not(B_H,B_L);

not(C_H,C_L);

nand(Y0_L,C_L,B_L,A_L,G);

nand(Y1_L,C_L,B_L,A_H,G);

nand(Y2_L,C_L,B_H,A_L,G);

nand(Y3_L,C_L,B_H,A_H,G);

nand(Y4_L,C_H,B_L,A_L,G);

nand(Y5_L,C_H,B_L,A_H,G);

nand(Y6_L,C_H,B_H,A_L,G);

nand(Y7_L,C_H,B_H,A_H,G);

endmodule

2.3-8译码器的仿真测试代码

//Addstimulushere

G1=0;

G2A_L=1'bx;

G2B_L=1'bx;

C=1'bx;

B=1'bx;

A=1'bx;

#100;

G1=1'bx;

G2A_L=1;

G2B_L=1'bx;

C=1'bx;

B=1'bx;

A=1'bx;

#100;

G1=1'bx;

G2A_L=1'bx;

G2B_L=1;

C=1'bx;

B=1'bx;

A=1'bx;

#100;

G1=1;

G2A_L=0;

G2B_L=0;

C=0;

B=0;

A=0;

#100;

G1=1;

G2A_L=0;

G2B_L=0;

C=0;

B=0;

A=1;

#100;

G1=1;

G2A_L=0;

G2B_L=0;

C=0;

B=1;

A=0;

#100;

G1=1;

G2A_L=0;

G2B_L=0;

C=0;

B=1;

A=1;

#100;

G1=1;

G2A_L=0;

G2B_L=0;

C=1;

B=0;

A=0;

#100;

G1=1;

G2A_L=0;

G2B_L=0;

C=1;

B=0;

A=1;

#100;

G1=1;

G2A_L=0;

G2B_L=0;

C=1;

B=1;

A=0;

#100;

G1=1;

G2A_L=0;

G2B_L=0;

C=1;

B=1;

A=1;

仿真结果如下图所示。

图4译码器的仿真结果

3.译码器在Nexys3开发板上的约束文件

#Switch

NETALOC=T10;

NETBLOC=T9;

NETCLOC=V9;

NETG2B_LLOC=M8;

NETG2A_LLOC=N8;

NETG1LOC=U8;

#Led

NETY0_LLOC=U16;

NETY1_LLOC=V16;

NETY2_LLOC=U15;

NETY3_LLOC=V15;

NETY4_LLOC=M11;

NETY5_LLOC=N11;

NETY6_LLOC=R11;

NETY7_LLOC=T11;

4.4位并行加法器的代码

moduleAdder_4Bit(A3,A2,A1,A0,

B3,B2,B1,B0,

C0,

C4,S3,S2,S1,S0);

InputA3,A2,A1,A0;

inputB3,B2,B1,B0;

inputC0;

outputC4,S3,S2,S1,S0;

wireg3_L,p3_L,g2_L,p2_L,g1_L,p1_L,go_L,p0_L;

wirec0_L;

wirew1,w2,w3,w4,w5,w6,w7,w8,w9,w10,w11,w12,w13,w14;

wirehs3,c3,hs2,c2,hs1,c1,hs0,c0;

nand(g3_L,A3,B3);

nor(p3_L,A3,B3);

nand(g2_L,A2,B2);

nor(p2_L,A2,B2);

nand(g1_L,A1,B1);

nor(p1_L,A1,B1);

nand(g0_L,A0,B0);

nor(p0_L,A0,B0);

not(c0_L,C0);

not(w1,p3_L);

nand(w2,p2_L,g3_L);

nand(w3,p1_L,g3_L,g2_L);

nand(w4,p0_L,g3_L,g2_L,g1_L);

nand(w5,g3_L,g2_L,g1_L,g0_L,c0_L);

and(C4,w1,w2,w3,w4,w5);

and(hs3,g3_L,~p3_L);

not(w6,p2_L);

nand(w7,p1_L,g2_L);

nand(w8,p0_L,g2_L,g1_L);

nand(w9,g2_L,g1_L,g0_L,c0_L);

and(c3,w6,w7,w8,w9);

xor(S3,hs3,c3);

and(hs2,g2_L,~p2_L);

not(w10,p1_L);

nand(w11,p0_L,g1_L);

nand(w12,g1_L,g0_L,c0_L);

and(c2,w10,w11,w12);

xor(S2,hs2,c2);

and(hs1,g1_L,~p1_L);

not(w13,p0_L);

nand(w14,g0_L,c0_L);

and(c1,w13,w14);

xor(S1,hs1,c1);

and(hs0,g0_L,~p0_L);

not(c0,c0_L);

xor(S0,hs0,c0);

endmodule

5.加法器的仿真测试代码

#100;

C0=1;

#100;

C0=0;

B3=1;

B2=1;

B1=1;

B0=1;

#100;

A3=1;

A2=1;

A1=1;

A0=1;

#100;

C0=1;

仿真结果如下图所示

图5加法器的仿真结果

6.加法器在Nexys3开发板上的约束文件

#Switch

NETB0LOC=T10;#SW0

NETB1LOC=T9;#SW1

NETB2LOC=V9;#SW2

NETB3LOC=M8;#SW3

NETA0LOC=N8;#SW4

NETA1LOC=U8;#SW5

NETA2LOC=V8;#SW6

NETA3LOC=T5;#SW7

#Led

NETS0LOC=U16;#LD0

NETS1LOC=V16;#LD1

NETS2LOC=U15;#LD2

NETS3LOC=V15;#LD3

NETC4LOC=M11;#LD4

#Button

NetC0Loc=B8;#BTN0

7.数据选择器的代码

modulemux_2in4bit(

inputEN_L,S,

input[4:

1]D0,D1,

output[4:

1]Y

);

wirew0,w1,w2,w3,w4,w5,w6,w7,w8,w9;

wireS_L;

not(S_L,S);

nor(w0,EN_L,S);

nor(w1,EN_L,S_L);

and(w2,D0[1],w0);

and(w3,D1[1],w1);

and(w4,D0[2],w0);

and(w5,D1[2],w1);

and(w6,D0[3],w0);

and(w7,D1[3],w1);

and(w8,D0[4],w0);

and(w9,D1[4],w1);

or(Y[1],w2,w3);

or(Y[2],w4,w5);

or(Y[3],w6,w7);

or(Y[4],w8,w9);

endmodule

8.数据选择器的仿真测试代码

//Addstimulushere

EN_L=1;

S=1'bx;

#100;

EN_L=0;

S=0;

D0=4'b0101;

#100;

EN_L=0;

S=1;

D1=4'b1010;

仿真结果如下图所示。

图6数据选择器的仿真结果

9.数据选择器在Nexys3开发板上的约束文件

#Switch

NETD0[1]LOC=T10;#SW0

NETD0[2]LOC=T9;#SW1

NETD0[3]LOC=V9;#SW2

NETD0[4]LOC=M8;#SW3

NETD1[1]LOC=N8;#SW4

NETD1[2]LOC=U8;#SW5

NETD1[3]LOC=V8;#SW6

NETD1[4]LOC=T5;#SW7

#Led

NETY[1]LOC=U16;#LED0

NETY[2]LOC=V16;#LED1

NETY[3]LOC=U15;#LED2

NETY[4]LOC=V15;#LED3

#Button

NetSLoc=B8;#BTN0

NetEN_LLoc=C4;#BTNL

八、实验结论:

1、3-8译码器输入0:

2、3-8译码器输入1:

3、3-8译码器输入4:

4、4位并行进位加法器实现1+1:

5、4位并行进位加法器实现4+4:

6、4位并行进位加法器实现7+8:

7、两输入4位多路选择器实现选择线路1输入1011:

8、两输入4位多路选择器实现选择线路2输入0110:

九、总结及心得体会:

通过本次实验,我对VerilogHDL语言有了更加深刻的理解:

在使用各种门级电路时要注意输入和输出的位置;在电路板上实现功能时,约束文件所起的重要作用,如果缺少约束文件,我们将不知道每一个开关所对应的功能。

同时,通过实验,我认识到了任何的小问题都将会影响我们最终的输出结果,所以也培养了我的细心、仔细和耐心,有助于我养成锱铢必较的好习惯。

十、对本实验过程及方法、手段的改进建议:

1、最终实验结果只能以自己拍照的方式呈现,不够方便;

2、对于两输入4位多路选择器实验的开关不足,要实现线路选择时,必须长按另一开关,对于输出实验结果造成麻烦。

报告评分:

指导教师签字:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 电子科 计算机 学院 数字 逻辑 实验 报告 Verilog 组合 逻辑设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx